This is a repository copy of Enhancement-mode metal-insulator-semiconductor GaN/AllnN/GaN heterostructure field-effect transistors on Si with a threshold voltage of +3.0V and blocking voltage above 1000V.

White Rose Research Online URL for this paper: http://eprints.whiterose.ac.uk/98678/

Version: Accepted Version

### Article:

Lee, K.B., Guiney, I., Jiang, S. et al. (7 more authors) (2015) Enhancement-mode metal-insulator-semiconductor GaN/AlInN/GaN heterostructure field-effect transistors on Si with a threshold voltage of +3.0V and blocking voltage above 1000V. Applied Physics Express, 8 (3). 036502. ISSN 1882-0778

https://doi.org/10.7567/APEX.8.036502

#### Reuse

Unless indicated otherwise, fulltext items are protected by copyright with all rights reserved. The copyright exception in section 29 of the Copyright, Designs and Patents Act 1988 allows the making of a single copy solely for the purpose of non-commercial research or private study within the limits of fair dealing. The publisher or other rights-holder may allow further reproduction and re-use of this version - refer to the White Rose Research Online record for this item. Where records identify the publisher as the copyright holder, users can verify any specific terms of use on the publisher's website.

### **Takedown**

If you consider content in White Rose Research Online to be in breach of UK law, please notify us by emailing eprints@whiterose.ac.uk including the URL of the record and the reason for the withdrawal request.

**Enhancement-mode**

Metal-insulator-semiconductor

GaN/AlInN/GaN Heterostructure Field Effect Transistors on Si

with a Threshold Voltage of +3.0V and Blocking Voltage Above

**1000V**

Kean B. Lee<sup>1</sup>, Ivor Guiney<sup>2</sup>, Sheng Jiang<sup>1</sup>, Zaffar H. Zaidi<sup>1</sup>, Hongtu Qian<sup>1</sup>, David J. Wallis<sup>2</sup>,

Michael J. Uren<sup>3</sup>, Martin Kuball<sup>3</sup>, Colin J. Humphreys<sup>2</sup>, and Peter A. Houston<sup>1</sup>

<sup>1</sup>Department of Electronic and Electrical Engineering, University of Sheffield, Mappin Street,

Sheffield S1 3JD, United Kingdom

<sup>2</sup>Department of Material Science and Metallurgy, University of Cambridge, 27 Charles

Babbage Road, Cambridge CB3 0FS, United Kingdom

<sup>3</sup>H.H. Wills Physics Laboratory, Tyndall Avenue, Bristol BS8 1TL, United Kingdom

Email: kboon.lee@sheffield.ac.uk

Enhancement-mode AlInN/GaN metal-insulator-semiconductor heterostructure field effect

transistors on silicon substrates are reported. The fabricated devices exhibit a threshold

voltage of +3V using a fluorine-based plasma treatment technique and gate dielectric. A drain

current density of 295mA/mm at a gate bias of +10V is measured. An excellent off-state

blocking voltage capability of 630V at leakage current of 1µA/mm and more than 1000V at

10µA/mm is achieved on a device with 20µm gate-drain separation at gate bias of 0V. The

dynamic on-resistance is ~2.2 times the DC on-resistance when pulsing from off-state drain

bias of 500V.

1

GaN-based heterostructure field effect transistors (HFETs), particularly AlGaN/GaN, have attracted much attention due to their potential to replace 600 to 1200V silicon-based power switching devices. Indeed, high-power and high-efficiency AlGaN/GaN power switches that exceed the performance of silicon devices have been demonstrated recently. However, AlGaN/GaN devices often suffer from high electric field reliability issues such as the formation of leakage paths through the AlGaN barrier. On the other hand, AlInN has emerged as a promising alternative to AlGaN as a barrier layer, capable of delivering high output current density and low on-resistance owing to its strong spontaneous polarization. In addition, the AlInN alloy can be lattice-matched to GaN, which results in a strain-free barrier layer and potentially offers advantages over AlGaN/GaN in term of reliability. Several groups have reported enhancement-mode AlInN/GaN devices, but these devices exhibit a relatively low threshold voltages, V<sub>TH</sub> (<+2V), and off-state blocking voltage (<350V).

In this letter, we demonstrate enhancement mode metal-insulator-semiconductor AlInN/GaN HFETs (MISHFETs) on silicon substrates using a fluorine-plasma treatment technique.  $^{14)}$  V<sub>TH</sub> as high as +3.0V and output current of 295mA/mm at a gate bias of +10V are measured. A device with 20µm gate-drain separation shows an off-state blocking voltage (BV) of 630V and >1000V with a leakage current at 1µA/mm and 10µA/mm, respectively.

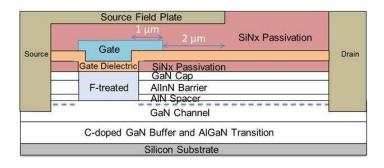

Fig. 1 depicts the device structure of the AlInN/GaN HFETs. The structure was grown by metal-organic vapour phase epitaxy on a 6-inch diameter silicon substrate. After a 250nm AlN nucleation layer, a total of 7μm thick compositionally graded Al<sub>x</sub>Ga<sub>1-x</sub>N transition layer and carbon-doped GaN buffer layer were grown. Subsequently, a 250nm unintentionally doped (UID) GaN channel layer and a 2nm AlN spacer layer were grown, prior to the 11nm thick Al<sub>0.84</sub>In<sub>0.16</sub>N barrier layer. Finally, the structure was capped with 2nm of GaN. The 6-

inch GaN-on-Si wafer shows a bow of ~30 $\mu$ m (concave). The X-ray diffraction rocking curve full width half maximum for (002) and (102) reflections were 520 and 940arcsec, respectively. A root mean square surface roughness of 0.73nm was measured using atomic force microscopy in a  $5x5\mu m^2$  scan area. A 2-dimensional electron gas (2DEG) density of  $8.2x10^{12}$ cm<sup>-2</sup> and an electron mobility of 1240cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> were measured using the Hall technique.

For device fabrication, mesa isolation was performed using inductively coupled plasma etching with a  $Cl_2$ -based plasma. A Ti/Al/Ni/Au (20/120/20/45nm) metal stack was thermally evaporated and annealed at 830°C under  $N_2$  ambient to form the source and drain ohmic contacts. A 100nm  $SiN_x$  passivation layer was deposited using plasma enhanced chemical vapour deposition (PECVD) and a 1.5 $\mu$ m gate window was opened by etching through the  $SiN_x$  layer using reactive ion etching (RIE). A  $CHF_3$  plasma-treatment (RF power of 100W) in an RIE system was performed on the gate window to implant the fluorine and shift  $V_{TH}$  from negative to positive. A 20nm PECVD  $SiN_x$  layer was then deposited to serve as gate insulator prior to T-shape Ni/Au (20/180nm) gate metal deposition. A further 250nm  $SiN_x$  was deposited before the source-connected field plate and probe pad metal deposition. The devices have a 100 $\mu$ m gate width, gate-source separation of 2.5 $\mu$ m and gate-drain separation ( $L_{GD}$ ) varying between 7 and 20 $\mu$ m.

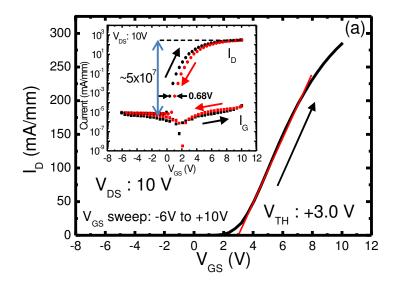

Fig. 2(a) illustrates the gate transfer characteristics of the AlInN/GaN MISHFETs  $V_{TH}$  of ~+3.0V was linear extracted from the gate transfer characteristics. To our knowledge, this is the highest  $V_{TH}$  reported in enhancement-mode AlInN/GaN MISHFETs. The high  $V_{TH}$  is achieved by the combination of fluorine-based plasma treatment which depletes the 2DEG under the gate<sup>14)</sup> and the 20nm SiN<sub>x</sub> gate dielectric. An output current of 295mA/mm was

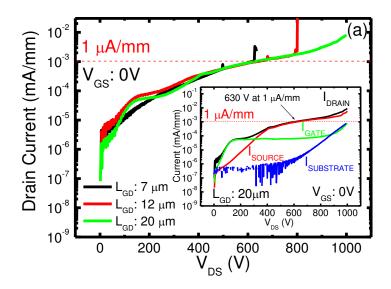

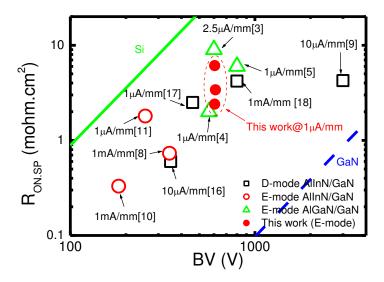

measured at  $V_{GS}$ :+10V and gate current remained below 50nA/mm with the  $V_{GS}$  between -6V and +10V. An on-off ratio as high as ~5x10<sup>7</sup> was obtained. It is noted that a  $V_{TH}$  hysteresis of ~0.68V is observed from the bi-directional gate sweeps between -6 and +10V, which is likely caused by electron trapping in the acceptor-like states at the interface between the gate dielectric and GaN cap. <sup>15,16)</sup> This hysteresis effect may be alleviated by employing surface treatment techniques prior to gate dielectric deposition to reduce the interfacial traps. <sup>16)</sup> Fig. 2(b) shows the DC I-V characteristics of the AlInN/GaN MISHFET. The specific onresistance ( $R_{ON.SP}$ ) increases linearly with increasing gate-drain separation ( $L_{GD}$ ). The  $R_{ON.SP}$  of the device with  $L_{GD}$ :7, 12 and 20  $\mu$ m is 2.1, 3.4 and 6.1m $\Omega$ .cm<sup>2</sup>, respectively. ( $R_{ON.SP}$  is calculated from the active area between the source and drain contacts and a 2 $\mu$ m contact transfer length extracted from TLM).

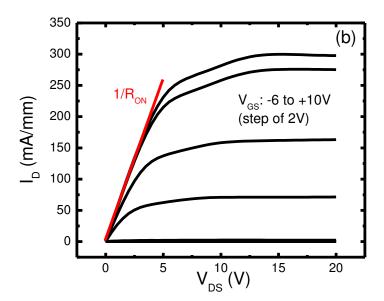

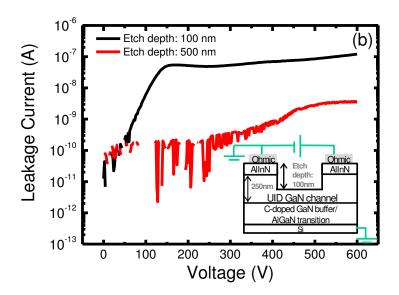

Fig. 3(a) shows the three-terminal off-state measurements of AlInN/GaN MISHFETs at  $V_{GS}$ : 0V. The sample was immersed in Fluorinert FC-40 to prevent surface flashover and the substrate was grounded during the measurements. The devices show an excellent voltage blocking capability with a BV as high as 606V at  $I_D$ :1 $\mu$ A/mm for  $L_{GD}$ :7 $\mu$ m at  $V_{GS}$ :0V. While the 7 $\mu$ m device showed a hard breakdown at 623V due to breakdown of the gate, no hard breakdown was observed up to 1000V for the device with  $L_{GD}$ :20 $\mu$ m.

It is noted that the gate leakage current ( $I_{GATE}$ ) dominates below 250V and leakage between source and drain terminals ( $I_{SOURCE}$ ) surpasses  $I_{GATE}$  as  $V_{DS}$  increases beyond 250V. Fig. 3(b) shows the leakage current measured from the two-terminal lateral buffer leakage structure with ohmic contacts isolated with a mesa etch. The leakage current is more than an order of magnitude higher in the structure with partially etched UID GaN layer (etch depth of 100nm) compared to the structure with completely etched UID GaN layer (etch depth of 500nm).

This suggests that the  $I_{SOURCE}$  is primarily due to leakage via the 250nm UID GaN channel in the three terminal off-state measurements. Reducing the UID GaN channel thickness may reduce  $I_{SOURCE}$  and provide a better confinement of 2DEG within the channel. Unlike other reported GaN-on-Si transistors, <sup>5,17)</sup> the substrate leakage current ( $I_{SUBSTRATE}$ ) is not the main leakage contribution and stays below  $1\mu A/mm$  up to 1000 V due to the  $7\mu m$  thick high resistive GaN buffer and AlGaN transition layers. The  $R_{ON.SP}$  versus BV performance of our enhancement mode AlInN/GaN MISHFETs is compared with the reported AlInN and AlGaN MISHFETs in Fig. 4.

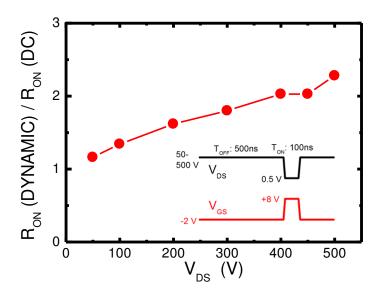

Dual-pulse measurements were carried out to characterize the dynamic on-resistance of the AlInN/GaN MISHFETs. The devices were held at  $V_{GS}$ :0V during the off-state and switched to  $V_{GS}$ : +8V during the on-state. During the off-state,  $V_{DS}$  up to 500V was applied and the dynamic on-resistance was measured at  $V_{DS}$ :0.5V during on-state. The duration of off-state and on-state were set at 500 $\mu$ s and 100 $\mu$ s, respectively and the substrate was grounded. Fig. 5 shows the ratio of dynamic on-resistance to DC on-resistance as a function of applied  $V_{DS}$ . The dynamic on-resistance increases with increasing off-state drain bias and is approximately 2.2 times the DC on-resistance at  $V_{DS}$ :500V, attributable to field-assisted charge trapping on the surface and/or in the carbon-doped GaN buffer region between the gate and the drain.  $^{18,19}$  Optimization of the field-plate geometry as well as improvement of the GaN buffer design may further reduce the dynamic on-resistance of the devices.

In summary, enhancement-mode AlInN/GaN MISHFETs with a threshold voltage of +3.0V and a blocking voltage of more than 600V at leakage current of  $1\mu$ A/mm and 1000V at leakage current of  $10\mu$ A/mm have been demonstrated using a 6-inch silicon substrate. This is, to our knowledge, the highest threshold voltage and blocking voltage reported in the

enhancement-mode AlInN/GaN MISHFETs. Pulsed measurements reveal that the dynamic on-resistance of the AlInN/GaN MISHFETs is nearly 2.2 times the DC value with the incorporation of field plate. These results suggest the excellent potential of AlInN/GaN MISHFETs for power switching applications.

## Acknowledgments

This work was funded by the Engineering and Physics Sciences Research Council (EPSRC), United Kingdom under EP/K014471/1 (Silicon Compatible GaN Power Electronics).

### References

- 1) H. L. Xing, Y. Dora, A. Chini, S. Heikman, S. Keller, and U. K. Mishra, IEEE Electron Device Lett. **25**, 161 (2004).

- 2) Y. Wu, M. J. Mitos, M. L. Moore, and S. Heikman, IEEE Electron Device Lett. 29, 824 (2008).

- 3) R. Chu, A. Corrion, M. Chen, R. Li, D. Wong, D. Zehnder, B. Hughes, and K. Boutros, IEEE Electron Device Lett. **32**, 632 (2011).

- 4) B. Lu, E. Matioli, and T. Palacios, IEEE Electron Device Lett. 33, 360 (2012).

- 5) J. J. Freedsman, T. Egawa, Y. Yamaoka, Y. Yano, A. Ubukata, T. Tabuchi, and K. Matsumoto, Appl. Phys. Express **7**, 041003 (2014).

- 6) E. Zanoni, M. Meneghini, A. Chini, D. Marcon, and G. Meneghesso, IEEE Trans. Electron Devices **60**, 3119 (2013).

- 7) J. Kuzmik, G. Pozzovivo, J. F. Carlin, M. Gonschorek, E. Feltin, N. Grandjean, G. Strasser, D. Pogany, and E. Gornik; Phys. Status Solidi C 6, S925 (2009).

- 8) Q. Zhou, H. Chen, C. Zhou, Z. H. Feng, S. J. Cai, and Kevin J. Chen, IEEE Electron Device Lett. **33**, 38 (2012).

- 9) A. Watanabe, J. J. Freedsman, R. Oda, T. Ito, and T. Egawa, Appl. Phys. Express 7, 041002 (2014).

- 10) H. Lee, D. Piedra, M. Sun, X. Gao, S. Guo, and T. Palacios, IEEE Electron Device Lett. 33, 982 (2012).

- 11) D. Morgan, M. Sultana, H. Fatima, S. Sugiyama, Q. Fareed, V. Adivarahan, M. Lachab, and A. Khan, Appl. Phys. Express 4, 114101 (2011).

- 12) S. Zhao, J. Xue, P. Zhang, B. Hou, J. Luo, X. Fan, J. Zhang, X. Ma, and Y. Hao, Appl. Phys. Express **7**, 071002 (2014).

- 13) M. Jurkovic, D. Gregusova, V. Palankovski, Š. Hascik, M. Blaho, K. Cico, K. Fröhlich, J. Carlin, N. Grandjean, and J. Kuzmík, IEEE Electron Device Lett. 34, 432 (2013).

- 14) Y. Cai, Y. G. Zhou, K. M. Lau, and K. J. Chen, IEEE Trans. Electron Devices **53**, 2207 (2006).

- 15) C. Mizue, Y. Hori, M. Miczek, and T. Hashizume, Jpn. J. Appl. Phys. **50**, 021001 (2011)

- 16) Y. Hori, Z. Yatabe, and T. Hashizume, J. Appl. Phys. **114**, 244503 (2013).

- 17) P. Srivastava, J. Das, D. Visalli, J. Derluyn, M. V. Hove, P. E. Malinowski, D. Marcon, K. Geens, K. Cheng, S. Degroote, M. Leys, M. Germain, S. Decoutere, R. P. Mertens, and G. Borghs, IEEE Electron Device Lett. **31**, 851 (2010).

- 18) W. Saito, Y. Kakiuchi, T. Nitta, Y. Saito, T. Noda, H. Fujimoto, A. Yoshioka, T. Ohno, and M. Yamaguchi, IEEE Electron Device Lett. **31**, 659 (2010).

- 19) M. J. Uren, J. Moereke, and Martin Kuball, IEEE Trans. Electron Devices **59**, 3327 (2012).

# **Figure Captions**

**Fig. 1.** The device structure of AlInN/GaN MISHFETs.

the AlInN/GaN MISHFET with L<sub>GD</sub>: 12µm.

Fig. 2. (a) Gate transfer characteristic of the enhancement mode AlInN/GaN MISHFET ( $L_{GD}$ : 12 $\mu$ m) with a threshold voltage of +3V ( $V_{GS}$  sweeps from -6V to +10V). The inset shows the gate (squares) and drain currents (circles) on a semi-logarithm-scale. (b) I-V characteristics of

**Fig. 3.** (a) Three-terminal off-state measurements of enhancement mode AlInN/GaN MISHFETs at  $V_{GS}$ : 0V with varying  $L_{GD}$ . The substrate was grounded during the measurements. Inset shows the individual components of off-state leakage current measured at drain, source, gate and substrate terminals of the AlInN/GaN MISHFET with  $L_{GD}$ : 20μm. (b) Leakage current measured from two-terminal lateral buffer leakage structure with a mesa isolation etch depth of 100 and 500nm. The gap spacing between the isolated pads is 15μm. The substrate was grounded during the measurements.

**Fig. 4.** Benchmark of R<sub>ON.SP</sub> versus BV of AlInN/GaN MISHFETs and enhancement-mode AlGaN/GaN MISHFETs.

Fig. 5. Ratio of dynamic  $R_{ON}$  to DC  $R_{ON}$  of enhancement-mode AlInN/GaN MISHFETs ( $L_{GD}$ : 20  $\mu$ m) as function of  $V_{DS}$ .

Fig. 1.

Fig. 2.

Fig. 3.

Fig. 4.

Fig. 5.