This is a repository copy of From Concept to Practice: an Automated LLM-aided UVM Machine for RTL Verification.

White Rose Research Online URL for this paper: <a href="https://eprints.whiterose.ac.uk/id/eprint/235874/">https://eprints.whiterose.ac.uk/id/eprint/235874/</a>

Version: Accepted Version

# **Proceedings Paper:**

Ye, Junhao, Hu, Yuchen, Xu, Ke et al. (8 more authors) (2025) From Concept to Practice: an Automated LLM-aided UVM Machine for RTL Verification. In: 2025 IEEE/ACM International Conference on Computer-Aided Design (ICCAD). IEEE/ACM International Conference on Computer-Aided Design.

https://doi.org/10.1109/ICCAD66269.2025.11240679

# Reuse

This article is distributed under the terms of the Creative Commons Attribution (CC BY) licence. This licence allows you to distribute, remix, tweak, and build upon the work, even commercially, as long as you credit the authors for the original work. More information and the full terms of the licence here: https://creativecommons.org/licenses/

# Takedown

If you consider content in White Rose Research Online to be in breach of UK law, please notify us by emailing eprints@whiterose.ac.uk including the URL of the record and the reason for the withdrawal request.

# From Concept to Practice: an Automated LLM-aided UVM Machine for RTL Verification

Junhao Ye<sup>1,2</sup>, Yuchen Hu<sup>1,2</sup>, Ke Xu<sup>1,2</sup>, Dingrong Pan<sup>2</sup>, Qichun Chen<sup>3</sup>, Jie Zhou<sup>1,2</sup>

Shuai Zhao<sup>4</sup>, Xinwei Fang<sup>5,\*</sup>, Xi Wang<sup>1,2,\*</sup>, Nan Guan<sup>6</sup>, Zhe Jiang<sup>1,2,\*</sup>

<sup>1</sup>School of Integrated Circuits, Southeast University, China <sup>2</sup>National Center of Technology Innovation for EDA, China

<sup>3</sup>College of Economics, Shenzhen University, China

<sup>4</sup>School of Computer Science and Engineering, Sun Yat-sen University, China

<sup>5</sup>Department of Computer Science, University of York, UK

<sup>6</sup>Department of Computer Science, City University of Hong Kong, Hong Kong

Abstract— Verification presents a major bottleneck in Integrated Circuit (IC) development, consuming nearly 70% of the total development effort. While the Universal Verification Methodology (UVM) is widely used in industry to improve verification efficiency through structured and reusable testbenches, constructing these testbenches and generating sufficient stimuli remain challenging. These challenges arise from the considerable manual coding effort required, repetitive manual execution of multiple EDA tools, and the need for in-depth domain expertise navigate complex designs. Here, we present UVM<sup>2</sup>, an automated verification framework that leverages Large Language Models (LLMs) to generate UVM testbenches and iteratively refine them using coverage feedback, significantly reducing manual effort while maintaining rigorous verification standards. To evaluate UVM<sup>2</sup>, we introduce a benchmark suite comprising Register Transfer Level (RTL) designs of up to 1.6K lines of code. The results show that UVM<sup>2</sup> reduces testbench setup time by up to 38.82× compared to experienced engineers, and achieve average code and function coverage of 87.44% and 89.58%, outperforming stateof-the-art solutions by 20.96% and 23.51%, respectively.

#### I. INTRODUCTION

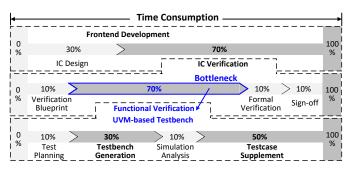

IC verification is the most resource and time-intensive phase in IC frontend design, consuming nearly 70% of the total development effort [1]. As illustrated in Fig. 1, IC verification usually begins with a verification blueprint, followed by functional verification, formal verification, and ultimately sign-off [2]. Among these stages, the functional verification alone accounts for approximately 70% of the total verification effort and encounters two significant challenges that hinder verification efficiency [3]–[7].

The first challenge is the complexity associated with testbench generation. UVM-based testbench is widely used in industrial due to its modular, layered architectures and reusable verification components [8]–[10]. For instance, stimulus generation is modularly encapsulated via sequencers, enabling reuse across designs [11]–[14]. However, this modularity significantly increases the complexity of testbench setup. Engineers must manually instantiate and configure numerous hierarchical components adhering to SystemVerilog class conventions and UVM library specifications [15]–[17], while ensuring accurate connections to the interfaces and protocol behaviours of the Design-Under-Test (DUT). As a result, verification testbench codebase typically grows to 4 or 5 times the size of the original RTL codes, imposing a substantial engineering burden.

The second challenge lies in testcase supplement, which involves generating effective test cases to achieve comprehensive function coverage [18]–[20]. This requires iterative refinement of test cases, including the careful generation of scenarios to capture boundary conditions, rare event sequences, and intricate state transitions. Coverage achieved, defined as the fulfilment of all user-defined function points, becomes increasingly more challenging as design complexity grows [21]–[23]. The manual identification and supplement of these scenarios into testbench are both costly and prone to human error.

\*Corresponding authors: xinwei.fang@york.ac.uk, xi.wang@seu.edu.cn, and zhejiang.uk@gmail.com

Fig. 1: Breakdown of the IC frontend design and verification workflow, demonstrating the effort required at each stage, where the functional verification dominates the time consumption of the entire workflow.

Recent advances in large language models (LLMs) have opened new opportunities for automated assistance in hardware design and verification [24]–[34]. Prior work has made promising strides: MEIC [35] demonstrated the feasibility of employing LLMs in verification. However, it neither adopts a UVM-based verification flow, thus remaining disconnected from industry-standard methodologies, nor scales beyond small designs (typically fewer than 150 lines of RTL), limiting its applicability to realistic industrial settings. UVLLM [36] improved upon this by integrating LLMs into a UVM-compatible workflow, demonstrating that LLMs can assist in generating UVM components. Nevertheless, the overall verification testbench still demands manual construction. Furthermore, both approaches rely on randomised stimulus generation without targeted coverage refinement or feedback-driven optimisation, leading to limited code and function coverage achievements and reduced verification efficiency.

In this paper, we present an LLM-aided UVM Machine (UVM²), the first systematic framework to realise an automated, LLM-driven function verification. By integrating domain-knowledge-guided prompt engineering with syntactic rule constraints [37]–[40], UVM² automatically generates UVM-based verification testbench, and iteratively refines test stimuli based on coverage feedback. This approach not only lowers the barrier to adopting UVM-based verification by significantly reducing the need for human involvement, but also turns a promising concept into a practical and scalable solution, demonstrating improved verification outcomes (e.g., more than 20% improvement over the the state-of-the-art solutions) and increased efficiency (e.g., reducing setup time by more than 15×).

The main contributions of this paper are:

- An automated framework for UVM testbench generation: UVM<sup>2</sup> employs LLMs guided by domain-specific strategies to produce industrial-grade, UVM testbench, significantly alleviating manual development overhead.

- Automated stimuli generation with an iterative refinement: UVM<sup>2</sup> iteratively improves function coverage by analysing collected coverage data and supplementing test stimuli, thereby

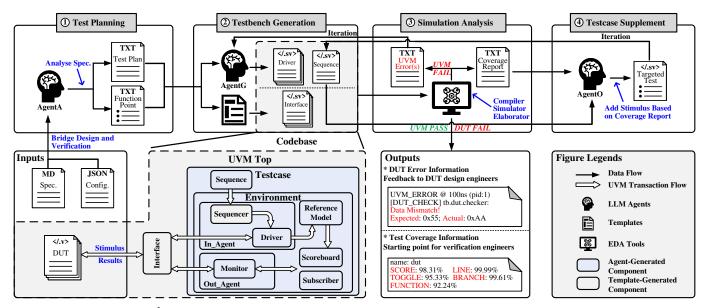

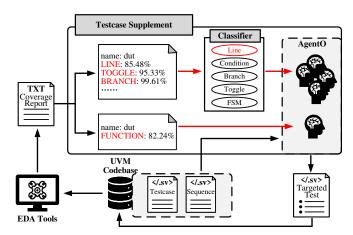

Fig. 2: Overview of the UVM<sup>2</sup> Framework, which integrates UVM with LLM agents to automate the IC verification workflow. The framework includes Analysis Agent (AgentA) for test planning, Generation Agent (AgentG) for automatic testbench creation and error-driven regeneration, and Optimisation Agent (AgentO) for iterative testcase supplement based on coverage analysis.

accelerating coverage achieved.

- End-to-end integration into practical verification workflows: UVM<sup>2</sup> supports the complete functional verification, demonstrating its scalability and adaptability across diverse and real RTL designs and protocols.

- Open-source release of the UVM<sup>2</sup> framework and benchmark: we release the complete UVM<sup>2</sup> framework and all component within it to support wider adoption. In addition, we publish our evaluation benchmark comprising 10 real RTL designs (ranging from 400 to 1,600 lines of code) for cross-comparison and future research at https://anonymous.4open.science/r/UVM\_Machine-7806/.

The rest of this paper is organised as follows. Section II introduces the overall architecture of  $UVM^2$ . Section III then details the key techniques in each workflow and their rationales. Section IV assesses our work based on the five proposed research questions. Section V concludes the paper and outlines future research directions.

## II. UVM<sup>2</sup>: AN OVERVIEW

Aiming to accelerate the verification execution loop, UVM<sup>2</sup> utilises task-specific LLM agents with templates within a standardised UVM tool-chain as shown in Fig. 2. It comprises three specialised agents, one each for analysis, generation and optimisation, and a library of reusable templates as predefined scripts that ensure generation accuracy and reduce LLM usage. UVM<sup>2</sup> produces the verification results as an error information report and a coverage report and assumes following three inputs:

- Design specifications: which define the intended functionality and behaviour of the DUT, written in Markdown format.

- Configuration files: in which the user specifies the target DUT and the reset state using a JSON file.

- DUT: the design entity implemented in RTL code.

These inputs are already expected in existing industrial verification and align with the standard workflow followed by verification engineers, enabling UVM<sup>2</sup> to integrate seamlessly without the need for additional formats or tool dependencies. To maximise accuracy while keeping token usage predictable, each LLM agent is fine-tuned and guided by domain-specific prompts. The overall flow is developed through the following iterative processes:

- **Test Planning.** The Analysis Agent (AgentA) examines the input design specification to identify function points and constructs a coverage-driven testcase plan.

- **Testbench Generation.** Leveraging the identified test plan, the Generation Agent (AgentG) and the pre-validated templates jointly produce a UVM-based verification testbench.

- Simulation Analysis. Any errors in the generated UVM testbench are captured during simulation and used to refine the verification testbench, while coverage data are also collected for analysis and supplement.

- **Testcase Supplement.** If coverage remains insufficient, the Optimization Agents (AgentO) create additional targeted sequences to improve stimulus diversity, iteratively refining the testbench until coverage goals or user-defined iterations are reached.

**Modularity and flexibility.** To allow UVM<sup>2</sup> to evolve with future verification techniques, all artefacts are exchanged via well-defined formats, enabling designers to swap in a domain-specific LLM, replace an EDA tool, or insert additional processes without impacting the validity of the workflow.

# III. THE FRAMEWORK PIPELINE

We first present test planning from input specifications (Section III-A) and UVM testbench generation (Section III-B), both serving as the foundation of the framework. We then describe simulation analysis with error handling (Section III-C) and coverage-driven supplementation (Section III-D) to refine the UVM testbench and improve verification quality. Finally, we introduce the benchmarking setup used to assess framework performance (Section III-E).

# A. Test planning

In IC design, the design process focuses on implementing functional behaviour, while functional verification ensures all possible scenarios, including edge cases, are handled correctly. Effective verification relies on interpreting the design specification and identifying function points for testing, a task requiring domain expertise. In UVM<sup>2</sup>, we automate this process with LLM-based agents, AgentA. However, general-purpose LLMs often struggle with complex specifications due to their lack of structured memory and tendency to hallucinate [41]–[43], leading to missed edge cases. To address this,

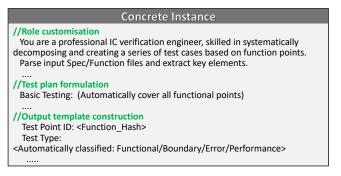

Fig. 3: Prompt Instructions for AgentA.

UVM<sup>2</sup> breaks down the analysis into a structured reasoning pipeline that mimics expert verification engineers.

As shown in Fig. 3, our approach follows a three-step analysis flow, designed to isolate the high-level cognitive tasks involved in human-driven verification planning:

- Role customisation: AgentA is first guided through prompts to act as an IC verification engineer, enabling it to identify the functional expectations stated in the specification, including signal dataflow, control dependencies, input/output interaction patterns, and state transitions. From these elements, the agent extracts specific functional points, leading to a deeper understanding of the design's intended behavior.

- 2) Test plan formulation: based on the function points, AgentA is required to define testing strategies for each functional point, including stimulus conditions, observability points, and coverage goals. For example, testing an arithmetic unit involves exercising the full range of operands and all signed/unsigned combinations under both overflow and underflow scenarios.

- 3) Output template construction: to ensure consistency, all related files, including the test plan and functional points (stored in .txt format), follow a predefined template. This template captures each functional point along with its associated test strategy and a draft test case, thereby enabling integration with UVM components and supporting manual inspection and refinement.

This three-step process not only ensures that critical functional points are consistently extracted from the specification, but also improves LLM reliability by enforcing deterministic reasoning paths. The generated test plan serves as the foundation for subsequent verification stages, ensuring alignment between spec-driven objectives and testbench implementation.

# B. Verification Testbench Generation

A robust verification testbench must not only support a broad range of stimuli and monitoring strategies but also reflect the structure and interaction logic of the underlying design. In UVM-based flows, the generation of testbenches is extremely time-consuming, largely due to component dependencies. UVM components are tightly coupled structurally and behaviourally. For instance, the Driver and Monitor are inseparable from the Interface: the Driver needs signal-level connectivity to drive transactions, and the Monitor must observe the same signals to collect functional responses. Likewise, an Agent encapsulates and coordinates multiple sub-components (Sequencer, Driver, Monitor), and cannot be constructed without knowing their details. Naively generating each module in isolation risks producing structurally invalid or semantically inconsistent testbenches.

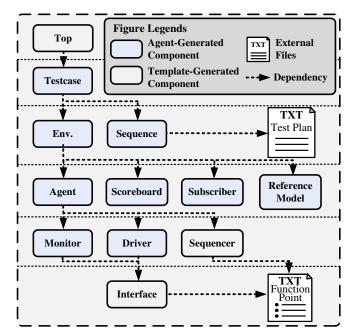

**Dependency-Driven UVM Testbench Flow.** To address this, UVM<sup>2</sup> employs a dependency-driven testbench generation flow as shown in Fig. 4 that sequences component creation based on interdependencies. The process begins with shared infrastructure (e.g., Interface), proceeds to leaf-level components (Driver, Monitor), then composites

Fig. 4: Dependency-Driven UVM Testbench Generation Workflow with Hierarchical Organization and External Dependencies.

Fig. 5: The "Top" module Template in the Testbench. This template facilitates the integration of the testbench with the DUT. The DUT instance name (blue text) and DUT ports (green text) are customizable parameters that allow the template to be configured for various verification scenarios.

(Agents), and concludes with environment-level modules (Scoreboard, Top, Testcase). This ensures each component is generated with complete contextual awareness of its dependencies.

Once the flow is defined, component generation strategies must be selected. Analysis reveals that certain UVM modules exhibit deterministic and repetitive patterns, with variations primarily in signal names and data widths. These can be efficiently synthesised using template-based generation. In contrast, modules involving behavioural logic, such as transaction sequencing or protocol-specific checks, require semantic understanding and are better suited for LLM-based generation. Accordingly, UVM<sup>2</sup> employs a hybrid synthesis strategy (Fig. 4), combining templates for structurally regular components with LLMs for functionally complex ones to optimise efficiency, correctness, and robustness.

**Template-Based Generation.** Templates are employed for modules that show high regularity across designs. This choice is motivated by three main factors: stability, speed, and reduced hallucination risk. Interface modules follow near-identical formats, varying primarily in the number and naming of input/output ports. Top modules serve as wrappers that instantiate all lower-level components and connect them via DUT ports; their structure is fixed and easily scriptable. Sequencer modules exhibit a rigid control pattern that dispatches sequences to the Driver and rarely require complex logic. Fig. 5 is an example

# Concrete Instance //Role customisation You are an IC verification engineer and you need to use UVM to build a tesebench. --UVM (component name) Generation Specification for (module name) --//Dependency definition The content of {new component name} shall be generated based on: {existing component names} //Function expectation 1.This file is part of the UVM tesebench components, used to {basic requirements) 2. At the beginning of the code, add {code requirements} 3. Pay attention to the input signals must be declare as {functional //Mistake mitigation The following mistakes must be prevented: {frequent errors}

Fig. 6: Prompt Instructions for AgentG.

generated by the top module using a template. After extracting the module name and port signal from the spec, the template will automatically fill in and generate the complete component.

**LLM-Based Generation.** In contrast, components with complex behaviour, such as Driver, Monitor, and Scoreboard, require precise functional encoding tailored to specific testcase semantics and verification goals identified earlier. These modules necessitate adaptable code generation that aligns with both design behaviour and test intent. To support this, UVM<sup>2</sup> applies a structured prompting framework for each LLM generation task, as shown in Fig. 6. Each prompt is systematically constructed in four stages to guide the LLM in producing accurate, context-aware SystemVerilog code.

- 1) Role customisation: we guide AgentG to act as an IC verification expert through prompt engineering, enabling it to more accurately understand the design functionality, verification objectives, and the required UVM components. This prompt-driven fine-tuning effectively constrains the relevance and scope of the generated content.

- 2) Dependency definition: dependency information is provided to ensure consistency with related components. For example, a Monitor must reference signal definitions from the Interface and transaction structures from the Sequence Item.

- 3) Function expectation: the prompt outlines the component's functional responsibilities, such as capturing rising-edge events, introducing random timing variations, or detecting protocol violations. It also includes guidance on recommended coding patterns, such as TLM port usage.

- 4) Mistake mitigation: typical mistakes are outlined in the prompt to reduce the impact of hallucinations caused by AgentG, such as missing reset logic, inconsistent transaction identifiers, or incorrect signal directions.

Together, these four stages emulate the thought process of skilled verification engineers, ensuring the generated code is functionally valid and integrable into the overall testbench architecture.

By integrating dependency-driven planning, template-based generation for structural components, and guided LLM synthesis for behavioural modules, UVM2 delivers a scalable and automationfriendly workflow for UVM testbench construction. This division of labour not only accelerates testbench generation but also improves modular correctness and robustness in industrial-scale projects.

# C. Simulation Analysis

Once the UVM testbench is assembled, the DUT is simulated using Synopsys VCS to verify functionality and assess coverage. VCS compiles the DUT and testbench, executes generated testcases, and collects reports on function coverage, code coverage, and runtime

# Algorithm 1: Repair Mechanism.

```

Input: Verification \log V_{log}

Output: repaired Uvm_Component UC<sub>True</sub>

1 Function Fixed_Err(V_{log}):

2

/* Err: Error message of component */

/* GeneAgentMap =

3

"driver": "G_driver_agent"

"monitor": "G\_monitor\_agent"

} * /

for phase \in phases do

4

5

if ErrInPhase(V_{log}, phase) then

PhaseErr = GetErr(V_{log}, phase);

6

for UC,Err \in PhaseErr_i do

7

AgentID = GeneAgentMap[UC];

8

UC_{True} = CallAgent(AgentID, Err);

10

end

end

11

12

end

13

return UC<sub>True</sub>

14 End Function

```

Fig. 7: Testcase Supplement Workflow with Coverage Analysis.

logs, which are essential for evaluating testbench quality and identifying verification gaps. If design bugs are found, UVM<sup>2</sup> provides detailed diagnostics to assist in debugging.

Repair Mechanism. However, due to the generative nature of our framework, initial outputs from LLMs or templates may contain errors, such as syntax issues, interface mismatches, or improper sequencing, particularly when LLMs receive ambiguous context or insufficient dependency information. Inspired by prior work such as MEIC, which demonstrated the value of iterative LLM refinement through feedback, we introduce a repair mechanism into UVM<sup>2</sup>. As outlined in Algorithm 1, if simulation fails, the framework attempts to repair faulty components using LLMs by taking UVM error logs as structured prompts. These are then fed back into the AgentG to drive a second (or third) round of regeneration, focusing on correcting specific structural or behavioural issues. This iteration cycle is repeated iteratively until one of two termination conditions is met: (i) the simulation completes successfully, or (ii) a predefined maximum iteration is exhausted.

# D. Testcase Supplement

Ensuring the correctness of a testbench is only one part of the verification process—it does not by itself ensure completeness. In hardware verification, both code and functional coverage are essential indicators, and low or plateaued coverage often suggests that the applied stimuli are not effectively exercising key parts of the DUT. To

## **Concrete Instance**

#### //Role customisation

You are an IC verification engineer and you need to use UVM to build a tesehench

--{modulename}\_add\_{type\_name}\_seq Generation Specification --

#### //Coverage analysis

The new {type\_name}\_seq shall be generated based on: {existing files} Consider the following characteristics of this type: {analysis\_guidance}

#### //Stimulus supplement

To generate effective content, ensure the stimulus meets these requirements: {stimulus\_requirements}

#### //Mistake mitigation

Within randomize() with {} blocks: \* Prohibited: {common mistakes}

Fig. 8: Prompt Instructions for AgentO.

tackle this issue, we introduce a testcase optimisation mechanism that enhances stimulus generation through sequence refinement, focusing on the protocol-level behaviours defined within UVM.

As shown in Fig. 7, testcase supplement phase in UVM<sup>2</sup> analyzes coverage gaps, categorizing them by logic region, transaction stage, or stimulus dependency. Deficient types are passed to AgentO, which revises sequences to target these gaps, generating new testcases until satisfactory coverage is achieved. Precise prompting is crucial, as LLMs without guidance may repeat patterns or miss gaps, making goal-oriented context essential for effective coverage improvement.

To resolve this, we design a prompting instructions for each coverage type. As shown in Fig. 8, it includes four stages that collaboratively shape the LLM's response:

- Role customisation: We assign AgentO the role of an IC verification expert, equipped with sufficient knowledge to generate and optimize the UVM testbench.

- 2) Coverage analysis: We also provide the DUT section, relevant protocols, and reference the specific coverage metrics or types that remain unsatisfied. For the test points that do not satisfy the coverage criteria, we offer explanations to facilitate the process.

- 3) Stimulus supplement: This part includes specific constraints, such as generating sequences with varying payload sizes or triggering edge-case interrupts. These information are used to assist the LLM in supplementing missing stimuli.

- 4) Mistake mitigation: To reduce LLM hallucination during stimulus supplementation, we explicitly forbid certain potentially problematic stimulus sequences in the prompt, including those with syntactic errors or functionally invalid behaviors.

**Optimisation mechanism.** The refinement loop is designed to be fault-tolerant. If the updated testbench fails simulation, UVM<sup>2</sup> reverts to the last valid version. The loop continues until either the target coverage is achieved or the number of optimization iterations exceeds a user-defined maximum. This closed-loop, coverage-driven refinement strategy mirrors expert workflows while dramatically reducing manual effort, resulting in faster, more reliable verification cycles.

# E. Benchmark

While simpler benchmarks such as RTLLM [44] and Verilog-Eval [38], which target designs with fewer than 200 lines of code, are useful for testing basic LLM capabilities in RTL design and verification, they do not accurately reflect the complexities of industrial scenarios. As such, they are not suitable for assessing the full scope and scalability of UVM<sup>2</sup> in real-world applications.

To evaluate the effectiveness of UVM<sup>2</sup>, we curated a diverse set of hardware design modules that collectively represent a wide spectrum of real-world verification challenges, as illustrated in Table I. These benchmarks span cryptographic cores (AES, SHA256, SM4), arithmetic units (ALU), memory controllers (DDR3, SDRAM), data

compression (Huffman Encoder - HUF), and peripheral communication interfaces (SPI, UART). Each module presents unique structural and behavioral characteristics, ranging from highly sequential logic (e.g., SHA256, HUF) to pipelined arithmetic computation (e.g., ALU) and complex control flow (e.g., DDR3, SDRAM).

We deliberately selected modules with varying design sizes and complexities, as reflected by their line counts, to assess the scalability and adaptability of our approach. For instance, the AES and HUF modules involve intricate data-path logic and state machines, posing significant coverage challenges. Memory controllers like DDR3 and SDRAM demand rigorous protocol compliance, while modules such as UART and SPI, though smaller, require nuanced handling of asynchronous communication and timing constraints.

## IV. EVALUATION

This section presents our experimental setup, evaluation metrics, research questions, and results to answer the questions.

**Experimental setup.** In our experiment, we employed LLM agents via the Deepseek API, with Deepseek-v3 as the default model. We set the temperature of the agents, which controls the output randomness of the LLM, to 0.3. Then we used our benchmark for assessment and adopted VCS as the simulation tool for our testbench. Additional, we set the iteration times of the iteration mechanism in both Testcase Analysis and Testcase Supplement to 2, since little improvement can be observed based on pre-experiment results. Following the pass@5 evaluation standard commonly used in the LLM field, each component was generated five times per module to minimise experimental randomness.

#### A. Evaluation Metrics

To evaluate the performance of our work in correct and complete UVM-based testbench, we propose the following metrics:

Success Rate of Generation ( $SR_G$ ): This metric evaluates the correctness of the generated UVM testbenches by comparing them against a reference testbench manually constructed by experienced engineers. A generated testbench is considered correct if it passes the full VCS simulation flow and produces results that match the expected outputs defined by the reference testbench. Otherwise, it is categorized as a generation failure. This metric reflects the functional validity of the generation framework.

$$SR_G = \frac{N_{\text{correct}}}{N_{\text{total}}} \times 100\% \tag{1}$$

**Coverage:** This metric quantifies the test completeness of a generated testbench after it has successfully passed the simulation phase. It is composed of two standard components:

- Code Coverage ( $C_{\rm code}$ ): Automatically provided by simulation tools such as VCS, this measures the percentage of RTL code exercised by the testbench (e.g., line, branch, toggle coverage).

- Functional Coverage ( $C_{\rm func}$ ): This represents how thoroughly the testbench exercises the RTL design with respect to the functional scenarios outlined in the design specification.

**Completion Time:** This denotes the time to complete the entire functional verification process depicted in Fig. 1. In our work, it corresponds to the time to execute the entire functional verification process under the premise that UVM<sup>2</sup> generates a correct Testbench.

# B. Research Questions

We conducted experiments to evaluate UVM<sup>2</sup> with respect to five key research questions (RQs):

**RQ1:** How effective is UVM<sup>2</sup> in generating syntactically and semantically correct UVM testbenches? This research question evaluates the capability of UVM<sup>2</sup> to produce valid UVM testbenches that conform to standard structure and compile without errors.

TABLE I: Benchmark designs used for evaluation, including a variety of commonly implemented hardware modules such as cryptographic cores (AES, SHA256, SM4), arithmetic units (ALU), memory and communication controllers (DFI, SDRAM, SPI, UART), and a Huffman encoder.

| Design | Description                                                                                                                              | Module<br>Counts | Line Counts |

|--------|------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------|

| AES    | Encrypts a 128-bit plaintext input using a configurable key (128, 192, or 256 bits) and outputs 128-bit ciphertext.                      | 8                | 684         |

| ALU    | A 32-bit unit that performs FP arithmetic, logical operations (OR, AND, XOR), shifts, FP to INT conversion, and complement.              | 7                | 409         |

| DFI    | A lightweight DDR3 memory controller that efficiently manages the interface between a system and DDR3 memory devices.                    | 2                | 430         |

| HUF    | A synchronous Huffman encoding system that compresses 4-bit input data symbols by calculating their frequencies,                         | 10               | 1,572       |

|        | generating Huffman codes, and outputting a compressed serial bitstream.                                                                  |                  |             |

| SDRAM  | A controller for synchronous dynamic random-access memory (SDRAM) with a Wishbone bus interface.                                         | 1                | 604         |

| SHA256 | A cryptographic unit that computes a 256-bit hash value from a 24-bit input message using the SHA-256 algorithm.                         | 3                | 1,412       |

| SM4    | A synchronous implementation of the SM4 encryption/decryption algorithm, supporting both modes through a 128-bit key and data interface. |                  | 1,142       |

|        |                                                                                                                                          |                  |             |

| SPI    | A lightweight SPI controller supporting Master mode with FIFO-based data transfer and interrupt-driven operation.                        | 1                | 839         |

| UART   | Facilitates serial communication between a host and peripherals, supporting configurable baud rates and stop bits.                       | 3                | 639         |

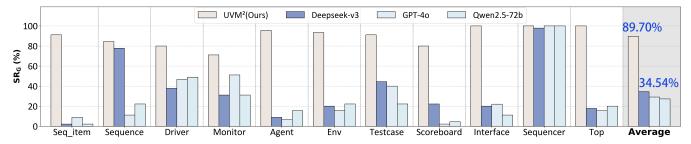

Fig. 9: SR<sub>G</sub> of 11 UVM components with UVM<sup>2</sup> against SOTA LLMs

RQ2: How does the verification completeness achieved by UVM<sup>2</sup> compare to existing LLM-based verification approaches? This question investigates whether UVM<sup>2</sup> can generate testbenches that reach comparable or higher code and functional testcase coverage than other LLM-driven methods.

RQ3: How much of a performance gain in terms of efficiency can end-to-end verification using UVM<sup>2</sup> achieve compared to that of expert engineers? This question explores whether UVM<sup>2</sup> can reduce the total time needed to complete the functional verification process relative to manual effort.

**RQ4:** How does the repair mechanism influence the success rate of UVM testbench generation? This question examines whether incorporating automatic repair significantly improves the ability of UVM<sup>2</sup> to generate usable testbenches after initial failures.

RQ5: How does the optimisation mechanism in UVM<sup>2</sup> affect functional coverage improvement? This research question evaluates the effectiveness of the optimization strategy in increasing the achieved coverage metrics during simulation.

# C. Results and Discussions

The results of our experiments are presented as follows, with each aligned to its respective research question.

**Result 1:** Fig. 9 illustrates the  $SR_G$  of UVM<sup>2</sup> for various UVM components, achieving an average success rate of 89.70%. Notably, the three components generated from the template technique achieve a 100% success rate, validating the reliability of this approach. Among components generated by AgentG, agent, env, testcase, and seq\_item exceed 90%  $SR_G$ . However, driver and monitor, two components requiring in-depth domain knowledge of timing information like handshakes, show lower success rates (approximately 80%), reflecting the challenge of encoding complex designs without explicit guidance.

UVM<sup>2</sup> is also compared with three widely-used LLM baselines: GPT-40 (closed-source), Deepseek-v3, and Qwen2.5-72b (two open-source models widely adopted for their strong problem-solving capabilities). To ensure experimental rigor, each generated component was

used to replace the corresponding module in a manually crafted UVM testbench developed by experienced engineers, while the remaining components were kept unchanged. This approach ensures a valid evaluation since individual components cannot be tested in isolation due to inherent interdependencies, as illustrated in Fig. 4. For each generation task, the rest of the testbench was provided as reference context. Among these baselines, Deepseek-v3 achieves the highest overall success rate at 34.54%. In contrast, UVM² reaches a success rate that is 2.59× higher, surpassing all baselines across every component category. Notably, in the agent and seq\_item categories, where UVM² particularly excels, baseline performance is minimal, as agent success rates are 8.88%, 6.66%, and 15.55%, and seq\_item success rates are 2.22%, 8.89%, and 2.22% for Deepseek-v3, Qwen2.5-72b, and GPT-4o, respectively. This significant discrepancy underscores critical limitations in baseline capabilities.

Fig. 10 provides concrete examples of such errors and their corrected versions, illustrating how LLM outputs deviate from UVM design norms without structured guidance.

**Insufficient protocol analysis/constraint generation.** UVM requires precise sequence constraints (e.g., DFI protocol specifications). Legacy LLMs fail to parse protocols, generating invalid constraints (e.g., incorrect address ranges). This oversight can derail simulations entirely, as critical scenarios remain unaddressed, not merely reducing coverage but rendering verification incomplete and unreliable

Hallucinations in naming/logic. LLMs invent invalid UVM class names or misapply methods. Naming like HUF\_Driver driver (as presented in Fig. 10) isn't inherently wrong. However, in this UVM component, other parts are named as drv. This naming inconsistency leads to mismatches during instantiation, triggering runtime errors. Such lapses in naming coherence violate UVM's structural norms, severely undermining the testbench's reliability.

**Inadequate understanding of TLM mechanism.** LLMs often omit critical TLM declarations, such as uvm\_analysis\_imp\_decl. Without these foundational elements, subsequent method usage becomes flawed, including incorrect instantiation of uvm\_analysis\_imp. This

| Error Analysis                                                                                                                         |                                                                                                                                              |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Category 1: Insufficient protocol analysis / constraint generation                                                                     |                                                                                                                                              |  |  |  |  |  |  |

| class DFI_seq_item extends uvm_sequence_item;                                                                                          | class DFI_seq_item extends uvm_sequence_item;                                                                                                |  |  |  |  |  |  |

| constraint valid_address_range { Constraints Error address_i inside {[0:12'h7563131F98F]}; }                                           | <pre>constraint valid_address_range {     address_i inside {[0:15'h7FFF]}; }</pre>                                                           |  |  |  |  |  |  |

| Category 2: Hallucinations in naming / logic                                                                                           |                                                                                                                                              |  |  |  |  |  |  |

| class HUF_Agent extends uvm_agent;                                                                                                     | class HUF_Agent extends uvm_agent;                                                                                                           |  |  |  |  |  |  |

| HUF_Driver driver;                                                                                                                     | HUF_Driver drv;<br>HUF_Sequencer sqr;                                                                                                        |  |  |  |  |  |  |

| Category 3: Inadequate understanding of the TLM mechanic                                                                               | sm                                                                                                                                           |  |  |  |  |  |  |

| Missing TLM header file declaration                                                                                                    | `uvm_analysis_imp_decl(_actual) `uvm_analysis_imp_decl(_expected)                                                                            |  |  |  |  |  |  |

| class AES_Encrypt_scoreboard extends uvm_scoreboard;                                                                                   | class AES_Encrypt_scoreboard extends uvm_scoreboard;                                                                                         |  |  |  |  |  |  |

| <pre>uvm_analysis_imp#(AES_seq_item, AES_scoreboard)expected_imp;<br/>uvm_analysis_imp#(AES_seq_item, AES_scoreboard)actual_imp;</pre> | uvm_analysis_imp_actual#(AES_seq_item,AES_scoreboard) actual_imp;<br>uvm_analysis_imp_expected #(AES_seq_item, AES_scoreboard) expected_imp; |  |  |  |  |  |  |

| Category 4: Ambiguous component responsibilities module uvm_Top();                                                                     | module uart_Top();                                                                                                                           |  |  |  |  |  |  |

| <br>uart_if ifc();                                                                                                                     | uart_if ifc();                                                                                                                               |  |  |  |  |  |  |

| Lack of exemplification of DUT                                                                                                         | uart_top #(9,1,0) dut ( );                                                                                                                   |  |  |  |  |  |  |

Fig. 10: Four categories of errors in LLM-generated UVM components and their corrections.

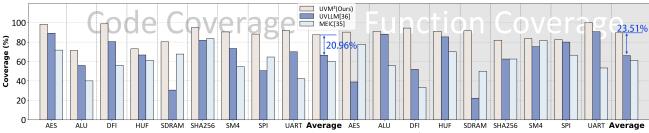

Fig. 11: Code Coverage and Function Coverage of UVM<sup>2</sup>, UVLLM, MEIC

combination of missing declarations and misapplied methods disrupts the TLM-based communication that underpins UVM verification, ultimately rendering components non-functional.

Ambiguous component responsibilities. Each UVM module must adhere to its role. For instance, the top module's duty includes proper DUT instantiation. Failing this (as in the incorrect example) violates the principle of clear - cut responsibilities. Such role - neglect doesn't just cause minor issues but invalidates the entire verification setup, highlighting that overlapping or overlooked duties can collapse the UVM testbench's effectiveness.invalidates testbench correctness.

These results demonstrate that relying solely on legacy LLMs for UVM testbench generation is infeasible due to domain knowledge gaps. By contrast, UVM<sup>2</sup> significantly enhances feasibility through targeted techniques (e.g., templates, iterative repair), achieving robust performance across both simple and complex components.

**Result 2:** We measured the coverage of the testbench generated by UVM<sup>2</sup> across 9 modules and compared it with two instances (MEIC and UVLLM) of LLMs applied in functional verification. Notably, since function coverage relies on the setting of expected functional scenarios by humans, the function coverage in this experiment used the functional scenarios defined by experienced engineers when constructing the testbench as the expected scenarios.

Fig. 11 demonstrates the verification coverage of UVM<sup>2</sup> and the other two control groups in each module. Specifically, the average code coverage of UVM<sup>2</sup> reaches 87.44%, which is 20.96% and 27.24% higher than UVLLM and MEIC respectively. In terms of function coverage, UVM<sup>2</sup> achieves 89.58%, which is 23.51% and 28.40% higher than UVLLM and MEIC respectively. Among them,

DDR3 achieves the highest code coverage of 98.31% and function coverage of 94.44%. As the number of RTL code lines increases and the number of sub-modules grows, the coverage of UVM² decreases but still remains competitive. HUF, an RTL code with nearly 1,500 lines and containing ten submodules, has a code coverage of 73.07%, however, the function coverage is 91.21% since several code segments contribute to just one function point in this design. Moreover, the coverage of UVM² in the verification of each module is higher than that of the other two works. This result indicates that UVM² significantly improves the test completeness in LLM-based verification. Meanwhile, UVM² also practices the theory of applying LLM to UVM-based verification, demonstrating that LLM-based testing does not have to rely solely on random stimuli.

**Result 3:** We recorded the time required for UVM<sup>2</sup> to complete each process, as well as the total time, comparing it with the time taken by experienced verification engineers to build UVM testbenches.

As shown in Table II, UVM<sup>2</sup> significantly outperforms human verification engineers in achieving similar coverage conditions. For the HUF module, UVM<sup>2</sup> achieves a speedup of 14.68×, while for less complex modules like DFI, the performance gap widens, with a speedup of up to 38.82×. The two most time-consuming phases, testbench generation and testcase supplement, have average execution time of 41.34 minutes and 20.84 minutes, respectively. As illustrated in Fig. 1, these phases account for approximately 30% and 50% of the total workflow time. In comparison, human experts typically spend 8.10 hours and 13.51 hours on these tasks, yielding speedups of 11.75× and 38.90× for UVM<sup>2</sup> respectively. These results demonstrate UVM<sup>2</sup>'s potential to significantly reduce

TABLE II: Completion Time of UVM<sup>2</sup> against Human Verification Engineers. The time statistics for each stage incorporate multiple generation attempts as required. The "Simulation" time includes compile, elaboration, simulation and repair iterations for components.

| Danism  |          |            | UVM <sup>2</sup> |            |           | Human  | Connection |

|---------|----------|------------|------------------|------------|-----------|--------|------------|

| Design  | Planning | Generation | Simulation       | Supplement | Total     | Total  | Speedup    |

| AES     | 3.55min  | 12.52min   | 6.47min          | 5.83min    | 28.37min  | 16.22h | 34.30x     |

| ALU     | 3.43min  | 15.22min   | 5.28min          | 8.51min    | 32.44min  | 16.13h | 29.83x     |

| DFI     | 2.12min  | 11.53min   | 5.90min          | 5.41min    | 24.96min  | 16.15h | 38.82x     |

| HUF     | 25.45min | 72.22min   | 40.85min         | 25.42min   | 163.94min | 40.12h | 14.68x     |

| SDRAM   | 32.18min | 80.22min   | 45.24min         | 25.35min   | 182.99min | 39.34h | 12.90x     |

| SHA256  | 22.48min | 48.43min   | 30.52min         | 30.74min   | 132.17min | 33.26h | 15.10x     |

| SM4     | 22.52min | 50.31min   | 35.50min         | 30.32min   | 138.65min | 30.25h | 13.09x     |

| SPI     | 24.46min | 65.25min   | 42.32min         | 35.47min   | 167.50min | 31.26h | 11.20x     |

| UART    | 4.29min  | 16.33min   | 12.52min         | 20.55min   | 53.69min  | 20.32h | 22.71x     |

| Average | 15.61min | 41.34min   | 24.96min         | 20.84min   | 102.75min | 27.01h | 15.77x     |

TABLE III:  $SR_G$  of  $UVM^2$ -generated UVM testbenches across three iterative verification rounds. "Gain" indicates the percentage improvement from the previous round.

| Design  | Round1 | Round2 | Gain   | Round3 | Gain  |

|---------|--------|--------|--------|--------|-------|

| AES     | 93.33% | 95.56% | 2.23%  | 95.56% | 0.00% |

| ALU     | 86.67% | 91.11% | 4.44%  | 93.33% | 2.22% |

| DFI     | 82.22% | 91.11% | 8.89%  | 91.11% | 0.00% |

| HUF     | 44.44% | 77.78% | 33.34% | 77.78% | 0.00% |

| SDRAM   | 42.22% | 86.67% | 44.45% | 86.67% | 0.00% |

| SHA256  | 66.67% | 84.44% | 17.77% | 84.44% | 0.00% |

| SM4     | 57.77% | 82.22% | 24.45% | 82.22% | 0.00% |

| SPI     | 64.44% | 80.00% | 15.56% | 80.00% | 0.00% |

| UART    | 84.44% | 86.67% | 2.23%  | 88.89% | 2.22% |

| Average | 69.13% | 86.17% | 17.04% | 86.67% | 0.50% |

verification time and highlight its competitiveness in accelerating functional verification.

**Result 4:** We evaluated the generation success rate of UVM test-benches with different iterations for the repair mechanism in UVM<sup>2</sup>.

Table III presents the generation success rate of UVM testbenches for each module across three rounds (including one initial generation round, followed by two repair iterations) under the condition of multiple tests. The results show that with our repair mechanism, the final generation success rate is 86.67%, reflecting an increase of 17.54% compared to the initial generation success rate of 69.13%. We observed that in AES and UART, the generation success rate could reach 93.33% in the round 1, while for RTL like HUF and SDRAM, multiple rounds were needed to generate a correct UVM testbench. This reveals the model's deficiency in understanding in-depth domain expertise regarding timing handshakes, interface protocols in IC design, and verification domains. Meanwhile, the improvement in the generation success rate between the third and second rounds is insignificant, merely 0.50%. Further increasing the number of repair iterations would not yield better results. This validates that setting the number of iterations in the repair mechanism to 2 is reasonable, avoiding unnecessary resource waste.

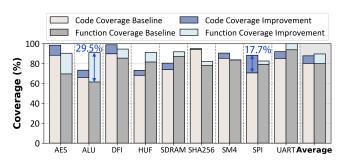

**Result 5:** We evaluated the effect of the optimization mechanism in UVM<sup>2</sup> on verification coverage by comparing the coverage with and without the testcase supplement phase. The results, presented in Fig. 12, highlight the improvements in both code and function coverage. Specifically, the optimization mechanism led to an increase of 7.6% and 9.7% in code and function coverage, separately.

Notably, the optimization is especially beneficial for certain modules. For instance, the SPI module witnesses a 17.7% increase in code coverage, while the ALU module experiences a 29.5% improvement in function coverage. However, some modules showed slight gains. In the SM4 module, for example, despite a 5.1% rise in code coverage, functional coverage hasn't improved noticeably. This outcome can be attributed to the fact that, in practical designs, certain function points require the joint triggering of multiple code blocks. In the case of the SM4 module, once function coverage reached 83.5%, an additional 5.4% in code coverage was insufficient to trigger new function points.

Fig. 12: Coverage improvement via testcase supplement It is important to note that the average time required for the testcase supplement phase was 20.84 minutes, as shown in Table II. Despite the time-cost overhead, the improvements in coverage demonstrate the competitiveness and effectiveness of the optimisation mechanism.

# V. CONCLUSION

In this work, we explored the use of LLMs for hardware design verification and identified key challenges that hinder their effectiveness. To address these issues, we introduced UVM<sup>2</sup> a structured framework that enhances LLM capabilities through hierarchical guidance and systematic prompting. UVM<sup>2</sup> enables the generation of UVM testbench with a generation success rate of 86.67%. With approximately 88% coverage, the average runtime is 102.75 minutes, achieving up to 38.82x speedup in development efficiency.

Recognizing the limitations of existing benchmarks, where most DUTs are under 150 lines, we developed a new benchmark(up to 2k lines) to better reflect real-world verification demands. UVM<sup>2</sup> seamlessly integrates with industrial tools such as Synopsys VCS to automate the entire verification workflow. It also incorporates a optimisation mechanism, allowing generated testbenches to reach an average 87.44% code coverage and 89.58% function coverage, outperforming state-of-the-art solutions by 20.96% and 23.51% respectively.

Our results demonstrate that UVM<sup>2</sup> significantly narrows the gap between LLM capabilities and the stringent requirements of industrial-grade hardware verification. However, challenges remain. Enhancing LLM understanding of hardware protocols and semantics, and embedding richer verification knowledge into the generation process, are essential directions for future work. By advancing these areas, we move closer to realizing autonomous, expert-level verification assistance powered by foundation models.

# VI. ACKNOWLEDGEMENT

We appreciate the reviewers for their insightful and helpful feedback. This work is supported by the National Key Research and Development Program (Grant No. 2024YFB4405600), the National Natural Science Foundation of China (Grant No. 62472086 and No. 92464301), the Basic Research Program of Jiangsu (Grant No. BK20243042), the Science and Technology Major Special Program of Jiangsu (Grants No. BG2024010), and the Start-up Research Fund of Southeast University (Grant No. RF1028624005).

#### REFERENCES

- [1] S. Lahti, P. Sjövall, J. Vanne, and T. D. Hämäläinen, "Are we there yet? a study on the state of high-level synthesis," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 38, no. 5, pp. 898–911, 2018.

- [2] P. Ashar and V. Viswanath, "Closing the verification gap with static sign-off," in 20th International Symposium on Quality Electronic Design (ISQED). IEEE, 2019, pp. 343–347.

- [3] K. A. Ismail and M. A. Abd El Ghany, "High performance machine learning models for functional verification of hardware designs," in 2021 3rd Novel Intelligent and Leading Emerging Sciences Conference (NILES). IEEE, 2021, pp. 15–18.

- [4] G. M. Danciu and A. Dinu, "Coverage fulfillment automation in hard-ware functional verification using genetic algorithms," *Applied Sciences*, vol. 12, no. 3, p. 1559, 2022.

- [5] R. Gal and A. Ziv, "Machine learning in the service of hardware functional verification," in *Machine Learning Applications in Electronic Design Automation*. Springer, 2022, pp. 377–424.

- [6] J. L. Hennessy and D. A. Patterson, Computer architecture: a quantitative approach. Elsevier, 2011.

- [7] S. Harris and D. Harris, Digital Design and Computer Architecture, RISC-V Edition. Morgan Kaufmann, 2021.

- [8] K. Salah, "A uvm-based smart functional verification platform: Concepts, pros, cons, and opportunities," in 2014 9th International Design and Test symposium (IDT). IEEE, 2014, pp. 94–99.

- [9] R. Madan, N. Kumar, and S. Deb, "Pragmatic approaches to implement self-checking mechanism in uvm based testbench," in 2015 International Conference on Advances in Computer Engineering and Applications. IEEE, 2015, pp. 632–636.

- [10] B. Vineeth and B. B. T. Sundari, "Uvm based testbench architecture for coverage driven functional verification of spi protocol," in 2018 International conference on advances in computing, communications and informatics (ICACCI). IEEE, 2018, pp. 307–310.

- [11] Y.-N. Yun, J.-B. Kim, N.-D. Kim, and B. Min, "Beyond uvm for practical soc verification," in 2011 International SoC Design Conference. IEEE, 2011, pp. 158–162.

- [12] L. Piccolboni and G. Pravadelli, "Simplified stimuli generation for scenario and assertion based verification," in 2014 15th Latin American Test Workshop-LATW. IEEE, 2014, pp. 1–6.

- [13] G. Visalli, "Uvm-based verification of ecc module for flash memories," in 2017 European Conference on Circuit Theory and Design (ECCTD). IEEE, 2017, pp. 1–4.

- [14] A. Vintila, I. Tolea, H. Du, and Q. Gong, "Portable stimulus driven systemverilog/uvm verification environment for the verification of a high-capacity ethernet communication endpoint," in *Proceedings of the* 2018 DVCON Conference and Exhibition Europe, Munich, Germany, 2018, pp. 24–25.

- [15] J. Bromley, "If systemverilog is so good, why do we need the uvm? sharing responsibilities between libraries and the core language," in *Proceedings of the 2013 Forum on specification and Design Languages* (FDL). IEEE, 2013, pp. 1–7.

- [16] J. Francesconi, J. A. Rodriguez, and P. M. Julian, "Uvm based testbench architecture for unit verification," in 2014 Argentine Conference on Micro-Nanoelectronics, Technology and Applications. IEEE, 2014, pp. 89–94.

- [17] L. S. Tavares, W. J. Chau, and F. J. Fonseca, "Case study: Uvm-fie: Enhancing uvm-based fault injection library for complex designs," in 2025 IEEE 26th Latin American Test Symposium. IEEE, 2025.

- [18] T. Pavithran and R. Bhakthavatchalu, "Uvm based testbench architecture for logic sub-system verification," in 2017 International Conference on Technological Advancements in Power and Energy (TAP Energy). IEEE, 2017, pp. 1–5.

- [19] M. Dharani, M. Bharathi, N. Padmaja, and K. Praveena, "Design and verification process of combinational adder using uvm methodology," in 2023 International Conference on Advances in Electronics, Communication, Computing and Intelligent Information Systems (ICAECIS). IEEE, 2023, pp. 359–362.

- [20] P. S. Kumar, R. Rajalakshmi, N. H. Kumar, B. P. Gupta, C. H. Nikhilesh, and J. S. P. Pavan, "Robust serial driver verification through uvm framework," in 2024 Control Instrumentation System Conference (CISCON). IEEE, 2024, pp. 1–6.

- [21] M. A. Salem and K. I. Eder, "Modified condition decision coverage: A hardware verification perspective," in 2013 14th International Workshop on Microprocessor Test and Verification. IEEE, 2013, pp. 8–13.

- [22] S. Wu, K. Zhao, X. Wang, S. He, and D. Guo, "An uvm-based verification platform for hardware and software co-design," in 2023

- IEEE 17th International Conference on Anti-counterfeiting, Security, and Identification (ASID). IEEE, 2023, pp. 21–24.

- [23] K. V. Reddy, "Uvm methodology: Industry-specific applications in modern hardware verification," *International Journal of Computer En*gineering and Technology (IJCET), vol. 15, no. 6, pp. 20–32, 2024.

- [24] S. Thakur, B. Ahmad, H. Pearce, B. Tan, B. Dolan-Gavitt, R. Karri, and S. Garg, "Verigen: A large language model for verilog code generation," arXiv preprint arXiv:2308.00708, 2023.

- [25] J. Blocklove, S. Garg, R. Karri, and H. Pearce, "Chip-chat: Challenges and opportunities in conversational hardware design," arXiv preprint arXiv:2305.13243, 2023.

- [26] Y. Tsai, M. Liu, and H. Ren, "Rtlfixer: Automatically fixing rtl syntax errors with large language models," arXiv preprint arXiv:2311.16543, 2023.

- [27] B. Ahmad, S. Thakur, B. Tan, R. Karri, and H. Pearce, "Fixing hardware security bugs with large language models," arXiv preprint arXiv:2302.01215, 2023.

- [28] W. Fu, K. Yang, R. G. Dutta, X. Guo, and G. Qu, "Llm4sechw: Leveraging domain-specific large language model for hardware debugging," in 2023 Asian Hardware Oriented Security and Trust Symposium (AsianHOST). IEEE, 2023, pp. 1–6.

- [29] M. DeLorenzo, A. B. Chowdhury, V. Gohil, S. Thakur, R. Karri, S. Garg, and J. Rajendran, "Make every move count: Llm-based high-quality rtl code generation using mcts," arXiv preprint arXiv:2402.03289, 2024.

- [30] M. Liu, M. Kang, G. B. Hamad, S. Suhaib, and H. Ren, "Domain-adapted llms for vlsi design and verification: A case study on formal verification," in 2024 IEEE 42nd VLSI Test Symposium (VTS). IEEE, 2024, pp. 1–4.

- [31] X. Yao, H. Li, T. H. Chan, W. Xiao, M. Yuan, Y. Huang, L. Chen, and B. Yu, "Hdldebugger: Streamlining hdl debugging with large language models," arXiv preprint arXiv:2403.11671, 2024.

- [32] W. Fang, M. Li, M. Li, Z. Yan, S. Liu, H. Zhang, and Z. Xie, "Assertllm: Generating and evaluating hardware verification assertions from design specifications via multi-llms," arXiv preprint arXiv:2402.00386, 2024.

- [33] B. Yao, N. Wang, J. Zhou, X. Wang, H. Gao, Z. Jiang, and N. Guan, "Location is key: Leveraging large language model for functional bug localization in verilog," arXiv preprint arXiv:2409.15186, 2024.

- [34] J. Zhou, Y. Ji, N. Wang, Y. Hu, X. Jiao, B. Yao, X. Fang, S. Zhao, N. Guan, and Z. Jiang, "Insights from rights and wrongs: A large language model for solving assertion failures in rtl design," arXiv preprint arXiv:2503.04057, 2025.

- [35] K. Xu, J. Sun, Y. Hu, X. Fang, W. Shan, X. Wang, and Z. Jiang, "Meic: Re-thinking rtl debug automation using llms," in Proceedings of the 43rd IEEE/ACM International Conference on Computer-Aided Design, ser. ICCAD '24. New York, NY, USA: Association for Computing Machinery, 2025. [Online]. Available: https://doi.org/10.1145/3676536.3676801

- [36] Y. Hu, J. Ye, K. Xu, J. Sun, S. Zhang, X. Jiao, D. Pan, J. Zhou, N. Wang, W. Shan et al., "Uvllm: An automated universal rtl verification framework using llms," arXiv preprint arXiv:2411.16238, 2024.

- [37] J. White, Q. Fu, S. Hays, M. Sandborn, C. Olea, H. Gilbert, A. Elnashar, J. Spencer-Smith, and D. C. Schmidt, "A prompt pattern catalog to enhance prompt engineering with chatgpt," arXiv preprint arXiv:2302.11382, 2023.

- [38] M. Liu, N. Pinckney, B. Khailany, and H. Ren, "Verilogeval: Evaluating large language models for verilog code generation," in 2023 IEEE/ACM International Conference on Computer Aided Design (ICCAD). IEEE, 2023, pp. 1–8.

- [39] K. Chang, Y. Wang, H. Ren, M. Wang, S. Liang, Y. Han, H. Li, and X. Li, "Chipgpt: How far are we from natural language hardware design," arXiv preprint arXiv:2305.14019, 2023.

- [40] P. Sahoo, A. K. Singh, S. Saha, V. Jain, S. Mondal, and A. Chadha, "A systematic survey of prompt engineering in large language models: Techniques and applications," arXiv preprint arXiv:2402.07927, 2024.

- [41] G. Perković, A. Drobnjak, and I. Botički, "Hallucinations in Ilms: Understanding and addressing challenges," in 2024 47th MIPRO ICT and Electronics Convention (MIPRO). IEEE, 2024, pp. 2084–2088.

- [42] G. P. Reddy, Y. P. Kumar, and K. P. Prakash, "Hallucinations in large language models (Ilms)," in 2024 IEEE Open Conference of Electrical, Electronic and Information Sciences (eStream). IEEE, 2024, pp. 1–6.

- [43] S. Tonmoy, S. Zaman, V. Jain, A. Rani, V. Rawte, A. Chadha, and A. Das, "A comprehensive survey of hallucination mitigation techniques in large language models," arXiv preprint arXiv:2401.01313, 2024.

- [44] Y. Lu, S. Liu, Q. Zhang, and Z. Xie, "Rtllm: An open-source benchmark for design rtl generation with large language model," arXiv preprint arXiv:2308.05345, 2023.