This is a repository copy of *Exploring the Feasibility of Novel 3D Polyhedrally-Tiled Computing Arrays*.

White Rose Research Online URL for this paper: <a href="https://eprints.whiterose.ac.uk/id/eprint/232470/">https://eprints.whiterose.ac.uk/id/eprint/232470/</a>

Version: Published Version

### Article:

Crispin-Bailey, Christopher orcid.org/0000-0003-0613-9698, Thuphairo, Pakon, Austin, Jim orcid.org/0000-0001-5762-8614 et al. (2 more authors) (2025) Exploring the Feasibility of Novel 3D Polyhedrally-Tiled Computing Arrays. IEEE Access. 11146660. pp. 159685-159713. ISSN: 2169-3536

https://doi.org/10.1109/ACCESS.2025.3605303

# Reuse

This article is distributed under the terms of the Creative Commons Attribution (CC BY) licence. This licence allows you to distribute, remix, tweak, and build upon the work, even commercially, as long as you credit the authors for the original work. More information and the full terms of the licence here: https://creativecommons.org/licenses/

### Takedown

If you consider content in White Rose Research Online to be in breach of UK law, please notify us by emailing eprints@whiterose.ac.uk including the URL of the record and the reason for the withdrawal request.

Received 2 June 2025, accepted 31 July 2025, date of publication 2 September 2025, date of current version 17 September 2025.

Digital Object Identifier 10.1109/ACCESS.2025.3605303

# **Exploring the Feasibility of Novel 3D Polyhedrally-Tiled Computing Arrays**

CHRIS CRISPIN-BAILEY<sup>101</sup>, PAKON THUPHAIRO<sup>102</sup>, STEVEN WRIGHT<sup>101</sup>, ANTHONY MOULDS 1, AND JIM AUSTIN 2, AND JIM AUSTIN 1, AND JIM AUSTIN 2, AND JIM AUSTIN 2, AND JIM AUSTIN 3, AND JIM 3,

<sup>2</sup>Department of Computer Engineering, Faculty of Engineering, Rajamangala University of Technology Rattanakosin, Nakhon Pathom 73170, Thailand

Corresponding author: Chris Crispin-Bailey (chrisb@cs.york.ac.uk)

This work was supported in part by the Royal Thai Government National Science and Technology Development Agency (NSTDA) Ph.D. Scholarship of Office of Educational Affairs (OEA) under Grant ST\_G5599, and in part by U.K. Government through Engineering and Phsyical Sciences Research Council (EPSRC) under Grant G0103201 IFPT-2023-04. The work of Pakon Thuphairo was supported by the Faculty of Engineering, Rajamangala University of Technology Rattanakosin.

**ABSTRACT** Polyhedral tiled computing arrays (PTCAs) are a largely unexplored paradigm in which the assembly of high performance computing (HPC) structures may be achieved by the multidimensional tiling of particular polyhedral modules, each housing computing devices. Typically, PTCAs form physical three-dimensional (3D) topologies which readily support logical three-dimensional topologies. PTCAs eliminate the need for traditional backplanes, racks and custom host circuit-board modules, while inherently composing coherent and scalable input/output (IO), power and cooling grids simply by abutting to neighboring modules in one or more dimensions. This highly novel concept offers unique possibilities in all three of those domains, and therefore quantifying PTCA capabilities and limitations is critical in establishing the desirability of such systems for future modular and heterogeneous HPC systems. The questions must then arise: is this a realistic paradigm?, and, can such a system be practically engineered? In this paper we contribute a number of insights, an analytical methodology for the evaluation of a specific class of PTCAs, based upon simple-cube and truncated octahedral modules arranged into cubic arrays, and we demonstrate the use of numerical methods and formulae to analyze the potential capabilities and limits of such novel systems with both existing reference points and future technology expectations. Whilst mapping out all aspects of this novel design-space is somewhat speculative, and beyond the scope of a single paper, we do conclude by identifying key challenges and 'road-map' goals aimed toward finally reaching that objective.

**INDEX TERMS** 3D mesh arrays, future computing, HPC, interconnection network, network topology, polyhedra, power density, system cooling, three-dimensional interconnect.

# I. INTRODUCTION

Traditionally, the most convenient route to construct a large-scale computer system has been to use a cabinet, backplane, rack, and circuit board assembly: either from highly standardized components or via custom rack-based printed circuit board (PCB) designs, engineered for each specific solution. Although mainstream, this approach introduces multiple levels of technical and engineering hierarchy even before assembly can be considered complete as a system, and

The associate editor coordinating the review of this manuscript and approving it for publication was Tomas F. Pena.

effectively imposes 2D models of assembly onto systems that are often logically structured as 3D topologies in actuality.

Given the direction of Moore's law, Dennard scaling, VLSI technology road-maps, and Koomey's law, it is now timely to better understand new paradigms and potentially identify radically new concepts for future high-performance computing (HPC) systems. One such possibility relies upon polyhedral tiles: 3D forms that themselves tile into 3D structures. There is, at best, sparse literature indicating work in this field to date, indicating novelty and a need for innovation and exploration of this design space to establish its feasibility.

<sup>&</sup>lt;sup>3</sup>Department of Computer Science, University of York, YO10 5DD York, U.K. (Retired)

Previous work undertaken in this area shows the potential for large-scale 3D system assemblies based upon polyhedral tiled computing array (PTCA) concepts, including power grid simulations, evaluations of wired and wireless connectivity strategies, hardware prototypes and network/workload modeling comparisons to more traditional physical topologies [1], [2], [3], [4], [5]. However, there is now a need for a well-defined numerical approach to evaluating such systems on a theoretical basis, in order to understand their viability as genuine alternatives. This includes modeling of performance-relevant metrics such as the number of processors, IO bandwidths, power consumption, and FLOPS, but in the case of PTCAs it is also important to understand size, volume, power delivery, heat management and their related engineering challenges. This paper seeks to evaluate four key questions that are critical for arriving at useful conclusions about the viability of PTCAs in real-world deployment:

- 1) What are feasible shapes and sizes for cores?

- 2) Can cascaded power grids achieve required capacities?

- 3) Can tiled modules interface to each other effectively?

- 4) Is power density and cooling viable in such systems?

These are important questions, and can only be answered by either building non-trivial prototype systems, or by making use of analytical models and simulations to examine the detail of these parameters. Ultimately bringing both together would provide the ideal outcome.

Specifically, this paper makes the following contributions:

- A set of mathematical equations is presented that can be used to derive a number of useful properties of a PTCA;

- It explores possible PTCA configurations, evaluating IO, power, and physical parameters, and constraints for a range of PTCA array sizes;

- A set of use-case evaluations is detailed, showing specific design goals being translated into a PTCA paradigm and reporting on their system characteristics;

- An evaluation of power density versus size and core power is given, and implications for current and future petascale and exascale PTCA systems are considered.

- Finally, a number of 'road-map' recommendations are given for more detailed studies into specific aspects of PTCA design space, suggesting a set of 'road-map goals' aimed toward a complete understanding of this novel paradigm.

The remainder of this paper is structured as follows: Section II outlines the background and motivations for PTCA; Section III introduces a series of mathematical equations for predicting the physical and computational characteristics of PTCAs; Section IV demonstrates the use of these mathematical models to evaluate use-cases inspired by relevant and well understood real world HPC systems; Section IV-E evaluates the potential for technological trends to shift the perspective over the coming 10-year horizon; Section V provides a summary of the necessary road-map objectives needed to move forward toward understanding and engineering of practical PTCA systems at large scales and,

finally, Section VI concludes this paper with a final view of work presented and its implications.

### A. SUMMARY OF KEY TERMS INTRODUCED

For convenience, the following quick introduction to key terms introduced in this paper may be useful to readers.

- PTCA: Polyhedral Tiled Computing Array. An array of polyhedral shaped/packaged computational modules.

- **Polyhedra/Polyhedron**: a 3D structural shape with geometric properties.

- **T-facet**: a trapezoidal (typically square) facet on the surface of a relevant polyhedron.

- **H-facet**: a hexagonal facet on the surface of a relevant polyhedron.

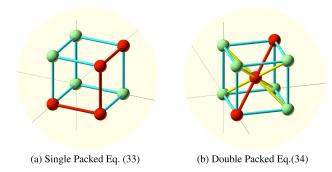

- **Single-packed array**: in this paper this refers to a 3D array where only T-facets are abutted in the tiling model, resulting in an incomplete space-packing outcome.

- **Double-packed array**: in this paper this refers to a 3D array where spaces between tiled polyhedra are filled with other polyhedra (involving both T and H-facet abutment), and achieving complete or high-density space packing outcomes.

- **Kelvin-Core / K-core**: a short-hand name given in this paper to a truncated octahedral polyhedron a shape which has six 'T' and eight 'H' facets.

- PCB: Printed Circuit Board.

- MCM: Multi-Chip Module.

- SIP: System-In-Package.

- **SOC**: System on Chip.

- FLOPS Floating point operations per second.

# **II. BACKGROUND CONCEPTS AND MOTIVATION**

# A. MOTIVATION

Before expanding into detail, it is perhaps useful to highlight some key comparisons in terms of the approach which PTCA attempts to offer, as differentiated from other mainstream HPC examples. Consider Table 1, which compares a number of mainstream HPC cases against a generic PTCA model:

- Many existing systems depend upon blade or custom board level designs which aggregate multiple processing elements into local groups, and then associate them via rack-mount structures. Those modules are typically powered via a high-current backplane power bus.

- PTCA utilizes freely tileable modules, whereby abutting a number of modules forms a typically 3D physical array of varied possible overall structure (a 3D mesh being the most obvious).

- Power distribution in PTCA systems is via a collective 3D-scalable power grid, formed by tiling of modules.

- In mainstream systems, IO is often hierarchical combining board-level groupings of processing elements with cable-based inter-modular connectivity, resulting in large numbers of cables with lengths of the order of metric metre or sub-metre scales.

- PTCA uses point-to-point centimetre-scale connection paths in a typically uniform grid structure.

- Mainstream cooling generally relies upon air-cooled cabinet designs, but increasingly the use of external conduits and 'bolt-on' cold-plates and fluid-delivery networks is commonplace. Full liquid-immersion is a newer approach in terms of mature large-scale solutions but growing in frequency of deployment.

- PTCA envisages internalized cooling voids passing through the inner space within the tiled module, and the formation of contiguous air/liquid cooling paths by virtue of modules abutting into array structures.

From these basic observations, one can see that PTCA sits in a very different corner of the design space than traditional and mainstream HPC solutions, with multiple differentiating factors. The following sections will expand these comparisons in significantly more detail.

Traditional rack-mount systems are widely used and have the convenience of a well-tested mode of assembly, but also come with significant limitations. A primary issue is that processing and auxiliary components must be aggregated via rack-mount PCB planes, themselves complex design endeavors, and any such host-board design must also be constrained by rack and backplane requirements rather than being able to directly mirror the intended logical topology of the system. This hinders the literal implementation of logically three-dimensional (3D) computing topologies, obliging them to map onto what are inherently closer to two-dimensional (2D) signaling structures such as rack and backplane, and/or heavily augmented by complex inter-module IO cabling. This often leads to design compromises that are undesired and potentially detrimental to performance and cost.

Such constraints are tolerated in lieu of the convenience of having a well-established standard construction medium and accepting the compromises resulting from mapping logically 3D topologies onto '2D' structures. Some systems aggregate such data flows into common data-channels via the backplane or inter-board and inter-cabinet data highways. Likewise, these are at best described as '2.5D' systems assemblies in comparison to their logical 3D topologies. The SpiNNaker and MDGRAPE systems are examples where this approach is observable [6], [9]. On the other hand, relative ease of maintainability in a rack system is a positive aspect that should also be noted.

Meanwhile, more loosely-coupled systems may route inter-node messaging onto traffic-aggregating switching networks such as fat-tree routing structures, but cannot facilitate direct connectivity between cores in 3D physical space. Consequently, extra costs are introduced in terms of message structure, buffering, latency, hardware component expense, power consumption, heat, physical space, and other factors. With the evolution of ever more complex AI and big-data systems these issues will only become more salient in the coming decade.

In strong contrast, PTCAs are defined as true 3D assemblies, and permit direct point-to-point connection

to neighboring nodes in all three dimensions at large scales with uniformity. This is achieved by employing a directly three-dimensional modular system assembly paradigm founded upon the principle of composing arrays of modular polyhedral computing nodes from within the class of tileable polyhedra.

The nature of such modules allows direct connection to nearest neighbors in three dimensions for power, IO and system cooling. All three of these requirements may then aggregate into their respective networks simply by abutment of such modules. Compositions of system-level PCB planes are not required, and rack-mount and backplane concepts are eliminated in any traditional sense. Of course there is a trade-off, in that PTCA systems lose some of the generality of switch-routed topological implementations, and maintainability must be managed in different ways, but there are nonetheless valuable gains where tightly-coupled grid-like fabrics are desirable.

While modules that are simple cubes might seem the obvious choice of modular shape for such a paradigm, and having the advantage of plain simplicity, there are other partial or fully space-filling polyhedra, some having distinctive capabilities including extra-dimensional properties beyond that of a cube-based X-Y-Z grid structure.

Tiled modules therefore offer the possibility of overcoming such serious limitations, simultaneously solving three key problems – logical versus physical IO mapping, power distribution, and heat dispersion, simply by adopting a polyhedron-based assembly model.

# B. RELATED WORK

Significant insights and motivations may be found in the work of earlier studies, highlighting the key advantages and necessities of moving scaling into higher dimensions to meet the needs of increasingly complex future systems, with an important observation made by those authors:

"We find that historical efficiency trends are related to density and that current transistors are small enough for zetascale systems once communication and supply networks are simultaneously optimised. We infer that biological efficiencies for information processing can be reached by 2060 with ultra-compact space-filled systems that make use of brain-inspired packaging and allometric scaling laws". [13] (published in 2011).

Meanwhile, a recent white paper on future unconventional HPC systems by leading researchers, also identifies some important key requirements to meet the needs of future HPC systems over the next decade [14]. These include, in particular:

- Short low-latency electrical links

- Co-packaged optical interconnects

- Modular fabrics

- Disruptive heterogeneity

- Flexible wire-composable systems

| TABLE 1. Cor | nparison of | some kev | design : | factors f | or mainstream | and PTCA systems. |

|--------------|-------------|----------|----------|-----------|---------------|-------------------|

|--------------|-------------|----------|----------|-----------|---------------|-------------------|

| MODEL                           | Compute Node IO Hierarchy                                                              | Power Delivery               | Cooling                                                           |

|---------------------------------|----------------------------------------------------------------------------------------|------------------------------|-------------------------------------------------------------------|

| Spinnaker [6]                   | Inter-Nodal PCB Inter Board Custom Backbone Inter-Rack Cable IO paths up to 0.5m scale | Rack and cabinet Power Bus   | Air cooled Cabinet                                                |

| Google TPU Data Centre [7], [8] | Cable, Direct Optical beam interchange                                                 | Rack and cabinet Power Bus   | Cold-Plate Liquid Cooling+air cooling                             |

| MDGRAPE-4A [9], [10]            | Inter-CPU wired, Inter-board optical IO, IO paths 1 metre scale (est)                  | Rack and cabinet Power Bus   | air-cooled                                                        |

| Anton-3 [11], [12]              | Inter-board High Speed IO cabling, IO paths 1 metre scale (est)                        | Rack and cabinet Power Bus   | Liquid Cooling, Cold plate                                        |

| PTCA                            | Infra-nodal PCB,<br>Point-to-Point Dedicated Links,<br>IO paths on 100 mm scale        | Inter-nodal distributed grid | Air or liquid internalized cooling grid, direct immersion cooling |

The authors argue that, in the context of both of these perspectives, co-integration of cooling solutions are also of high priority, and would add this to the list as a further important challenge to be met, especially given the diverse range of technologies and the granularity of solutions at play in that domain [15].

It is useful to make some observations upon the limitations of rack-mount assembly, which are easily observed in some successful, well known and relatively large-scale systems, which adopt fairly standard rack and backplane approaches. For example, in the SpiNNaker project [6], [16], [17], [18], [19], the SpiNNaker 'million core' system is built from a number of adjacent and linked server cabinets, with each cabinet containing five rackmount PCB clusters. Each rackmount cabinet contains an array of identical SpiNNaker multicore SOCs (system-on-chip) arranged as twenty four 48-chip PCBs in racks and cabinets with five modules per cabinet. In computational terms however, SpiNNaker is inherently a 3D logical topology (a hexagonal torus), and achieves connectivity between SOCs on different rack modules via multiplexed (SpiNNlink) backplane routed data highways, and also by connection between the server cabinets, reportedly requiring 'thousands of metres' of cabling [17]. A considerable amount of hierarchical design and infrastructure is thus imposed upon the implementation, which ultimately aims to combine many processing nodes into a collective system array.

Cooling is an equally complex problem in large-scale array designs, with hierarchical and inter-modular issues analogous to that of data connectivity. For example, the Google TPU server has cooling pipes that must connect across multiple domains in order to form a large-scale cooling network [8]. This cold-plate directed liquid cooling approach is essential given the power density of the Google TPU units. These approaches seek to overcome the power density limitations of air cooling, where server cabinets can struggle to achieve power densities beyond the region of 40 kW unless employing external air-chiller units or internal highly directed cooling

approaches. Fluid-assisted cold-plate cooling may push limits as high as 100 kWh [20], [21], while bulk immersion systems can achieve power densities approaching 200 kW for volumes similar to a 42U rackmount cabinet ( $\approx 1m^3$ ). When exploring new and novel design concepts, it is anticipated that cooling strategies will require detailed modeling. Examples of such work for more traditional architectures include modeling and optimizing workload (and thus power) distribution within arrays, and detailed modeling at the component and board level [22], [23], [24]. The need for flow dynamics (be it air or liquid) is an important requirement for 3D grid concepts, especially as dimensions scale downward and effects such as turbulence and flow-resistance within cooling voids become more significant relative to general liquid or air flow models.

Another notable system in this domain, MDGRAPE-4A, occupies a different end of the spectrum to SpiNNaker (which uses devices with power consumption of the order of only a few Watts), instead relying upon a much smaller array of albeit far more powerful processing nodes, consuming of the order of 120 W (with core SOC power of 85 W), in contrast to the reported 1 W for the SpiNNaker SOC [9], [19]. For comparison, the latest Google TPU v4 devices are approaching 200 W power consumption [7]. Likewise, the Anton series of HPC systems also typically scale up to 512 nodes with a similar scale and complexity to MDGRAPE-4A, i.e., fewer but more powerful nodes, again arranged in a 3D logical structure, but using highly optimized custom ASIC components in place of more general commodity CPUs [10], [11], [12]. The Google TPUv4 installation also operates on a grid-wise principle, using a 3D torus, though using an advanced optical switching network to link at a higher level of hierarchy [7]. All of these aforementioned and very successful systems are arranged in PCB planes, racks, cabinets, and inter-cabinet connectivities, with similar 2D physical trade-offs versus a true 3D logical

More generally, 3D logical topologies, including 3D mesh variants, have been of great interest in a wide range of

computing problems, including scientific modeling problems, big data, image processing, and increasingly complex AI systems. These systems vary widely in scale: SpiNNaker, for example, achieves an impressive 'million core' system scale, and yet is orders of magnitude smaller in scale than future neuromorphic systems might require, while MDGRAPE-4A, BlueGene, Google TPU, and others use hundreds of more powerful processors [6], [7], [9], [10], [11], [25], [26], [27], [28], [29].

Many computational application domains have 3D *logical* workload topologies, including volumetric medical imaging, molecular modeling, drug discovery, protein modeling, climate modeling, aerodynamics and fluid dynamics, among others [11], [30], [31], [32], [33], [34]. Such requirements are not limited only to traditional CPU or indeed GPU processing elements, but can also employ arrays of reconfigurable FPGA accelerators [35], or even optical computing paradigms [36]. However, they are often mapped onto very different physical structures. Taking an inherently 3D (three-dimensional) computing topology and mapping it onto, for example, a fat-tree physical architecture, presents challenges and compromises for cost and scalability alongside their advantages. This indicates that there is merit in building HPC systems as truly 3D physical structures, provided that they can overcome the key design challenges that this presents.

Meanwhile, a substantial body of work has accumulated which addresses the concept of mapping common logical topologies onto uniform and semi-uniform 2D and 3D grid arrays in the physical domain [6], [16], [25], [26], [28], [37], [38], [39], [40], [41], [42], [43]. The ability to 'fold' complex structures such as tori onto both 3D arrays and other physical topologies effectively means that an array structure such as PTCA can accommodate a wide range of computing models and offer some potentially unique advantages alongside its limitations.

All of these cases illustrate similar underlying challenges in terms of IO connectivity, power networks, and cooling pathways. Efficient mapping of 3D logical problems onto true physically 3D-connected hardware architectures, as 3D grids or otherwise, is therefore an important and timely area for investigation if the potential for future systems evolution toward, what are presently considered unconventional paradigms, is to be fully explored.

Another observation can be made of those systems and in general terms: most computing arrays have power grids, IO, and heat extraction systems 'on the outside'. This is observable in the cooling systems of the Google TPU arrays, and the IO cabling of SpiNNaker. It may seem an obscure question, but what if this concept was to be turned 'inside out', so that the power grid, the IO network and the heat extraction are in some senses *on the inside* of the devices which are being attempted to aggregate into arrays instead? The PTCA concept allows us to do exactly that. Indeed, these properties are a necessity for effective 3D tiling and as a result of those requirements some very interesting possibilities arise.

### C. POLYHEDRAL TILED COMPUTING ARRAYS

PTCAs are a potentially disruptive and unconventional paradigm for true 3D system assembly, which may address the challenges highlighted in the previous subsection in new ways based upon the principles of the mathematical characteristics of polyhedra (geometric structures capable of tiling in 3 dimensions). Adopting this theoretical foundation and applying those principles in the context of engineering choices required to construct such modules as tileable computing elements, leads us to the concept of the PTCA as examined in this paper.

PTCAs consist of a multiplicity of computing modules which, by virtue of their 3D shapes, can be abutted in one or more dimensions to create arrays. Such 3D geometrically defined shapes are known as polyhedrons. Earlier work investigating practical aspects of this concept focused upon planar hexagonal tiles (HexTiles), which could be assembled into multi-dimensional surfaces, including the truncated-octahedron form [1]. However the most recent work has focused upon complete polyhedral modules with three-dimensional properties, and particularly the truncatedoctahedron, which was recognized in work by Lord Kelvin (termed as Kelvin bubbles) as a highly efficient 3D packing shape [44], and is a singular permutahedron which may be uniformly tessellated indefinitely in any plane. The Weaire-Phelan scheme [45] is known to offer a provably better solution to Kelvin's problem, by using multiple different polyhedra. For convenience, truncated-octahedrons, when embodied as computational modules, are forthwith referred to as 'Kelvin Cores' or 'K-cores'. Both Kelvin and Weaire-Phelan forms can be envisaged as 3D tileable computing arrays, but K-cores require only a single core shape, which is advantageous for modular tiling.

Polyhedra are, of course, a widely known concept in mathematics, and there are also notable parallels in other fields on this topic with overlapping theoretical concepts as diverse as 3D tomography, theoretical geometry, and networks [37], [44], [45], [46], [47], [48], but a practical embodiment of such systems in the form of physically composable modular computing arrays has yet to be significantly explored. Part of the motivation for undertaking the work and research reported in this paper is to close that knowledge gap with the use of both theory, modeling, and practical engineering insights.

In hardware terms, a PTCA module will typically contain processing element(s), IO, and data storage components, with options including CPU, GPU, FPGA, TPU, SSD, neuromorphic processor, multi-ported shared memory, or indeed a combination of several elements, or perhaps even emerging technologies such as optical, quantum, or highly unconventional devices. Any of these module types can be combined to achieve heterogeneous arrays of high complexity. Nodes could also be selectively placed to act as local power reservoirs to enhance power distribution with a dynamically varying workload distribution, or as hub nodes within a grid to optimize traffic management, or even as assisted cooling nodes to improve cooling network behavior.

FIGURE 1. Lower order polyhedra. Left to right: tetrahedron, pentahedron, cube, octahedron, truncated-octahedron. Shapes are shown semi-transparent to expose geometry.

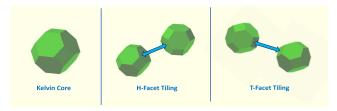

FIGURE 2. 'Kelvin Core' and facet tiling modes. Polyhedral shape (left), H-facet Tiling (middle) and T-facet tiling (right).

The full spectrum of regular and irregular polyhedra that might pack into some array-like structures is far too large to properly consider here. However there are some obvious choices that might be considered. Regarding our first question (core shapes and sizes), Figure 1 shows arguably the most obvious choices to consider as candidate polyhedra, including square and triangle-based pyramids, cube, diamond and other more complex shapes, and the truncated-octahedron. Figure 2 shows an example of the tiling modes of the truncated-octahedron.

The shapes presented are members of the sets of Platonic and Archimedean solids, with various efficiencies for packing into volumes of space [47]. In part, the answer is that a multitude of shapes can potentially be tiled in some respect [49], but how complete or efficient that packing may be, and how uniform that tiling occurs, is of great importance for genuinely practical systems assemblies. Additionally, the resulting physical topology of a particular packing scheme can be of great importance to the optimal mapping of logical topologies onto its physical structure. Highly incoherent or multivariate packing schemes are likely to be problematic in that respect.

Considering the suitability of these polyhedra as potential PTCA module candidates, and referring to Table 2, it can be observed that only the cube and truncated-octahedron provide rotational symmetry in the class defined here as 'simple', meaning that they can be uniformly packed into an infinitely large 3D array with only a single uniform orientation throughout. Pyramid and diamond have more complex packing attributes, which could/should require rotations of the shapes to achieve tiling and with tessellations at multiple scales. Thus, their base polyhedra form groups of larger and/or more complex polyhedra that are themselves tileable. For instance, some pentahedra may pack together to form rhombic dodecahedra, and these in turn may be tileable 'meta structures'. Although this does not prohibit their validity for PTCA solutions, this complexity is considered

TABLE 2. Basic properties of low order polyhedra.

| Polyhedron            | F-types | Neighbors | Symmetry | Packing |

|-----------------------|---------|-----------|----------|---------|

| Tetrahedron (Pyramid) | 1       | 3         | complex  | 0.78    |

| Pentahedron (Pyramid) | 2       | 4 (1+3)   | complex  | 0.95    |

| Cube                  | 1       | 6         | simple   | 1.00    |

| Octahedron (Diamond)  | 1       | 8         | complex  | 0.95    |

| truncated-octahedron  | 2       | 14 (6+8)  | simple   | 1.00    |

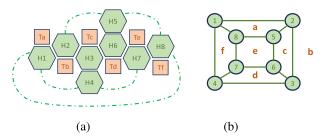

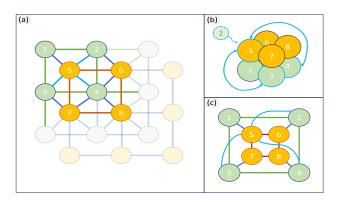

FIGURE 3. Kelvin core facet footprint and edge adjacency graph. This diagram represents (a) the unfolded form of the truncated-octahedron (Kelvin core), where trapezoidal T-facets and hexagonal H-facets have mutual adjacency. When this is translated into (b) a graph representation, it is possible to see how each facet adjoins its neighbors, and thus how each facet might communicate internally with other facets comprising the PTCA core module.

less convenient and potentially creates additional symmetry issues for the layout of facet connectors and makes array assembly a non-trivial task.

It is also apparent that some of the candidates have one facet type, while others have two or more. Notably, the simple cube, with six trapezoidal facets has many of the same properties as the corresponding six trapezoidal facets of the truncated-octahedron. This is of particular convenience as it permits most formulae relating to single packed array T-facet properties to be common to both polyhedra and also permits direct comparisons between the simple cube array forming a standard 3D mesh topology, a truncated-octahedron array forming the same topology in one instance and forming a partially bypassed 3D mesh in another tiling mode, as will be detailed later.

The neighborhood of each polyhedron, the number of other modules with adjacent facets when packed in a grid, indicates that the cube and truncated-octahedron are also more desirable in terms of a grid connectivity scheme with 6 and 14 unique neighbors respectively.

From an engineering point of view, when the facet footprint is 'folded' into a polyhedron, all facets are able to connect to all other facets internally via internal circuit pathways, which could be formed by internal PCB tracks. Figure 3 shows the facet adjacency graph and unfolded facet footprint. Figure 3(a) shows which H-facets are mutual neighbors, and the related adjacency graph in Figure 3(b) shows the connectivity between all hexagonal facets in the truncated-octahedron, which forms a  $(2 \times 2 \times 2)$  cube. It should be clear that the internal structure could therefore adopt a common power 'ring' which connects all power delivery facets to a common rail. This ensures that every core

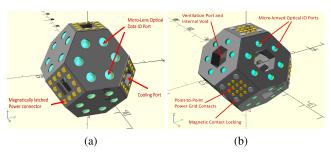

FIGURE 4. Kelvin cores with T-facet and H-facet venting schemes. These renderings show optical IO connections (the blue 'lens' areas on the hexagonal facets), but could utilize pogo pin or other IO data transfer mechanisms. Cooling vents represent entrances into the internal voids within the modules, which facilitate through-flow and internal thermal transfer from hot internal components into the circulating cooling medium (typically being air or liquid based). The number of IO ports and power pins is dependent upon the size of each facet within which they are located.

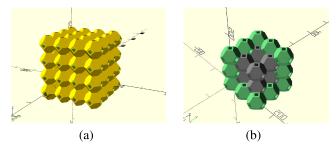

FIGURE 5. Example packing schemes as reported in [4]. (a) single packed grid (left) and (b) double packing example with a cutaway view (right) where gray cores are interleaved with green cores.

can act as a pass-through node to form collective power grids when composed into arrays, and can do so without any external supplementary power wiring or interconnect structures. In effect, the 3D module-to-module power grid is formed entirely by metal structures equivalent to a power bus or ring, but which are entirely internal to the modules. This reflects the earlier comment about PTCA having the advantage that cooling, IO, and power grids are all formed simply by abutting and tiling multiple modules into arrays.

It follows that the truncated-octahedron (K-core) in the envisaged PTCA is a highly relevant candidate for densely packed modular computing arrays. It also has two different facet styles which naturally tile together, as shown in Figure 2. There are 8 hexagonal and 6 trapezoidal facets (referred to here as H-facets and T-facets respectively). The primary focus in the remainder of this paper is the truncated-octahedron, and analysis of the characteristics and capabilities of such a module as a tileable computing element is also considered in terms of technical feasibility, with implications for potential performance.

# 1) FACET ADJACENCY AND PACKING SCHEMES

Connectivity between nodes is achieved where facets of individual polyhedra coincide and abut with each other in the packed grid. Figure 4 shows several conceptual variations of a Kelvin core, using different facet interface arrangements. The T-facet may provide both power and data connectivity via

**FIGURE 6.** Isomorphic equivalences. Case for a double packed truncated-octahedron array horizontal slice, where (a) shows a subsection of one layer of cores (green) and its interleaved double-packed layer (orange), (b) shows the isomorphic equivalent  $(2 \times 2 \times 2)$  cube, and (c) represents the node adjacencies.

abutment of adjacent cores in a point-to-point arrangement or operating in a pass-through bus arrangement, forming a global bus or a localized bus segment. H-facets can also operate in this mode. It is potentially valuable to consider specialization of facets, such that T-facets provide one function and H-facets another. For example T-facets are ideal for power network connection, and some forms of semiglobal routing. H-facets offer potential for highly connected data channels. As noted later, a third role of T- and H-facets relates to choices for system cooling.

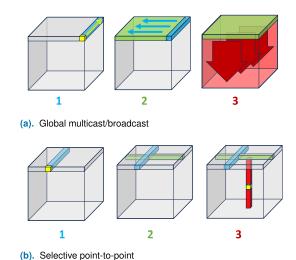

The tessellation of Kelvin cores is uniform, and results in two possible packing scenarios, as shown in Figure 5: scenario (a) involves only T-facet tiling, arranged in a *primitive cubic* mode, referred to here as a single-packed array, and (b) uses both T- and H-facet tiling in a *bodycentered* mode, (also known as a bi-truncated honeycomb) to pack additional Kelvin cores within the spaces created by an initial single-packed array. This is possible because the spaces between cores in the single packed scheme are the exact inverse of the volume of the Kelvin core itself, allowing complete packing. This structure equates to a skewed 3D mesh with additional hyper-connectivities, as visualized in Figure 6.

Notably, this structure (extended into 3D) also incorporates the hypercube topology as an isomorphic sub-graph. This can be extrapolated from the 2D Figure 6(a) where the green and orange nodes (labeled 1 to 4 and 5 to 8 respectively) form the two base squares of a hypercube, and with duplicate sets of nodes extending into layers above (assume corresponding labels 11 to 18) adding an identical pair of squares, linked by an associated vertical edge set such that node 1 connects to node 11, node 2 connects to node 12, and so-on. Thus two hyper-connected cubes are formed. It can be observed then that for the truncated octahedral array, it is possible to form extensible cube or hypercube arrays of cores that are themselves able to operate as 8-hex-facet cubic arrays.

More generally, there are four modes in which this dual-facet polyhedron can operate in a connective tiling:

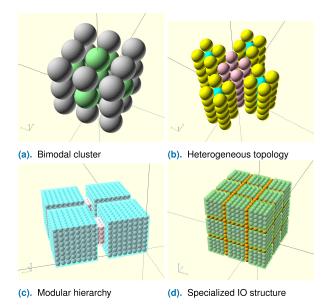

FIGURE 7. Examples of modularity and heterogeneity, where spheres represent kelvin-cores in these visualizations. Core dimensions are a design question, however assuming a quite conservative d=100mm, array dimensions would be as follows: (a)  $30 \times 30 \times 30cm$ , (b)  $60 \times 60 \times 50cm$ , (c)  $180 \times 180 \times 80cm$ , (d)  $140 \times 140 \times 140cm$ .

- A single-packed array using only T-facet interfacing, results in each core having six immediate connected neighbors. This is also directly equivalent to an array of simple cube-shaped modules.

- Double-packed arrays which restrict facet use only to T-facet connectivity would result in two interleaved but independent 3D meshes.

- Double packed arrays with only H-facet interfacing yields eight unique neighbors per core and a single unified grid.

- Double packed arrays employing both T- and H-facet interfaces, with up to 14 immediate unique neighbors per core, and forming a single unified grid.

Arguably, the single-packed Kelvin core arrangement has the same properties as a modular cube, packed to the same grid. However the Kelvin core case has significant space between nodes, and this forms a cooling void in the same way as abutted cores with internal flow vents, providing an additional cooling network (or an alternative if the cores are not themselves internally vented). It is also useful to note that the truncated-octahedron may pack in an intermediate mode where double packing of nodes can be selectively inserted across the grid according to custom computational criteria where machines are being built with highly specific applications. As noted in the next subsection, the internal functionality of each of the interleaved nodes may be one of many heterogeneous possibilities. There may simply be more primary compute nodes, configurable logic based accelerators, intermediary nodes primarily providing enhanced traffic distribution and management, redundant nodes to improve resilience, or indeed other custom purposes.

### 2) MODULAR HETEROGENEITY

A significant advantage of the PTCA paradigm is the ease of use of heterogeneity in array composition: a design factor emphasized as important by Becker et al. [14]. Tiled modules with externally standardized interfaces can thus have any desired internal specialization, but retain interchangeability, allowing both monolithic or heterogeneous array structures to be rapidly assembled with minimal custom design overheads. Likewise, the physical structure does not have to be as uniform as a cubic arrangement. Consider the illustrations in Figure 7, which show a few examples of heterogeneity, where different core colors represent types of specialized cores such as AI accelerators, GPUs, FPGAs, CPUs, SSDs, memory banks, neuromorphic cores, etc.

Figure 7(a) shows a bi-modal cluster: a combination of two core types in a small array which may represent two interspersed clusters of different device types (e.g. shared memory and CPUs), and could be a sub-grouping repeated across a larger array. Figure 7(b) shows a combination of custom topology and heterogeneous core types, and illustrates another key capability of PTCA systems: whereas cubic arrays are straightforward and in some terms 'general purpose', physical topologies can be constructed that place cores only where they are needed. They are therefore able to reflect aspects of the workload organization for one or more cases within a class of applications. In this case there are many permutations, the pink modules could be an SSD array, the blue modules could hold shared memory columns, and the yellow modules might be GPU nodes. Figure 7(c) highlights the ability of medium to large cubic PTCA arrays to be aggregated into larger systems, with modularity allowing scalable expansion and improved maintainability options. Finally, Figure 7(d) shows an array of sub-modular clusters (colored green) interspersed by planes of nodes envisaged to provide and manage a high-bandwidth many-channel data path between the modules (colored orange), and perhaps employing high radix cross-bar routing ICs at key positions within IO-plane intersections. Effectively this follows a 'many and moderate' rather than 'few and fast' data channels

It should be apparent that a complex hierarchical system can be composed in 3D with ease with the PTCA paradigm, a goal that would be more difficult at larger scales in a standard 2D rack-mount approach without a significant design effort around PCB design, bespoke and complex backplane IO arrangements, and other related design tradeoffs. PTCA therefore rapidly facilitates a significant diversity of such heterogeneous systems.

# 3) SYSTEM PROGRAMMABILITY

An obvious question with any kind of array structure might be – 'Is that array's programmability achievable with existing approaches, or do new approaches need to be devised?'.

It can easily be demonstrated that a single-packed PTCA array is a direct representation of a 3D mesh array, after all,

this is exactly what the structure represents if only the T-facets of neighboring modules abut to each other, and is then identical to an array of cubic modules arranged in the same 3D mesh structure. Since 3D mesh array programmability is widely used and understood as a logical topology, there is no need for new techniques to be developed; they already exist for problems that demand a 3D mesh logical topology solution space.

Folding and mapping techniques are well established for the translation of other logical topologies into mesh-array structures, and much work has been done on mapping structures such as tori into 3D processing arrays with guaranteed scalability [38], [39], [40], [41], [42].

When using double-packed arrays, it is still possible to demonstrate an equivalent 3D array topological structure for programmability. Consider again Figure 6, where it can be seen that the two interleaved array layers that form a double-packed array also create a 3D mesh: a 2D mesh slice is shown in Figure 6, but if this is duplicated in layers above and below, it becomes a 3D mesh. Again, with pre-existing models for programmability of logically 3D mesh topologies, there is no need for new programmability algorithms to be devised to exploit this structure.

Nonetheless, a double-packed array provides additional local connectivities between nodes that are not present in a standard 3D mesh – the hypercube connectivities mentioned earlier for example. This suggests that an enhanced approach to programmability could be beneficial, using existing 3D mesh methodologies but extending this to make optimal use of the links that permit localized packet routes, congestion, and hop-transitions to be bypassed and shortened. That work is beyond the scope of this paper, but quite feasible.

# 4) FAULT TOLERANCE AND MAINTAINABILITY

With regard to resilience, a key question is how to manage node failures in a large scale array. The first thing to consider is that when scaling to very large array sizes, a strategy that modularizes sub-groups of nodes, such as that illustrated in Figures 7(c), permits the down-time maintenance periods arising due to node failures to be typically limited to only the affected sub-group rather than the entire array, although this is still likely to be an inconvenience in general terms, and thus not a solution in itself.

In a rack-mount system, a node failure typically requires a rack module to be removed and swapped. Though an easy maintenance task, it also means potentially many nodes being removed and in some cases entire multi-node boards being scrapped when only a single node has failed. This can be ameliorated through socket-mounting of critical components but this adds cost and physical volume - there is a tradeoff here between extra up-front cost versus failure-rates and economic maintainability which needs to be balanced.

A strategy that could be exploited for PTCA nodes is that with circuit component positioning on the inside of each H-facet, as visualized in Figures 8 and 9, each node can potentially host multiple processing elements. Thus a degree of redundancy may be incorporated such that extra component cost can be traded off against reduced failure rates. For instance, with eight H-facets, a node might host four primary processing elements and four backups, making total node failure much lower in probability. Alternatively a node might use eight processing elements by default but throttle back workload capacity if individual processors fail. Designating perhaps six active processors as 'normal' operating capacity would maintain apparently normal operation in the presence of slowly accumulating failures.

A typical failure rate for many mainstream processors is often around 1 failure in 250,000 hours. For example, the Intel S1200V3RP Server Board has a MTBF (Mean Time Before Failure) of well over 350,000 hours, and the NVIDIA A100 GPU is anecdotally reported to have a MTBF of between 100,000 to 200,000 hours.

Given a constant failure rate  $\lambda$  for some unit time t, and also that the probability of failure  $P_{fail} = (1 - e^{-\lambda t})$ , it is possible to calculate how many failures will occur in a given period. Suppose that a system of 8,000 nodes is to operate quarterly maintenance schedules, and that each node in the system has a single processor with a MTBF of 200,000 hours. The probability of a node failure,  $P_{fail}$ , and the number of incidental failures during each quarter will then be as follows:

$$P_{fail} = 1 - e^{-[\frac{1}{200,000} \times \frac{8.760}{4}]}$$

= 0.01089(\approx 1.1%)

failures per quarter = 0.01089 \times 8, 000 \approx 87

This is approaching one failure per day on average, which is far from desirable for any HPC system, even if hot-swap racks are employed and the workload is able to accept and conveniently recover from such failures. However, reliability can be vastly improved by exploiting redundancy techniques.

Consider a PTCA node with a simple 1:1 active redundancy strategy, such that each node contains two processing elements, one of which is normally operational and the other is a normally idle backup device. It then becomes the case that both processing elements in a node must fail in order for that node to become non-operational - a much less frequent event in any given time frame. Assuming the same quarterly maintenance interval, the number of failures can now be determined as follows:-

$$P_{fail.dual} = (P_{fail})^2 = 0.0001185$$

failures per quarter =  $0.0001185 \times 8,000 \approx 0.95$

Therefore, the probability of one or more node failures between quarterly maintenance cycles can be substantially reduced, though it can never be completely eliminated. Recent and highly-relevant work by Takanami describes a number of strategies for tolerating failures in 3D grid arrays [43]. Such 'restructuring' and resilience strategies might include the following scenarios in the context of the described PCTA examples given in this paper:

- One, two or even more node failures may be tolerable for extended periods by redistributing workload to other nodes, thus allowing for maintenance to be scheduled at convenient and less disruptive intervals.

- Since every internal node in a Kelvin-core PTCA array

has 14 direct neighbors, even a full-node failure event

might be patched in a highly localized fashion by using

one of those 14 neighbor's spare processors to take on

the displaced workload.

It can reasonably be concluded that, although PTCA systems do not have the physical-maintainability convenience of standard rackmount systems based upon schemes such as fat-tree router networks, PTCAs can nonetheless be operated at large scales reliably with suitable design for redundancy.

Clearly, designing appropriate redundancy strategies and modes for continued but degraded performance are essential aspects of any large scale processing array. In the case of PTCA it is particularly important as the effort involved in swapping out faulty nodes is necessarily more complex. The cost-benefit trade-off therefore must balance maintenance and downtime costs against the cost of duplicating components for redundancy. This trade-off may well pivot around systems of a certain size and scale, as well as the level of heat stress and workload regime encountered in use. This is an area of work that could be fruitfully explored and modeled as a 'road map goal'.

The potential to enhance maintainability through hybrid architectural approaches is also noteworthy. A cluster of  $(8 \times 8 \times 8)$  node 3D sub-arrays, for instance, might be interconnected to other sub-arrays via more traditional fat-tree routing infrastructure for example, permitting each sub-array to be taken in and out of service relatively easily or even soft-swapped for a backup sub-array that is already in situ. This does of course reduce the full advantages of direct point to point connection in a uniform and contiguous 3D grid, but for certain applications this may be a desirable trade-off for enhanced maintainability.

### 5) COOLING GRIDS

As noted previously, one question this paper seeks to evaluate is whether power density and cooling is viable in a PTCA. There are two aspects to this:

- How can cooling be facilitated?

- Which range of power densities can be accommodated?

Cooling issues for tileable modules are fundamentally related to the configuration of a chosen module's facets and achievable packing regimes. Where packing schemes leave spaces between cores (as in the case of singularly packed K-cores), then a continuous cooling flow network is formed by that space. This might be adequate in its own right to provide a volume of air or fluid flow to achieve desired cooling demands. However, for the doubly packed K-cores, and indeed simple cubes, there are no spaces between cores. Instead each core will have an internal spatial void and external 'vents' which provide a path through the interior of

(a). Internal void space and flow

(b). Interior face of an H-Facet

(c). Conceptual cooling grid

(d). True cooling volume rendering

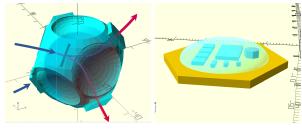

**FIGURE 8.** T-facet vented core cooling visualizations. Illustrating (a) interior void volume showing example of through-flow. Concave areas represent space occupied by (likely unpackaged) ICs, or MCM modules, located at interior plane of H-facets as shown in (b), where each H-facet can host complex circuitry. (c) Skeleton Cooling grid representation, (d) True volumetric view of cooling void with abutted cores. As for some previous figures, the individual core dimensions are a design parameter, and might feasibly be in the range  $60mm \le d \le 100mm$ .

the core to any other vent or external array surface. Singularly packed cores could also have internal venting if desired.

For K-cores this internal void-space will typically be of the order of 30-50% of the whole core volume for a double-packed scheme, and potentially 130-150% for single-packed schemes with spaces between cores. The vent location is an engineering decision, either T-facet or H-facet locations are suitable, though T-facets are preferred in this paper's analysis, as this means H-facets can host a larger multi-chip-module (MCM) with direct adjacency to external IO interface locations.

An example of the interior void volume formed in a T-facet-vented K-core is given in Figure 8(a), assuming an internal H-facet circuit design concept as shown in Figure 8(b) where components are mounted and bonded in a similar fashion to a Multi-Chip Module (MCM) or System-in-Package (SIP) with a thermally conductive encapsulation and/or heat-transfer structure.

The abutment of tileable cores in an array thus form a continuous internal void flowing through the entire array in multiple directions via T-facet vents, as shown in the topological representation of Figure 8(c). This forms a highly efficient directed cooling network for air or fluid flow with single- or double-packed cores. The true volume rendering is presented in Figure 8(d). Such a volume can exist inside K-cores in both single- and double-packed schemes, and a similar volume can be found between cores in the single-packed case (with or without internal cooling vents).

Such a fluid-flow system would be highly effective for heat removal and useful heat recovery as the PTCA

effectively forms a heat exchange labyrinth. In some senses, this solution sits somewhere between the two extremes of microchannels/microfluidics at the chip level and bulk immersive cooling systems at the other end of the spectrum, with various intermediate systems possible [8], [20], [21], [50], [51], [52], [53], [54]. Advanced implementations might conceivably combine macro and micro-cooling concepts in the same modular structure for example.

### 6) COOLING PARAMETERS AND MODELING

To help establish the viability of cooling, a critical factor of interest here is the area of the facet flow-vent aperture(s), which have influence over the flow capacity of any externally renewed air or fluid cooling system employed. A vent can be placed at a T-facet or H-facet, and the total area of each of these facets is calculated in the models presented later. This allows a determination of aperture area to be made while accommodating other facet constraints.

Ultimately, scalability in terms of cooling capacity relies upon too many factors to evaluate fully here. Several key considerations are the need for forced cooling flow models, and the impact of surface to volume ratios, as highlighted in earlier work [13]. Interestingly, the variance of surface to volume ratios with scale, once again highlights the relevance of earlier observations about allometric scaling as discussed and cited in Section II-B.

With the models presented, it is possible to determine both the flow capacity of channels, and the surface to volume ratios with a degree of accuracy. Future road-map directions must therefore include the use of fluid dynamics modeling to establish the impact of channel dimensions, flow turbulence, and intersecting flows under varied thermal loading scenarios. Relevant work in the field relating to modeling of complex flow systems and thermal heat transfer mechanisms, at the cabinet, module and component level, will beneficially inform this objective [22], [50], [52], [55], [56], [57], [58], [59], and could be adapted to this novel paradigm.

As a road-map goal, it is clear that a generic cooling model methodology is needed, ideally one which is able to adapt generally to other polyhedral modular compositions, i.e., a generic polyhedral volumetric flow model. This would be valuable as it could integrate with workload modeling to predict power density, thermal dissipation and workload interactions in large grids, not only assisting in identify where existing cooling technologies present limits to PTCA scaling, but perhaps also providing challenges for better future solutions to be conceived. Such models may also inform the possibility to distribute workload to minimize thermal hot-spots within a grid, i.e. thermally aware workload distribution and management.

# 7) FACET PHYSICAL CONNECTIVITY AND VIABILITY

Another question this paper seeks to address relates to the feasibility of connecting multi-dimensionally tiled objects and the feasibility of suitable connectors. The nature of the facet interfaces is an open design issue with many possibilities. Standard slot-in type connectors would be problematic when composing systems with three axes of tessellation, though not outside the scope of suitable innovation. Being able to slot in a device to other devices on three axes simultaneously with ease is, however, an engineering problem that is as yet not satisfactorily solved.

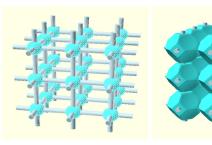

Considering alternatives, another approach is to use multiple parallel pogo-pin connections and magnetic couplings, and this has proven to be highly effective in our experimental work: reducing contact losses due to parallel resistance, multiplying electrical current capacities and reducing voltage losses. The reliability of these type of connectors is high. Manufacturers rate their products in the 10,000s to 100,000s of connect-disconnect (mating) cycles while retaining connection resistance and impedance within rated milliohm tolerances, and this is also corroborated by scientific studies of pogo pin resilience, behaviors under thermal stress, and other factors relevant to a high density system array [60], [61]. An advantage of PTCA is the ability to easily disassemble and reassemble systems, however it is very unlikely that such actions would be repeated many 1000's of times or more. Nonetheless, if necessary, pogo pins can be specified which tolerate high mating-cycle regimes.

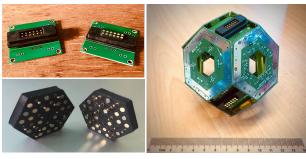

It can be concluded that polyhedral modules can connect to others in 3D with practical technology solutions, indeed this approach has been used in a number of prototypes, some examples of which appear in Figure 9, along with a concept for an advanced mass-production assembly methodology.

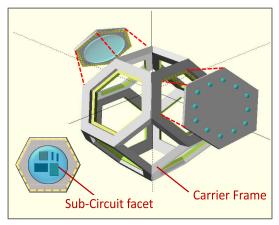

Practical core assembly is an important topic, since it will ultimately have engineering choices that may influence other design aspects. The scenario shown in Figure 9(c) treats H-facets somewhat like PLCC packaged IC modules that can retrofit into a carrier frame. PLCC techniques are well established and could easily be adapted to this form factor, and this would permit any combination of standardized sub-modules to be integrated during manufacture into a standard core frame, allowing a high degree of heterogeneity and specialization even within a single PTCA module.

This approach might use MCMs (multi-chip modules), stacked dies, and other currently evolving techniques. Bare die mounting on MCM substrates and system-in-package (SIP) techniques could allow a high degree of integration and enhanced cooling if encapsulated appropriately and yet would retain the ability to be economically mass-produced in volume.

The carrier frame itself would complete the internal IO pathways and common power grid continuity between T-facets, while the construction of the sub-modules could vary in sophistication from solutions relying upon edge-plated hexagonal PCB's hosting SMD components, through to IC dies bonded to a similar substrate as an MCM assembly. In the most advanced cases, highly integrated VLSI chips housed in hexagonal PLCC chip packages whilst additional optical IO ports and silicon-photonics elements are

(a) pogo-pin connectors

(b) K1 Prototype (internal)

(c) Mass-Production Assembly Concept

**FIGURE 9.** K1 prototype and possible module connectors. (a) Upper left: off-the-shelf connectors mounted on K1-P power boards; Lower left: custom 30-pin H-facet connector plate built by authors (max dia. 28mm: suited to a core of  $d\approx 50$  mm); (b) K1 prototype modular assembly showing bare module without housing covers  $d\approx 90$  mm. (c) Production assembly concept.

envisaged as a future evolutions of current chip packaging technologies.

Both power delivery and data IO connectivity may use the pogo-pin arrangement, which in the components shown in Figure 9 occupy only 4mm<sup>2</sup> of facet area each at standard separation. Data IO can also potentially use an opto-coupled arrangement with transmitter-receiver pairs arranged as opposing-facet components, assisted by micro-lens arrangements to aid coupling [62], [63]. A primitive version of the latter concept is used in prototype modules currently being developed as part of a validation project, a photo of which is also shown in Figure 9. Considering the metal-on-metal pogo-pin option, manufacturing data confirms feasibility of pogo-pin data-rates of 10 Gbps or more (e.g., USB 3.2 data lanes), though far inferior to the single-channel 50 Gbps delivered by infiniband HDR, this is pin-to-pin connect at very low hardware cost and can easily be paralleled to many channels if supported by appropriate chipsets.

Meanwhile, recent advances in co-packaged optics, directto-die waveguide bonding and integrated on-chip silicon photonics have significant potential while also eliminating issues with multi-lane parasitic signal effects that might be experienced in densely packed wired data lanes. Such technologies are capable of delivering data rates in the many tens of gigabits per second range and with increasing power efficiency, especially for very short range data transfer as envisaged here [63], [64], [65], [66], [67], [68], [69], [70], [71]. A particular emerging technology which achieves very high density multi-fibre IO parallelism, rather than fewer ultra-fast connections, could be very well suited to increasingly small PTCA core modules where high IO bandwidths per cm<sup>2</sup> and low energy per bit are key factors of interest [72]. On the whole, bespoke connector designs are becoming increasingly sophisticated, and there is much more to explore here, where multiple technologies might well be found in a single connector solution supported by a custom interface IC at each facet, combining data buffering/routing, integrated silicon photonics and data messaging protocols in a single 'wrapper' component. Then any desired components can be introduced as part of the core design.

Notably, all of the above techniques lend themselves to mass production at scale, with perhaps the exception of co-packaged optical interconnects, which is nonetheless a rapidly maturing field and expected to become an increasingly economic mass production option in the near future.

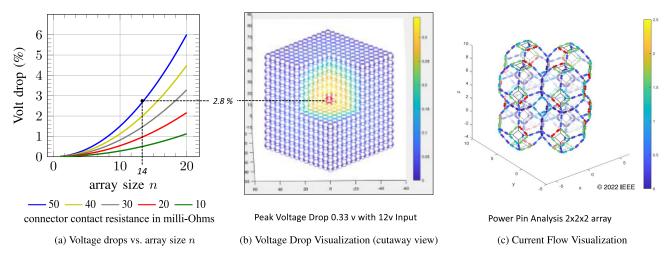

When one compares PTCAs to cabinet-based rack and backplane systems, it is clear that PTCAs compose densely packed modules into structures that directly reflect 3D system topologies, while forming data, power and cooling networks simply by the abutment of cores. The viability of such power grids has been validated through experimental prototype hardware test-beds and corresponding simulations of larger scale systems [1]. The feasibility of such systems can be demonstrated on that basis and by the mathematics of the system models to be presented in the next sections of this paper, which will allow a wide range of properties of such systems to be represented.

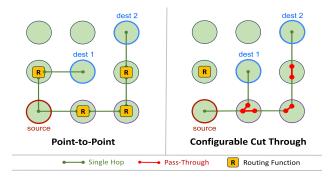

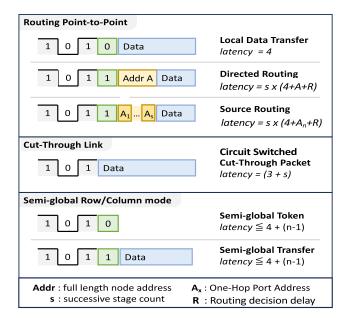

While PTCA facet IO schemes have an obvious asynchronous point-to-point capability, communications between more distant cores can be facilitated in a variety of ways, as explored in later sections. Facet-to-facet IO schemes may also designate IO pins to support clock domains for synchronous data transfer (e.g. one shared clock pin per abutted facet pair), and/or to support flow control for the whole facet IO channel group. This would allow reporting of the buffer status of the receiving channels to the sending facet and allow hardware flow control with no data loss.

In this relatively unexplored design space, there are clearly many possibilities and equally many unanswered questions. The challenge is that simply building a system is not a practical proposition until we have much clearer ideas about what choices to make in its design, and therefore the technologies and refinements required. Equally, simulations will only tell us how a system will perform based upon how we think we should construct it, or else ignore important questions about those aspects which might be critical for performance.

In this paper, a third approach is added, as described in the next section, using mathematical models to push into the design envelope to a degree that helps to establish feasibility,

**TABLE 3.** Single packed array characteristics.

| Symbol             | Equation                                                                               | Eq.                                                                                                                                                                                                                                                                |                                                      |

|--------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| $C_{TS}$           | $n^3$                                                                                  | (1)                                                                                                                                                                                                                                                                |                                                      |

| $V_S$              | $(n \times d)^{3 \text{ [tn 1]}}$                                                      | (2)                                                                                                                                                                                                                                                                |                                                      |

| $C_{ES}$           | $n^3 - (n-2)^3$                                                                        | (3)                                                                                                                                                                                                                                                                |                                                      |

| $C_{IS}$           | $(n-2)^3$                                                                              | (4)                                                                                                                                                                                                                                                                |                                                      |

| $T_{TS}$           | $6C_{TS}$                                                                              | (5)                                                                                                                                                                                                                                                                |                                                      |

| $H_{TS}$           | $8C_{TS}$                                                                              | (6)                                                                                                                                                                                                                                                                |                                                      |

| $T_{ES}$           |                                                                                        | (7)                                                                                                                                                                                                                                                                |                                                      |

| $H_{ES}$           | $24n^2 - 24n + 8$                                                                      | (8)                                                                                                                                                                                                                                                                |                                                      |

| $T_{IS}$           | $T_{TS} - T_{ES}$                                                                      | (9)                                                                                                                                                                                                                                                                |                                                      |

| $B_{TS}$           | $n^2$                                                                                  | (10)                                                                                                                                                                                                                                                               |                                                      |

| $P_{\mathrm{avg}}$ | $6p \div n$                                                                            | (11)                                                                                                                                                                                                                                                               |                                                      |

|                    | $C_{TS}$ $V_S$ $C_{ES}$ $C_{IS}$ $T_{TS}$ $H_{TS}$ $T_{ES}$ $H_{ES}$ $T_{IS}$ $H_{ES}$ | $\begin{array}{ccc} C_{TS} & n^3 \\ V_S & (n \times d)^3 \text{ [m 1]} \\ C_{ES} & n^3 - (n-2)^3 \\ C_{IS} & (n-2)^3 \\ T_{TS} & 6C_{TS} \\ H_{TS} & 8C_{TS} \\ T_{ES} & 6n^2 \\ H_{ES} & 24n^2 - 24n + 8 \\ T_{IS} & T_{TS} - T_{ES} \\ B_{TS} & n^2 \end{array}$ | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

$<sup>^{\</sup>mathrm{tn}\,1}\,d$  is the distance between two  $180^o$  opposing T-Facets.

practical engineering challenges, and refine the scope for future simulation studies. The expectation is that this allows a path for engineering, modeling, and simulation questions to converge upon a much better understanding of the PTCA concept and its future potential.

### III. MATHEMATICAL PROPERTIES OF CUBIC PTCA

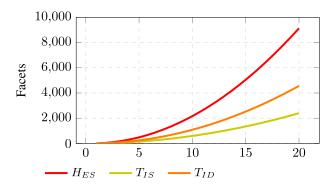

In order to assess the properties of PTCA systems, a set of mathematical equations are presented in Tables 3, 4, 5, and 6, relating to cubic arrays of single- or double-packed K-cores.

In a cubic K-core array, the key dimension n represents the number of cores visible across any outer edge of the cube. Therefore a cubic array of size n=4 would have all array cube faces showing  $4 \times 4$  visible outer cores, just as shown in Figure 5(a). Cuboids with differing values of n in the three key dimensions (height, width, depth) can also be subject to similar analysis, but are not presented here.

Tables 3 and 4 introduce formulae representing a range of system performance properties, but in addition there are dimensional parameters defined in Table 5, and formulae representing connectivity in Table 6. These equations can be used to facilitate first-order determinations of properties such as total system power, power density, data bisection bandwidth, peak connector current, ratios of internal to external IO bandwidth, maximum available power consumption per node, and many more metrics. As mentioned earlier, the single-packed array T-facet properties and equations relate to both the modular cube and the truncated-octahedron K-core, with the exception of  $T_{\rm side}$  and  $T_{\rm area}$ , where the cube has  $T_{\rm side} = d$  and  $T_{\rm area} = d^2$  respectively.

It might also be noted that containment volumes  $V_S$ ,  $V_D$  represent a cube incorporating the sized array, including wasted space at the bounding edges, since a packing efficiency of 100% is only achievable in an infinite space.

# A. FUNDAMENTALS

Some key fundamental properties of PTCA systems include the total number of cores in a given array size, and the number of internal and external cores. These properties are

**TABLE 4.** Double packed array characteristics.

| Attribute              | Symbol    | Equation            | Eq.  |

|------------------------|-----------|---------------------|------|

| Total Cores            | $C_{TD}$  | $n^3 + (n-1)^3$     | (12) |

| Containment Vol. $m^3$ | $V_D$     | $(n \times d)^3$    | (13) |

| External Cores [tn 1]  | $C_{ED}$  | $n^3 - (n-2)^3$     | (14) |

| Internal Cores [tn 1]  | $C_{ID}$  | $(n-1)^3 + (n-2)^3$ | (15) |

| Total T-facets         | $T_{TD}$  | $6C_{TD}$           | (16) |

| Total H-facets         | $H_{TD}$  | $8C_{TD}$           | (17) |

| External T-facets      | $T_{ED}$  | $6n^2 + 6(n-1)^2$   | (18) |

| External H-facets      | $H_{ED}$  | $24n^2 - 24n + 8$   | (19) |

| Internal T-facets      | $T_{ID}$  | $T_{TD} - T_{ED}$   | (20) |

| Internal H-facets      | $H_{ID}$  | $H_{TD}-H_{ED}$     | (21) |

| T Bisection factor     | $B_{TD}$  | $n^2 + (n-1)^2$     | (22) |

| H Bisection factor     | $B_{HD}$  | $4(n-1)^2$          | (23) |

| Avg Core Power         | $P_{avg}$ | $6p \div n$         | (24) |

$<sup>^{\</sup>mathrm{tn}\; 1}$  for  $n \leq 2,$   $C_{E^d} = C_{T^d},$  and  $C_{I^d} = 0$

**TABLE 5.** Key core dimensions.

| Attribute                   | Symbol         | Equation                                           | Eq.  |

|-----------------------------|----------------|----------------------------------------------------|------|

| T-facet side length [tn 1]  | $T_{ m side}$  | $d \div 3$                                         | (25) |

| T-facet area [tn 2]         | $T_{\rm area}$ | $(d \div 3)^2$                                     | (26) |

| H-facet maximal diameter    | $H_{ m dia}$   | $2d \div 3$                                        | (27) |

| H-facet side length         | $H_{ m side}$  | $d \div 3$                                         | (28) |

| H-facet circuit area [tn 3] | $H_{\rm area}$ | $\frac{3}{2} \times \sqrt{3} \times f(d \div 3)^2$ | (29) |

| Whole-core H-circ area      | $H_A$          | $8 \times H_{\text{area}}$                         | (30) |

$<sup>^{\</sup>mathrm{tn}\,1}\,T_{side}=d$  for modular cube.

TABLE 6. Hop count and neighbourhoods.

| Attribute        | Symbol   | Equation                               | Eq.  |

|------------------|----------|----------------------------------------|------|

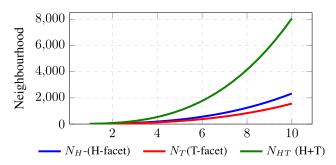

| Neighbours (H)   | $N_H$    | $(h+1)^3 + h^3$                        | (31) |

| Neighbours (T)   | $N_T$    | $(2h+1) \times (2h^2 + 2h + 3) \div 3$ | (32) |

| Neighbours (T+H) | $N_{TH}$ | $8h^3 + 6h + 1$                        | (33) |

| Max-h (Sngl)     | $M_S$    | 3(n-1)                                 | (34) |

| Max-h (Dble)     | $M_D$    | m-1                                    | (35) |

**note:** for double-packed cases, m represents the edge dimension for a double packed array, where m=2n-1, but note that the core count of a double-packed array is substantially larger than single, therefore direct comparisons using n values should be used cautiously.

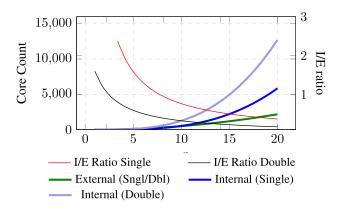

important for some basic considerations such as system size, raw GFLOPS, power delivery capacity and power per node limits.

A more subtle measure is the number of T- and H-facets visible at the array surface. This is the typical external entry point for power and IO connectivity into the grid, and for cooling flows. These equations take into account the location of cores placed at edges, corners and faces of the array.