Subscriber access provided by UNIV OF YORK

**Article**

# Paradigm of magnetic domain wall based In-memory computing

Xiangyu Zheng, Junlin Wang, Guanqi Li, Xianyang Lu, Wenjia Li, Yichuan Wang, Li Chen, Haihong Yin, Jing Wu, and Yongbing Xu

ACS Appl. Electron. Mater., Just Accepted Manuscript • DOI: 10.1021/acsaelm.0c00318 • Publication Date (Web): 07 Jul 2020

Downloaded from pubs.acs.org on July 13, 2020

#### **Just Accepted**

"Just Accepted" manuscripts have been peer-reviewed and accepted for publication. They are posted online prior to technical editing, formatting for publication and author proofing. The American Chemical Society provides "Just Accepted" as a service to the research community to expedite the dissemination of scientific material as soon as possible after acceptance. "Just Accepted" manuscripts appear in full in PDF format accompanied by an HTML abstract. "Just Accepted" manuscripts have been fully peer reviewed, but should not be considered the official version of record. They are citable by the Digital Object Identifier (DOI®). "Just Accepted" is an optional service offered to authors. Therefore, the "Just Accepted" Web site may not include all articles that will be published in the journal. After a manuscript is technically edited and formatted, it will be removed from the "Just Accepted" Web site and published as an ASAP article. Note that technical editing may introduce minor changes to the manuscript text and/or graphics which could affect content, and all legal disclaimers and ethical guidelines that apply to the journal pertain. ACS cannot be held responsible for errors or consequences arising from the use of information contained in these "Just Accepted" manuscripts.

Paradigm of magnetic domain wall based In-memory computing

Xiangyu Zheng<sup>1,2†</sup>, Junlin Wang<sup>1,2†</sup>, Guanqi Li<sup>2,3†</sup>, Xianyang Lu<sup>2,3</sup>, Wenjia Li<sup>1,2</sup>, Yichuan Wang<sup>2,3</sup>, Li Chen<sup>5</sup>,

Haihong Yin<sup>4,1\*</sup>, Jing Wu<sup>2,3\*</sup> and Yongbing Xu<sup>1,2\*</sup>

<sup>1</sup>Laboratory of Spintronics and Nanodevices, Department of Electronic Engineering, University of York, York, YO10 5DD, UK

<sup>2</sup>York-Nanjing International Center of Spintronics, School of Electronics Science and Technology, Nanjing University, Nanjing 210093, China

<sup>3</sup>Department of Physics, University of York, York, YO10 5DD, UK

<sup>4</sup>School of Electronics and Information, Nantong University, Nantong 226019, China

<sup>5</sup>School of Electronic and Electrical Engineering, University of Leeds, Leeds, LS2 9JT, UK

†These authors contributed equally to this work.

\*Corresponding author. E-mail: yongbing.xu@york.ac.uk, jing.wu@york.ac.uk, hhyin@ntu.edu.cn

### **ABSTRACT:**

While the conventional microelectronic integrated circuits based on the electron charge are approaching to the theoretical limitation in foreseeable future, next generation nonvolatile logic units based on electron spin have potential to build logic networks of low-power consumption. Central to this spin based architecture is to develop a paradigm for in-memory computing with magnetic logic units. Here we demonstrate the basic function of a transistor logic unit with patterned Y-shaped NiFe nanowires by gate-controlling domain wall pinning and depinning. This spin based architecture possesses the critical functionalities of transistors and can achieve a programmable logic gate by using only one Y-shaped nanostructure, which represents a universal design currently lacking for in-memory computing.

**KEYWORDS:** *In-memory computing, spin-based transistor, programmable nano-logic unit, domain-wall logic, permalloy.*

### 1. INTRODUCTION

Conventional microelectronic integrated circuits (ICs) based on complementary metal-oxide-semiconductor (CMOS) are experiencing its bottleneck. On contrast, Spintronics, which could replace CMOS or work alongside it in heterogeneous system, is rapidly evolving due to various breakthroughs in the study of spin quantum phenomena as well as huge industry demand in the last a few decades<sup>1</sup>. Motivated by this, a variety of concepts and spintronic devices have been proposed to overcome the limitation, knows as the memory wall, in which computation and storage are physically separated<sup>2</sup>. Instead of re-optimizing conventional integrated circuits, in-memory computing, which is a new revolutionary concept, aims to subvert the von Neumann architecture by *in-situ* calculations, where the data are located<sup>3</sup>. This new architecture, which has become the most attractive hot topic in the last decade, provides a straightforward advantage by totally eliminating the latency and energy burdens of memory wall<sup>2</sup>. Without any separation between the memory and computation, in-memory computing approach is very similar to the operation method of the human neurons networks<sup>4</sup>.

Various in-memory computing schemes have been proposed in both analogue and digital spaces<sup>2</sup> and these new architectures require capability that can compute and store data at the same time. The emerging nonvolatile computational memory techniques, such as resistance switching RAM (RRAM)<sup>5</sup>, phase change memory (PCM)<sup>6</sup>, magnetoresistive RAM (MRAM)<sup>7</sup>, and ferroelectric RAM (FeRAM)<sup>8</sup>, which have unique storage strategic rather than based on electronic charge, push the in-memory computing one step forward by reducing the 'distance' between computing and the data<sup>9</sup>. Digital computing by bipolar resistive switching<sup>10</sup> based on spintronic memory device offers several advantages over the nanomagnets<sup>11</sup> and quantum cellular automata <sup>12-14</sup> for in-memory digital computing. Analogue computing with crosspoint arrays is also applying computational memory technique such as RRAM<sup>15</sup> or PCM<sup>16</sup> to implement the in-memory computing. Another branch of in-memory computing is

investigating a magnetic logic architecture, referred to as "domain-wall logic" (DWL), where data are encoded along the magnetic nanowires. The DWL based on soft magnetic material such as Permalloy (NiFe) has been investigated for decades which has a strong potential to replace present logic gate <sup>17-20</sup>. In conventional DWL, however, a continuous rotation magnetic field is applied on logic units <sup>17, 21</sup> and output detection method based on MOKE signal is hard to integrate for in-memory computing. The chirality-encoded architecture has been proposed most recently<sup>20</sup> which has big advance on spin logic where data is encoded within the structures and carried by continuous stream. The limitation of this chirality-encoded architectures, however, is that the output chirality was not totally correlated to the input switching order<sup>20</sup>. Previous researches on DWL just focus on the function of the logic gate, and there is rare investigation of the combination of magnetic logic unit and memory. Here, we demonstrate the development of a new paradigm of in-memory computing by using the ability of DWL to calculate in memory.

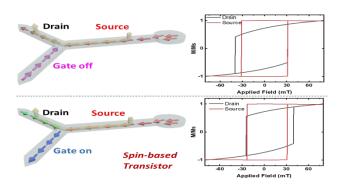

Central to this work is representing a phenomenon in specific design of DWL based on Y-shaped magnetic nanostructure which shows the similar function of a transistor in the circuit. The transistor inside the CMOS ALU (arithmetic logic unit) has a 'Gate' terminal which determines the conductivity of this device (as shown in Figure 1a and b). Inspired by this, we have designed a Y-shaped nanowire (as shown in Figure 1d) to implement the similar function of a conventional semiconductor transistor. The 'Gate' arm has the same effect as the 'insulated gate' in the transistor. The magnetization direction of this 'Gate' arm (restricted arm) controls the domain propagation process of the 'Drain' and 'Source' arm (switching arms)<sup>22</sup>. The domain wall pinning and depinning state in Y junction corresponds to 'gate on' and 'gate off', respectively, at the same input condition (as shown in Figure 1e). By controlling different magnetization states of three arms, several basic Boolean logic functions can feasibly perform under two input signals. Based on this phenomenon, a programmable logic gate with functions

including OR/NAND/XOR is achieved within only one nanostructure. Furthermore, comparing with the conventional CMOS-Based computer architecture (as shown in Figure 1a), this DWL can either process input signals or store output results that breaks the physical separation between the memory and computing. Instead of reading data and writing back process, spin-based logic is stored and operated in memory with a single writing instruction (as shown in Figure 1c). After receiving the instruction, a series of input signals will change the spin state of three arms, which is called the calculation stage. Subsequently, at the memory stage, the spin state is stored in two switching arms. There are two different spin states, namely "head to head" (domain wall exists) and "head to tail" to yield different outputs <sup>23-25</sup> (operations are illustrated in Figure 1e). This ingenious architecture, which combines ease of fabrication and integration for in-memory computing, fills the gap in the simplification of complex logic gates either in a conventional integrated circuit or the previously proposed DWL<sup>17, 19-20, 26</sup>.

# 2. EXPERIMENTAL SECTION

The Y-shaped nanowires were made from the magnetically soft Permalloy (Ni<sub>80</sub>Fe<sub>20</sub>) by e-beam lithography. Magnetization analysis was performed with a magneto-optical Kerr effect (MOKE) image system<sup>27</sup>. The successive images were taken at each applied in-plane sweep magnetic field in 1.44mT steps. The MOKE result was extracted from the average of 5 times full loop sweep signal. Same experiment was repeated for three times. Figure. 1d shows a SEM image of Y-shaped nanostructure with one nucleation pad (maximum width 6 $\mu$ m, maximum length 10 $\mu$ m). The angle between the three arms of Y-shaped nanowire are equal to 120°. 'Drain' arm and 'Gate' arm are 1 $\mu$ m width, 27 $\mu$ m length (from joint to the tail), and 'Source' arm is 1 $\mu$ m width, 32 $\mu$ m length. For the nanowire design, the large ratio of length to width can yield strong shape anisotropy enough to overcome the driven magnetic field to ensure the functionality of nanowire device.  $H_{sat}$  ( $\pm$  350mT) indicates initial applied saturated field along 'Gate' arm ( $x - \theta'$  ( $\theta' = 60^\circ$ )) and an orthogonal external field  $H_a$  (the range of

change is -350mT to 350mT) is then exerted along the  $x + \theta$  where  $\theta$  is 30°(Detailed of other experimental results about the 'Gate' arm controlled are analyzed and presented in the Supporting Information, Section S4).

#### 3. RESULTS AND DISCUSSION

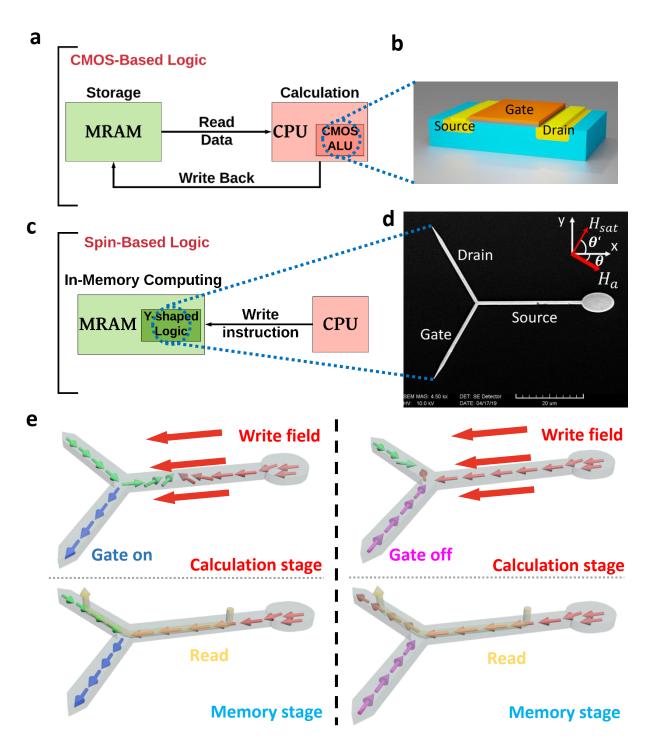

Figure. 2 represent the Kerr contrast images and continuous magnetization progress within the structure. Before the Kerr imaging, the sample was first saturated at magnetic field  $H_{sat}$  as an initial state. And subsequently a continuous sweeping magnetic field  $H_a$  is applied to the sample along  $(x + \theta)$ . Under the sweeping magnetic field which started from negative to positive and sweeping back, the magnetization state of entire device is changing via applied external field. Eight images (Figure. 2a to d and f to i) experiencing different applied field were picked up from the whole process. The magnetization reversal first occurs at nucleation pad and then the domain wall formed between the arm and the nucleation pad is pushed along the 'Source' arm (Figure. 2a). The domain wall passes the joint after depinning and subsequently moves to the terminal of 'Drain' arm (Figure. 2b), leading to a magnetization direction reversal of the 'Drain' arm. Due to the strong magnetic shape anisotropy in narrow FM (ferromagnetic) wire, the magnetization direction (magenta arrow shown in Figure 2a to d) of the 'Gate' arm is restricted to be directed parallel to the wire axis under orthogonal magnetic field  $H_a$ . Two switching arms experience different magnetization process under magnetic field sweep back from positive to negative (as shown in Figure. 2c and b). After the domain wall leaves the nucleation pad, it propagates from 'Source' arm to 'Drain' arm without pinning, meanwhile 'Gate' arm remains its magnetization direction pointing from the terminal to joint. In the opposite spin state (blue arrow shown in Figure 2f to i) of the 'Gate' arm, the 'Drain' arm and 'Source' arm exhibit opposite magnetization process at the same experimental method. The domain propagates from 'Source' arm to 'Drain' arm without pinning appeared during negative to positive field (Figure. 2f and g). And domain wall pinning occurred during positive to negative field (Figure. 2h and i).

For easy observation, we combine the hysteresis loops taken from 'Source' arm and 'Drain' arm under sweeping magnetic field showing in Figure. 2e. A significant different coercivity (approximately 15mT) of the 'Source' and 'Drain' arm can be clearly observed from Figure. 2e under a positive magnetic field. This coercivity bias indicates asymmetric magnetization of the 'Drain' and 'Source' arm. Comparing with Figure. 2e, an opposite offset coercivity around 19mT can be observed under a negative external field at the opposite spin state of 'Gate' arm as shown in Figure. 2j. This asymmetric magnetization process shows that the spin state of the 'Gate' arm determined by the external magnetic field can control the magnetization of the 'Drain' arm, which has the similar function of a transistor in the conventional circuit.

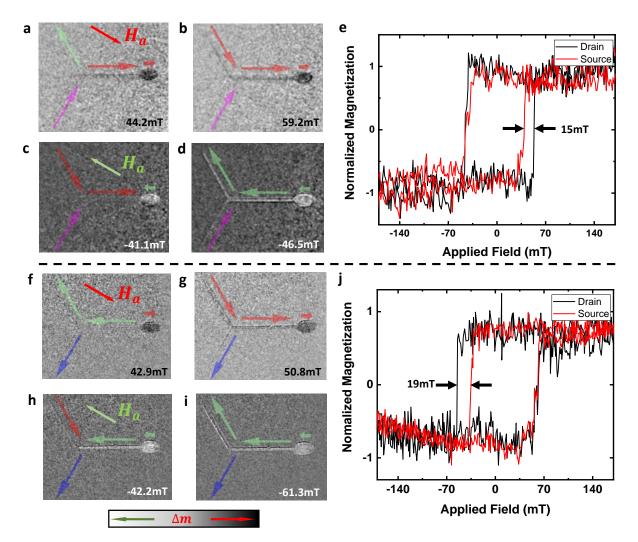

To gain understanding of the domain-wall motion within the nanowire in detail, we performed quasi-static micromagnetic simulations of the Y-shaped nanostructure with one nucleation pad showing in Figure. 3 (Detailed of other simulation results are analyzed and presented in the Supporting Information, Section S3). The micromagnetic simulations are performed by Mumax3 simulation package (reference). The parameters of the device material in the micromagnetic simulation are given as blow, the exchange stiffness  $A_{ex} = 13 \times 10^{-12}$  j/m, the crystalline anisotropy constant  $K = 0j/m^3$ , saturation magnetization  $M_s = 8.6 \times 10^5$  A/m and for the quasi-static simulations the Gilbert damping constant  $\alpha = 0.5$ . The cell size for the 2D micromagnetic simulation is  $5 \text{ nm} \times 5 \text{ nm} \times 20 \text{ nm}$ .

The simulation results showed that the domain switching process is similar to the function of the transistor. For the domain-wall pinning situation (Figure. 3a), there is a transverse domain-wall generated at the junctions showing in the enlarge image. Meanwhile,

the magnetizations along the 'Gate' to 'Drain' arm and 'Gate' to 'Source' arm are the head-to-tail. Thus, the domain depinning needs to overcome an energy barrier. Further increasing the applied field, the transverse domain-wall overcomes the barrier and propagate to 'Drain' arm (Figure. 3b). Under opposite magnetic field, three arms appeared to have head-to-head domain configurations with the domain-wall approaching to the junction. This led the domain wall to propagate directly along an easy magnetization direction to 'Source' arm, where 'Gate' arm is a hard magnetization axis along the external field due to strong shape anisotropy (Figure. 3c and d). Since the device was applied sweeping magnetic field, the initial and final magnetization state are totally same (as shown in Figure. 3d and i). The hysteresis loops which extracted X-axis magnetization from one pixel state at two arms (Figure. 3e) show a red square loop ('Source' arm, parallel to the X-axis) and a gray oblique loop ('Drain' arm, an 60° angle with X-axis). This result indicates that an asymmetric magnetization process takes place on the 'Drain' arm, which is exactly the same as the experimental observation.

Instead of applying  $H_{sat}$  as an initialization in the simulation, opposite magnetic field  $-H_{sat}$  was also applied to set up the initial state. As external field  $-H_{sat}$  applied along the 'Gate' arm, the magnetization direction along this arm is from joint to the terminal which shows the blue background in Figure. 3f. The same sweeping magnetic field was applied to this simulation, however, the directly propagation process appeared first (Figure. 3f and g) and subsequently domain-wall pinning state (Figure. 3h and i) occurred under reversed field condition. Comparing with pervious simulation hysteresis loop (Figure. 3e), Figure. 3j represents the opposite asymmetric magnetization process due to a reversed initial spin state of 'Gate' arm. Detailed simulation results are analyzed and presented in the Supporting Information, Movies S1 and S2.

According to these simulation and experiment result, the magnetization direction of 'Gate' arm and the 'Source' arm, which is directly connected with nucleation pad, plays a

decisive role in this transistor-like magnetic nanostructure. Our simulation results (figure.3a to d and f to i) indicate that the gate arm magnetization impacted by the external magnetic field and it's not exactly along the arm axis. This switching behavior of 'Gate' arm is attributed to the result of both external magnetic field and shape anisotropy. Since the asymmetric results mainly come from the along or opposite magnetization directions of the 'Source' and 'Gate' arm (such as head-to-tail or head-to-head), therefore, a slightly changes in the direction of the 'Gate' arm magnetization will not significantly affect the functions. The simulation results represent agreements to the experimental phenomenon under large amount of repeated experiment summarized. This Y-shaped nanostructure with the required functionality observed reliably shows the feasibility to develop logic unit or integrated logic networks. Here we propose several significant logic units which has strong potential to enhance the value of inmemory computing.

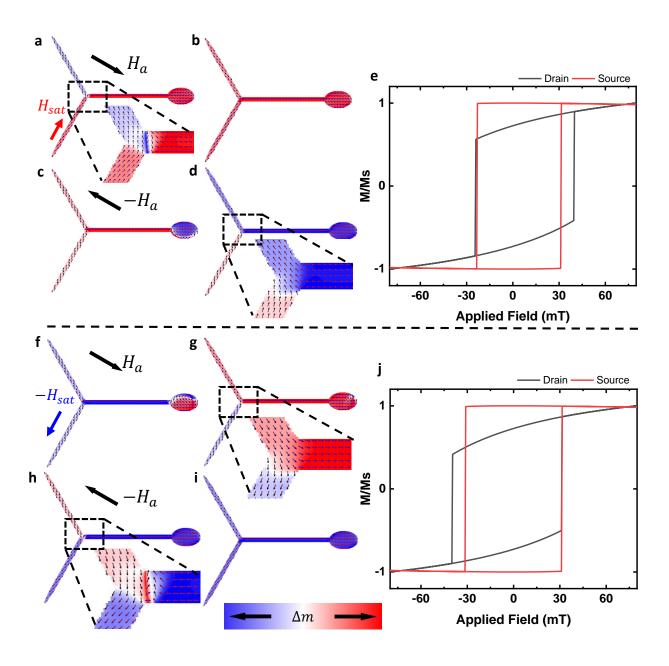

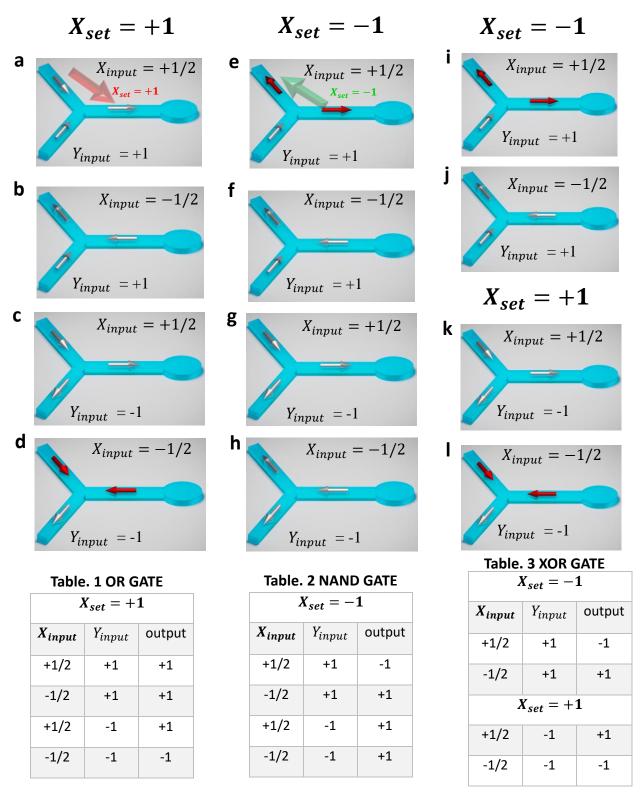

Based on the observed transistor-like phenomenon, we propose a feasible programmable logic gate, where a universal design based on just one nanostructure is still lacking. The operating principles of magnetic programmable logic gate are illustrated in Figure. 4. The key characteristic is that the output exhibits two different conductivity states for high ('1') or low ('-1') under two input external fields, where the two arms have different spin states due to the asymmetric magnetization process within the nanowire. The input signal  $Y_{input}$  (same with  $H_{sat}$ ), along the  $x - \theta'$  ( $\theta' = 60^{\circ}$ ) which should be the first input (Detailed of inputs order are analyzed and presented in the Supporting Information, Section S4), saturates the 'Gate' arm and controls its magnetization direction ( $H_{sat}$  refer to '1' and  $-H_{sat}$  refer to '-1'). Subsequently, a set saturated field  $X_{set}$  that set to '1' ( $x + \theta$ ) or '-1' ( $-(x + \theta)$ ), which initializes the magnetization of arm 'Source' and 'Drain' to same direction (head to tail magnetization state), can be used to control the logic gate selection. Finally, a  $X_{input}$  along the ( $x + \theta$ ) or ( $-(x + \theta)$ ) with '1/2' magnitude (the specific value depends on the specific

structure) apply to this DWL. Here we illustrate three different logic gates function within one nanostructure.

OR GATE. We select the saturated field  $X_{set}$  to '+1' to implement the OR logic gate (Figure. 4a to d). Noticeably,  $Y_{input}$  should first input to this nanostructure, otherwise it will impact the magnetization of other two arms. Each time after the  $Y_{input}$  applied, the saturated field  $X_{set}$  set the 'Drain' arm and 'Source' arm to the same state. And subsequently  $X_{input}$  is applied to complete a cycle of logic calculation. Detecting the conductivity between the 'Drain' arm and 'Source' arm, we get the same function of OR gate representing in the Table. 1. Due to the asymmetric magnetization process, the domain wall is pinned at the junction (Figure. 4a) where represents low conductivity because of domain wall (Tail-to-Tail) existed at joint under both 'high' input of X and Y. Same direction of  $X_{input}$  and  $X_{set}$  cause no changing of two arms' magnetization (Head-to-Tail) (Figure. 4b and d) which exhibit high conductivity. Figure. 4c indicates the fast propagation process when 'low'  $Y_{input}$  and 'high'  $X_{input}$  are applied, and same magnetization direction along the 'Drain' arm and 'Source' arm. As summary, only 'high' input of both X, Y can yield 'low' output under the 'low'  $X_{set}$  setting saturated field.

**NAND GATE**. When '-1' of  $X_{set}$  setting saturated field was selected, this programmable magnetic logic gate switches to the NAND function (Figure. 4e to h). With the same input signal applied to this nanostructure, we can only get the 'low' output under both 'low' input of X, Y. This function represents the same logic of NAND gate and true table shows in Table.2.

**XOR GATE**. Different from pervious logic gate, the XOR function can be implemented under two opposite  $X_{set}$  setting saturated fields (shown as Figure. 4i to l). The  $Y_{input}$  can trigger the direction of  $X_{set}$ . A corresponding opposite setting saturated field should be activated when  $Y_{input}$  is 'high' or 'low'. Due to the asymmetric magnetization, the output

represents same function of XOR gate that gives a true (high) output when the number of true inputs is odd. And true table exhibits in Table. 3. This XOR gate is a combination of part of OR gate and NAND gate. As shown in the Table. 3, the  $X_{set}$  and  $Y_{input}$  are bound, which means the  $X_{set}$  only related to  $Y_{input}$  in XOR gate state. In the real operation, the  $X_{set}$  and  $Y_{input}$  are executed by a same field driver that represent a single input but control opposite applied magnetic field directions.

Furthermore, if we detect the resistance state of two arms rather than the conductivity, the relative 'high' and 'low' value will be reversed. And this programmable logic could be extended three more logic functions. When '+1' of saturated field  $X_{set}$  is selected, the OR gate becomes AND gate due to the fact that all high inputs yield high output. And NAND gate is transferred to NOR because all low inputs yield high output under '-1' setting field  $X_{set}$ . Due to the opposite function, the XOR becomes NXOR where the same inputs yield high output. For translating the input signal to magnetic field, the extra field drivers is necessary. The value of '1' or '1/2' refer to the magnitude of external field and they are fixed by each field driver. When the Y-shaped nanostructure is running, the driver switches the direction of the magnetic field according to the input digital signal 0 or 1 (- or +). Therefore, swapped the inputs will not violate the truth table and keep output value correct which satisfy the two inputs should be equivalent and commutable.

In general, this novel nanostructure can implement various Boolean logic functions and thus a real feasible spintronic programmable logic unit could be achieved. In this research, the external magnetic field and MOKE signal detection are the main investigation method. Further improvements could be achieved by patterned electrical contacts nanowire as an input pulse source<sup>20, 28-29</sup> and patterned electrical pads as a detector of domain-wall electrical resistance<sup>23-24, 30</sup>. In addition, we have designed another Y-shaped nanostructure with two nucleation pads which has been investigated by the same method (Detailed of other experiment and simulation

results are analyzed and presented in the Supporting Information, Section S1 to S3). These two nucleation pads nanostructure was found to have the advantage of consuming less energy.

#### 4. CONCLUSIONS

In this article, we report a transistor-like phenomenon occurred in Y-shaped magnetic nanostructure and demonstrate its functions by MOKE imaging and micromagnetic simulations. Based on the asymmetric magnetization process, we propose a feasible paradigm for in-memory computing programmable logic gate, which can reduce significantly the complexity and area of conventional logic circuits. Utilizing the characteristic of DWL for both storage and calculation, in-memory computing can be implemented more efficiently and directly. To further implement the paradigm of the magnetic domain wall based in-memory computing, one may need to combine with one of these newly developed memory techniques including chirality-encoded DWL<sup>20</sup>, STT-MRAM<sup>31</sup>, Magnon-driven spintronic devices<sup>32</sup>. While the gating-controlled operation of the Y-shaped magnetic nanostructure as demonstrated in this work provides an underlying framework for the in-memory computing architecture, significant efforts are still needed to address the interdisciplinary challenge of integrating spintronic ALU for calculating data and memory for storing data to achieve the practical in-memory computing.

# **Supporting Information**

Detailed device fabrication process; SEM image of the Y-shaped nanostructure with two nucleation pads; Detail experimental and simulation results of the Y-shaped nanostructure with two nucleation pads including MOKE images and *Mumax3* results; Input order analysis of the different Y-shaped nanostructure; Simulation animation of the Y-shaped nanostructure with one nucleation pad (Movies S1-S4).

#### **ACKNOWLEDGMETNS**

This work is supported by National Key Research and Development Program of China (Grant No. 2016YFA0300803), the National Natural Science Foundation of China (Grant No. 61427812, 11774160), the Natural Science Foundation of Jiangsu Province of China (No. BK20192006), the Fundamental Research Funds for the Central Universities (Grant No. 021014380113),

## **REFERENCES**

- (1) ITRS. Beyond CMOS. 2015.

- (2) Ielmini, D.; Wong, H. S. P. In-memory computing with resistive switching devices. *Nature Electronics* **2018**, *1* (6), 333-343.

- (3) Di Ventra, M.; Pershin, Y. V. The parallel approach. Nature Physics 2013, 9 (4), 200-202.

- (4) Indiveri, G.; Liu, S.-C. Memory and Information Processing in Neuromorphic Systems. *Proceedings of the IEEE* **2015**, *103* (8), 1379-1397.

- (5) Waser, R.; Aono, M. Nanoionics-based resistive switching memories. *Nat Mater* **2007**, *6* (11), 833-40.

- (6) Raoux, S.; Welnic, W.; Ielmini, D. Phase change materials and their application to nonvolatile memories. *Chem Rev* **2010**, *110* (1), 240-67.

- (7) Kent, A. D.; Worledge, D. C. A new spin on magnetic memories. *Nat Nanotechnol* **2015**, *10* (3), 187-91

- (8) Mikolajick, T.; Dehm, C.; Hartner, W.; Kasko, I.; Kastner, M. J.; Nagel, N.; Moert, M.; Mazure, C. FeRAM technology for high density applications. *Microelectron Reliab* **2001**, *41* (7), 947-950.

- (9) Wong, H. S.; Salahuddin, S. Memory leads the way to better computing. *Nat Nanotechnol* **2015**, *10* (3), 191-4.

- (10) Linn, E.; Rosezin, R.; Tappertzhofen, S.; Bottger, U.; Waser, R. Beyond von Neumann--logic operations in passive crossbar arrays alongside memory operations. *Nanotechnology* **2012**, *23* (30), 305205.

- (11) Niemier, M. T.; Bernstein, G. H.; Csaba, G.; Dingler, A.; Hu, X. S.; Kurtz, S.; Liu, S.; Nahas, J.; Porod, W.; Siddiq, M.; Varga, E. Nanomagnet logic: progress toward system-level integration. *J Phys Condens Matter* **2011**, *23* (49), 493202.

- (12) Cowburn, R. P.; Welland, M. E. Room temperature magnetic quantum cellular automata. *Science* **2000**, *287* (5457), 1466-8.

- (13) Imre, A.; Csaba, G.; Ji, L.; Orlov, A.; Bernstein, G. H.; Porod, W. Majority logic gate for magnetic quantum-dot cellular automata. *Science* **2006**, *311* (5758), 205-8.

- (14) Gavagnin, M.; Wanzenboeck, H. D.; Belic, D.; Bertagnolli, E. Synthesis of individually tuned nanomagnets for Nanomagnet Logic by direct write focused electron beam induced deposition. *ACS Nano* **2013**, *7* (1), 777-84.

- (15) Jo, S. H.; Kim, K. H.; Lu, W. High-density crossbar arrays based on a Si memristive system. *Nano Lett* **2009**, *9* (2), 870-4.

- (16) Kau, D.; Tang, S.; Karpov, I. V.; Dodge, R.; Klehn, B.; Kalb, J. A.; Strand, J.; Diaz, A.; Leung, N.; Wu, J.; Lee, S.; Langtry, T.; Chang, K. W.; Papagianni, C.; Lee, J.; Hirst, J.; Erra, S.; Flores, E.; Righos, N.; Castro, H.; Spadini, G. A stackable cross point phase change memory. *Int El Devices Meet* **2009**, 617-20.

- (17) Allwood, D. A. Submicrometer Ferromagnetic NOT Gate and Shift Register. Science 2002, 2003-6.

- (18) Atkinson, D.; Allwood, D. A.; Xiong, G.; Cooke, M. D.; Faulkner, C. C.; Cowburn, R. P. Magnetic domain-wall dynamics in a submicrometre ferromagnetic structure. *Nat Mater* **2003**, *2* (2), 85-7.

- (19) Hesjedal, T.; Phung, T. Magnetic logic element based on an S-shaped Permalloy structure. *Applied Physics Letters* **2010**, *96* (7), 072501-1-3.

- (20) Omari, K. A.; Broomhall, T. J.; Dawidek, R. W. S.; Allwood, D. A.; Bradley, R. C.; Wood, J. M.; Fry,

- P. W.; Rosamond, M. C.; Linfield, E. H.; Im, M. Y.; Fischer, P. J.; Hayward, T. J. Toward Chirality-Encoded Domain Wall Logic. *Advanced Functional Materials* **2019**, *29* (10), 1807282-1-9.

- (21) Allwood, D. A.; Xiong, G.; Faulkner, C. C.; Atkinson, D.; Petit, D.; Cowburn, R. P. Magnetic domainwall logic. *Science* **2005**, *309* (5741), 1688-1692.

- (22) Ahn, S. M.; Moon, K. W.; Cho, C. G.; Choe, S. B. Control of domain wall pinning in ferromagnetic nanowires by magnetic stray fields. *Nanotechnology* **2011**, *22* (8), 085201.

- (23) Lepadatu, S.; Xu, Y. B. Direct observation of domain wall scattering in patterned Ni80Fe20 and Ni nanowires by current-voltage measurements. *Phys Rev Lett* **2004**, *92* (12), 127201.

- (24) Lepadatu, S.; Vanhaverbeke, A.; Atkinson, D.; Allenspach, R.; Marrows, C. H. Dependence of domain-wall depinning threshold current on pinning profile. *Phys Rev Lett* **2009**, *102* (12), 127203.

- (25) Berger, L. Analysis of measured transport properties of domain walls in magnetic nanowires and films. *Physical Review B* **2006**, *73* (1), 014407-1-5.

- (26) Atkinson, D.; Eastwood, D. S.; Bogart, L. K. Controlling domain wall pinning in planar nanowires by selecting domain wall type and its application in a memory concept. *Applied Physics Letters* **2008**, *92* (2), 022510-1-3.

- (27) Schafer, R. Investigation of Domains and Dynamics of Domain Walls by the Magneto-optical Kerreffect. **2007**, 1-29.

- (28) Hayashi, M.; Thomas, L.; Rettner, C.; Moriya, R.; Parkin, S. S. P. Direct observation of the coherent precession of magnetic domain walls propagating along permalloy nanowires. *Nature Physics* **2006**, *3* (1), 21-25.

- (29) Hayashi, M.; Thomas, L.; Bazaliy, Y. B.; Rettner, C.; Moriya, R.; Jiang, X.; Parkin, S. S. Influence of current on field-driven domain wall motion in permalloy nanowires from time resolved measurements of anisotropic magnetoresistance. *Phys Rev Lett* **2006**, *96* (19), 197207-1-4.

- (30) Xu, P.; Xia, K.; Gu, C.; Tang, L.; Yang, H.; Li, J. An all-metallic logic gate based on current-driven domain wall motion. *Nat Nanotechnol* **2008**, *3* (2), 97-100.

- (31) Ikeda, S.; Miura, K.; Yamamoto, H.; Mizunuma, K.; Gan, H. D.; Endo, M.; Kanai, S.; Hayakawa, J.; Matsukura, F.; Ohno, H. A perpendicular-anisotropy CoFeB-MgO magnetic tunnel junction. *Nat Mater* **2010**, *9* (9), 721-4.

- (32) Wang, Y.; Zhu, D.; Yang, Y.; Lee, K.; Mishra, R.; Go, G.; Oh, S.-H.; Kim, D.-H.; Cai, K.; Liu, E.; Pollard, S. D.; Shi, S.; Lee, J.; Teo, K. L.; Wu, Y.; Lee, K.-J.; Yang, H. Magnetization switching by magnon-mediated spin torque through an antiferromagnetic insulator. *Science* **2019**, 1125-1128.

# **Table of Contents**

**Figure 1.** (a) Schematic diagram of conventional CMOS-Based architecture. (b) The conventional transistor used in integrated circuits. (c) The new design of spin-Based Inmemory computing implemented Y-shaped logic can be stored and calculated with only one write instruction. (d) SEM image of transistor-like permalloy Y-shaped nanowire with one nucleation pad. Three arms correspond to the 'Drain', 'Source' and 'Gate' of conventional transistor. The red arrows showing at right top indicate the external in-plane magnetic field

directions of  $H_{sat}$  and  $H_a$ . (e) Schematic diagrams of operation to a Y-shaped nanowire both in calculation stage and memory stage. Left diagrams illustrate that when the 'Gate on', the domain wall pinned at the joint during write field, and the read process will detect a higher conductive at memory state. Conversely, lower conductive will be detected by the read current at same write field due to the 'Gate off' showing on the right diagrams.

Figure 2. Contrast images show two opposite magnetization process of Y-shaped nanowire with one nucleation pad at two different Gate states (a to d and f to i). Contrast here was generated by dividing the two different initial state image  $(m_1)$  by the specific image  $(m_x)$  resulting in a magnetization distribution  $\Delta m = m_1/m_x$ . Various colour arrows represent the magnetization direction along the three arms and nucleation pad that assist the reader's interpretation of the contrast. (e) and (j) are longitudinal MOKE signal taken from 'Drain' arm and 'Source' arm corresponding to black and red hysteresis loop show an asymmetric magnetization process. Approximately 15mT pinning field occurred during the process of the sweep field from negative to positive showing in (e). And approximately 19mT pinning field occurred during the process of the sweep field from positive to negative showing in (j).

Figure 3. A series of simulation results (a) to (d) showing the detail of magnetization process for Y-shaped nanowire at initial saturated field along  $y + \theta$  for  $H_{sat}$ . (f) to (i) represent magnetization process under same sweeping magnetic field condition at opposite  $-H_{sat}$  saturated field as initialization. The enlarge figures of simulation results indicate more details of magnetization direction inside the junction. (e) and (j) Hysteresis loop taken from two pixels at 'Drain' arm and 'Source' arm corresponding to  $H_{sat}$  and  $-H_{sat}$  saturated field.

**Figure 4.** (a) to (d) exhibit the operation principle of OR gate. Under the '+1'  $X_{set}$  saturated field, the output represents low when only both high inputs come, and Table. 1 illustrates the true table of this magnetic OR gate. (e) to (h) illustrate the operation principle of NAND gate. A low output yield when the both low inputs apply under '-1'  $X_{set}$  saturated field. The

functions show in the Table. 2. (i) to (l) represent the operation principle of XOR gate.  $Y_{input}$  trigger the different  $X_{set}$  saturated field state. Output gives high when the number of true inputs is odd which exhibit in the Table. 3.