# UNIVERSITY OF LEEDS

This is a repository copy of A Reduced-Wire ICE Catheter ASIC With Tx Beamforming and Rx Time-Division Multiplexing.

White Rose Research Online URL for this paper: http://eprints.whiterose.ac.uk/139147/

Version: Accepted Version

# Article:

Jung, G, Tekes, C, Rashid, MW et al. (5 more authors) (2018) A Reduced-Wire ICE Catheter ASIC With Tx Beamforming and Rx Time-Division Multiplexing. IEEE Transactions on Biomedical Circuits and Systems, 12 (6). pp. 1246-1255. ISSN 1932-4545

https://doi.org/10.1109/TBCAS.2018.2881909

(c) 2018 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

## Reuse

Items deposited in White Rose Research Online are protected by copyright, with all rights reserved unless indicated otherwise. They may be downloaded and/or printed for private study, or other acts as permitted by national copyright laws. The publisher or other rights holders may allow further reproduction and re-use of the full text version. This is indicated by the licence information on the White Rose Research Online record for the item.

## Takedown

If you consider content in White Rose Research Online to be in breach of UK law, please notify us by emailing eprints@whiterose.ac.uk including the URL of the record and the reason for the withdrawal request.

eprints@whiterose.ac.uk https://eprints.whiterose.ac.uk/

# A Reduced-Wire ICE Catheter ASIC with Tx Beamforming and Rx Time-Division Multiplexing

Gwangrok Jung, Student Member, IEEE, Coskun Tekes, Member, IEEE, M. Wasequr Rashid, Thomas M. Carpenter, David Cowell, Member, IEEE, Steven Freear, Senior Member, IEEE, F. Levent Degertekin, Senior Member, IEEE, and Maysam Ghovanloo, Senior Member, IEEE

Abstract—This paper presents a single chip reduced-wire active catheter application-specific integrated circuit (ASIC), equipped with programmable transmit (Tx) beamforming and receive (Rx) time-division multiplexing (TDM). The proposed front-end ASIC is designed for driving a 64-channel 1D transducer array in intracardiac echocardiography (ICE) ultrasound catheters. The ASIC is implemented in 60 V 0.18-µm HV-BCD technology, integrating Tx beamformers with high voltage (HV) pulsers and Rx front-end in the same chip, which occupies 2.6×11 mm<sup>2</sup> that can fit in the catheter size of 9 F (<3 mm). The proposed system reduces the number of wires from >64 to only 22 by integrating Tx beamformer which is programmable using a single low-voltage differential signaling (LVDS) data line. In Rx mode, the system uses 8:1 TDM with direct digital demultiplexing (DDD) providing raw channel data which enables dynamic Rx beamforming using individual array elements. This system has been successfully used for B-mode imaging on standard ultrasound phantom with 401 mW of average power consumption. The ASIC has a compact element pitch-matched layout, which is also compatible with capacitive micromachined ultrasound transducer (CMUT)-on-CMOS application. This system addresses cable number and dimensional restrictions in catheters to enable ICE imaging under magnetic resonance imaging (MRI) by reducing radio frequency (RF) induced heating.

Index Terms—Medical ultrasound imaging, time division multiplexing, capacitive micromachined ultrasound transducers (CMUT), intracardiac echocardiography (ICE).

#### I. INTRODUCTION

NTRACARDIAC echocardiography (ICE) has become an important clinical modality in interventional ultrasound

Manuscript received July 16, 2018; revised xyz.... This work was supported in part by the National Institutes of Health under grants EB015607 and HL121838.

Gwangrok Jung, F. Levent Degertekin\*, Maysam Ghovanloo\* are with the School of Electrical and Computer Engineering at the Georgia Institute of Technology, Atlanta, GA 30308, USA (\*co-corresponding authors, email: levent@gatech.edu, mgh@gatech.edu).

F. Levent Degertekin are with the School of Mechanical Engineering at the Georgia Institute of Technology, Atlanta, GA 30332, USA.

Coskun Tekes is with School of Computer Engineering at the Kennesaw State University, Marietta, GA 30060, USA.

M. Wasequr Rashid is with Impinj Inc., Seattle, Washington, USA.

T. M. Carpenter, D. Cowell and S. Freear are with the School of Electronic

and Electrical Engineering, University of Leeds, Leeds LS2 9JT, U.K. Copyright ....

imaging [1], [2]. It requires a minimally invasive procedure with local anesthesia to place a catheter in the right side of the heart to guide interventions like valve repair, placement of stents, closure of atrial septal defects (ASD), and catheter-based ablation to treat atrial fibrillation [3].

Current commercial ICE catheters offer a 2D or limited 3D field of view in spite of large number of interconnections, which are mainly determined by the number of array elements and ground connections. Each element in the ICE array is connected to the analog-front-end (AFE) residing in an external ultrasound system with a separate long flexible wire, which is a significant limitation for improving image quality and increasing the number of elements. Also, in order to use ICE catheters under MRI instead of the ionizing X-ray radiationbased angiography, the number of interconnect wires in the catheter should be decreased to reduce RF-induced heating of the conducting lines to acceptable levels and the catheter tip should be visible [4], [5]. Reducing the number of connections by integrating electronics at the catheter tip would improve the overall system performance by capturing the receiver signals with higher fidelity, and transmitting them to the backend using higher quality cables which reduce the spurious interference present in the catheterization labs. Cable reduction would also improve the mechanical flexibility of these single use catheters, and possibly lower the cost. Therefore, integrating electronics at the catheter tip would have a significant impact in the catheter-based ultrasound imaging applications.

When designing the integrated systems on a chip for imaging application, ideally the quality of the resulting images should not be compromised while improving other aspects such as the cable count. In the application considered here, 64 element 2D imaging ICE catheter, to preserve the image quality, the raw data from each channel (without pre-combining signals from multiple array elements) should be available in the backend as in the current ICE catheters. That enables dynamic receive (Rx) beamforming techniques to be applied without limitations. The transmit (Tx) and Rx aperture size should be maximized making use of the full width of the catheter so that the image resolution and penetration depth are not compromised [6]. This requires Tx beamformer be integrated along with the Rx circuitry on the chip using a high voltage (HV) process and connected to the backend system with small number of cables

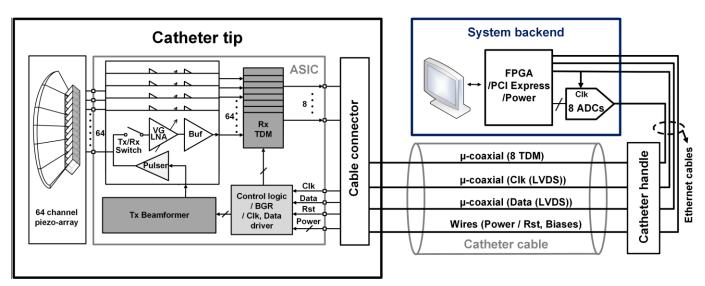

Fig. 1. Simplified block diagram of the proposed ICE catheter system which includes backend system.

and use the same maximum array area. Furthermore, the layout of the chip should be such that it is suitable for cable interconnect within the size limitations of the catheter tip. This paper demonstrates the first implementation of such an integrated system that combines a single cable programmable Tx beamformer and provides raw Rx data with 8:1 time division multiplexed receiver frontend for cable reduction.

On the Rx side, time division multiplexing (TDM) with direct digital demodulation (DDD) is used in this work as it provides -35 dB or below electrical crosstalk between channels with  $\mu$ -coax cables suitable for ICE imaging [7]. This figure can be further reduced by digital signal processing techniques [8]. Noting that in current miniature ultrasound systems, electrical crosstalk below -25 dB is acceptable [9], TDM emerges as a viable and simple option as compared to more robust but more complex and power consuming digital data transmission. Frequency division multiplexing (FDM) also has been shown to be feasible to provide raw channel data for ICE application [10]. However, this approach requires multiple analog filters and mixers that are vulnerable to process variations, which will increase the mismatch and complexity of the system. Another common method to reduce the number of wires in ultrasound systems on the receiver side is subarray beamforming ( $\mu$ -beamforming) [11]. Recent implementations of this method include a switched-capacitor-based delay and addition of an on chip digitizer and digital line driver [12]. Another digital subarray beamformer uses  $\Delta\Sigma$  modulator [13]. However, this system requires high frequency operation (960 MHz), which is difficult to feed into long interconnects in catheter-based applications, and limits integration of HV Tx circuits with thick gate oxide on a single chip. Note that these systems do not utilize the full aperture for Tx and Rx or do not integrate the Tx beamformer electronics which can be challenging to integrate with low voltage digital electronics. Furthermore, subarray beamforming methods inevitably compromise imaging performance as compared to a fully sampled array targeted here due to limited steering angles and angular directivity of the subarrays, which does not provide raw data information [14].

2

As mentioned above, the more critical aspect of cable reduction is single chip integration of the Tx beamformer at the catheter tip. Without Tx beamformer integration, only Rx cable reduction does not result in a practical imaging system. Single chip integration is essential to have a system size suitable for a catheter with a short rigid section at the tip. Single chip integration avoids complex through wafer vias for stacking chips and simplifies acoustic design. There are few examples of fully integrated Tx beamformer/Rx frontend systems. A system with more than 3000 transducer elements has been realized with Tx/Rx capability using subarray beamforming [15]. However, this system is developed for hand held probes to be used outside of the body. Other systems suitable in size for catheter implementation utilize subarray beamformers resulting in compromise in image quality and system complexity as noted by others [3] [12]. Other approaches to Tx beamformer implementation either require the number of cables proportional to the number of elements [16] with an external counter, or the beamformer has limited operation ability by only firing one pulse for each channel [17]-[19]. Another on-chip beamformer with integrated counter was presented in [20], however, it still requires multiple control signals to generate pulse for each channel.

In this paper, we describe a single chip solution for 2D imaging ICE catheter system, which limits the ASIC design to 9 F (<3 mm width) in size, and less than 0.5 W of power as the main constraints. The proposed ASIC adopts 8:1 TDM with DDD and Tx beamforming circuit requiring a single low voltage differential signaling (LVDS) data line for cable reduction. This paper is organized as follows. Section II describes the proposed system architecture including brief explanation of backend system. The details of the Tx ASIC level operation is provided in Section III, and the Rx operation is described in Section IV. The electrical measurements and acoustic experiments are presented in Section V. Further

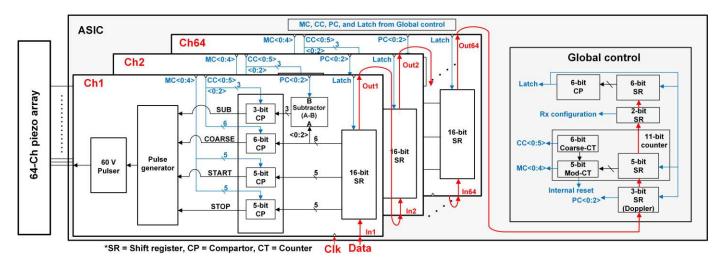

Fig. 2. Detailed block diagram of the Tx-beamformer.

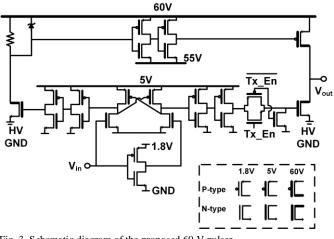

Fig. 3. Schematic diagram of the proposed 60 V pulser.

discussion is presented in Section VI with comparison with the recent state-of-art before concluding in Section VII.

#### II. SYSTEM ARCHITECTURE

In a conventional ICE catheter system, each of the piezoarray elements at the catheter tip is connected to the AFE system of the mainframe using a long conducting line. To reduce the number of wires, the proposed system uses an ASIC at the catheter tip to implement the Tx beamformer and Rx TDM circuits in a single chip. Fig. 1 shows the simplified block diagram of the proposed ICE catheter system. Each 1D piezotransducer array element is driven by a HV pulser, which can generate up to 60 V unipolar pulse, appropriately delayed based on the beamforming profile by the integrated beamformer. A Tx/Rx switch is located between pulser and Rx circuits to protect low voltage (LV) devices during Tx operation. Variable gain low noise amplifier (LNA) compensates for the attenuation of reflected echo signal by adjusting its gain to implement time gain compensation (TGC).

Eight sets of 8:1 TDM circuitry reduce the number of output signals from 64 to 8, and the high frequency (HF) buffers drive the TDM signals via Ethernet cables to the backend system.

The ADC in the backend system samples the corresponding channel at the right time. A key feature of the TDM in this system is the clock synchronization between the external ADC and multiplexer in the ASIC, details of which will be described in the next section. In this system, 64 channels of piezo-array elements are used to interface with the ASIC in this proof-ofconcept implementation. This array can be directly mounted on top of the front-end ASIC using flip-chip bonding or PZT-on-CMOS integration for future implementation [3], [12]. The proposed ASIC is also designed to be compatible with capacitive micromachined ultrasound transducer (CMUT)-on-CMOS application, where the array is fabricated directly over the CMOS wafer using a low temperature process [21].

3

The catheter cable consists of a mixture of  $\mu$ -coax cables (200 MHz of clock, data, TDM output signals) and single wires to deliver power lines, biases and control signals. After the catheter cable, the TDM signals are amplified via catheter handle to be sent across the long Ethernet cables to ADCs in backend system, where DDD is performed in the FPGA for advanced imaging processing in the digital domain [7].

The backend system consists of a custom ADC board to support 8 TDM signals, FPGA board, and power supply module. It also employs filters, AC-DC converters, DC-DC converters, and a PCI express card, which delivers data from the FPGA to a personal computer via optical fiber.

#### III. TX BEAMFORMER AND PULSER DESIGN

#### A. Design and Operation of Tx Beamformer

The proposed Tx beamformer uses a single LVDS data line to load the beamforming profile for 64 channels. It creates a maximum delay of  $10.235 \,\mu$ s with a resolution of 5 ns, using an 11-bit global counter. This maximum delay enables steering the ultrasound beam over the desired  $\pm 45^{\circ}$  field of view. The beamformer is designed to generate different pulse-width for each channel to control the Tx bandwidth and enable pulsewidth apodization, which improves ultrasound image quality by suppressing the side lobe effects [22]. Also, it can generate multiple pulses up to 8, for narrow band higher SNR operation in pulsed Doppler mode. It also can change the pulse repetition

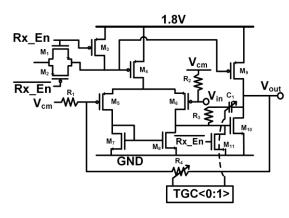

Fig. 4. Schematics of variable gain LNA.

frequency during Doppler mode operation.

Fig. 2 shows the detailed block diagram of Tx beamformer. In global control logic block, there is an 11-bit global counter that consists of 6-bit course counter (CC) and 5-bit mod counter (MC). During the data loading sequence, the initial value of 6-bit CC is fixed to 111111<sub>2</sub>, and the counter starts counting down to  $00000_2$  to find the coarse delay of each channel, while the 5-bit MC can be programmed to set the exact start time, width of a pulse, and number of pulses for each channel. Each of 64 channels has 16-bit serial-in parallel-out (SIPO) shift register that stores delay and pulse width information, respectively. Top 6-bit shift register is used to check proper data loading by comparing the value with 111111<sub>2</sub>. Once the data is loaded properly, the latch signal locks the shift registers and the counters start to count for pulse generation. A 2-bit shift register is used for Rx gain control configuration, and the last 3 bits of the shift register store the number of pulses for Doppler operation. Each channel has a 3-bit subtractor, which is used to keep track of how many pulses are fired during each transmitting cycle. Each channel has a 19-bit comparator that can calculate the exact beamforming profile to deliver LV pulses to the input of pulser.

To program the delay profile for all of the 64 channels, each programming cycle requires a 1040-bit data packet ( $64 \times 16+2$  +3+5+6), which corresponds to 5.2  $\mu$ s. Before programming the Tx beamformer, all shift registers are reset to set initial values, following which the data packet is generated and sent from the FPGA in the backend system through the high speed Ethernet cables.

#### B. Design and Operation of HV Pulser

Ultrasound pulse generator, aka pulser, is one of the key building blocks of any ultrasound imaging system, which drives ultrasound transducers, such as piezoelectric transducer or CMUT with HV output swing to create a pressure pulse. Recent literature shows several pulse-level shifting techniques to overcome limited supply voltage such as voltage doubler or multi-level pulse generator in ultrasound application [23], [24]. However, these approaches require multiple control signals and occupy significant area, such that integrating them in the ICE catheter becomes challenging.

In this system, a digital pulser is implemented using 60 V

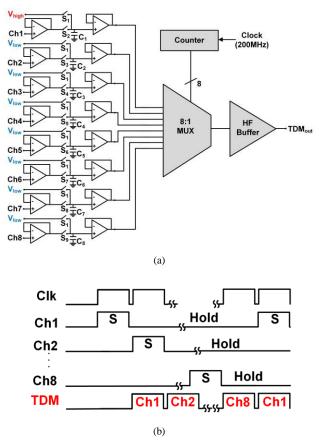

Fig. 5. (a) Simplified block diagram of TDM block for 8 channels, and (b) TDM sampling clock diagram.

double-diffused metal oxide semiconductor (DMOS) transistors, as shown in Fig. 3. The input of pulser is generated from Tx beamformer with 1.8 V supply. The pulser shifts this signal to 5 V<sub>pp</sub> to have enough input swing for DMOS transistors, and finally drives the output node with 60 V pulse. It is crucial to ensure that all devices in the circuit are operated in their safe operating conditions throughout the pulse cycle, considering the fact that in this process, the drain-source junction breakdown and gate-oxide breakdown voltages are 60 V and 5 V, respectively. Considering that P-type DMOS transistor occupies larger area compared to the N-type DMOS transistor due to additional guard rings, a 1.3 k $\Omega$  resistor is used in level-shifter stage with protection Zener diode which has 5 V of breakdown voltage. This level shifter is designed to limit the peak current to 5 mA from 60 V supply by adding an external 55 V supply and 5 V buffer chain, avoiding voltage drop across 6.7 mm on-chip power routing. The pulser is designed to drive 15 pF of capacitive load at 7 MHz with 60 V pulses, which is the equivalent capacitance of comparably large sized piezoelectric 1D ICE array.

#### IV. RX CIRCUITRY DESIGN FOR CABLE REDUCTION

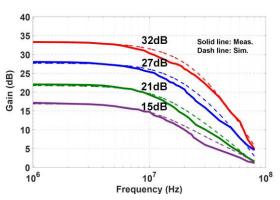

Simplified schematic of the AFE is shown in Fig. 1. 64 channels of Rx circuitry consists of Tx/Rx switch, variable gain LNA, buffer and TDM circuitry. The LNA design assumes an input echo signal dynamic range of 76 dB, and the gain of Rx

circuitry is set to compensate the attenuation by 4 stages (15 dB, 21 dB, 27 dB, and 32 dB) to meet the dynamic range of ADC in the backend system. During the Tx mode, Tx/Rx switch protects LV circuits from HV pulses. Variable gain LNA amplifies the echo signal based on the traveling depth for compensation, the buffer drives the amplified signal to TDM circuitry, and finally TDM circuitry samples and combines the output signals with 8:1 ratio to the backend system. The key blocks are described in detail below.

#### A. Design and Operation of Variable Gain LNA

Rx front-end topology in ultrasound system usually depends on the electrical impedance of ultrasound transducer type. The transimpedance amplifier (TIA) is a commonly used topology in CMUT application because the equivalent electrical model of CMUT has comparably high impedance [12]. For implementing the AFE for piezoelectric array, LNA structure is preferred because of relatively low impedance of piezoelectric elements [25]. Considering the area efficiency, and the fact that in this process capacitors occupy larger area than resistors, and for minimizing the shift of pulse-echo response to lowerfrequencies, a resistive feedback LNA structure was selected for this system [26]. Also, instead of implementing LNA and time gain control (TGC) circuit separately, we adopted a variable gain LNA structure.

Fig. 4 shows the schematic diagram of variable gain LNA structure. The gain is controlled by 2-bit TGC control bits through data line, which is generated by the external FPGA. The Miller compensation capacitor,  $C_1$ , is also controlled by TGC signal to push the second pole of this 2-stage op-amp well beyond the closed-loop bandwidth to keep phase margin above 60° in every gain stage of LNA. Rx\_EN signal and switch transistors (M<sub>1</sub>, M<sub>2</sub>, and M<sub>11</sub>) are required for power saving mode during Tx data loading period.

#### B. Design and Operation of TDM Circuitry

The TDM technique has been frequently used in communication systems to reduce the number of outputs [27], [28]. This approach allows multiple channels to share the same cable by assigning a corresponding time slot to each channel. Analog TDM requires a relatively simple design and less power because it needs an analog multiplexer and digital counting logic in addition to sample and hold circuits, which is suitable for compact ICE application. Also in this proposed system, by using DDD technique, the ADC can sample TDM output signals using the same frequency as the TDM circuitry in the ASIC. This results in less data processing to increase efficiency in the backend system [7].

The Tx target center frequency of this system is around 7 MHz, and the 3 dB fractional bandwidth is assumed as 80%, especially in the case of CMUT array, which usually has broader bandwidth than a piezoelectric array. This bandwidth requires a sampling rate more than 20 MS/s considering the Nyquist requirement. In this system, the clock frequency is chosen as 200 MHz, resulting in 25 MS/s for each channel of 8:1 TDM circuitry. To minimize the TDM cross-talk level due to inter symbol interference, the HF buffer is designed to have more than 400 MHz bandwidth. The TDM circuitry consists of 8 sets of TDM blocks, and each TDM block consists of 8 channels of sample and hold switches, link training switches,

Fig. 6. Link training waveform of (a) channel number synchronization, and (b) phase synchronization.

analog 8:1 multiplexer, and high frequency buffer, as shown in Fig. 5(a). The TDM block is designed and placed symmetrically using H-grid clock distribution to reduce the mismatch. The counter logic generates sampling clocks and the analog multiplexer selects signals for corresponding channel after 1 period of clock, which keeps track of which channel is to be connected, as shown in Fig. 5(b).

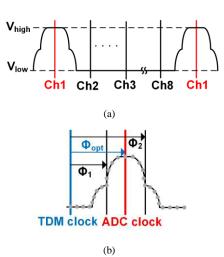

A critical part of the DDD is the clock synchronization between the TDM analog multiplexer in the ASIC and the ADC in the backend system with the same frequency. For this reason, the system requires two training sequences before TDM block starts working. One is channel number synchronization, and another is clock phase synchronization. These training sequences are called "link training" to ensure that the samples are correctly digitized in the backend system. During the link training process, first channel is connected to a fixed voltage level, Vhigh, while other channels are connected to another lower fixed voltage, V<sub>low</sub>, by adding another switch in parallel with the sample and hold switch for each channel, as shown in Fig. 5(a). During this operation,  $S_1$  is connected and all the other switches from  $S_2$  to  $S_9$  are open that the corresponding timing of channel 1 can be detected during demultiplexing in the backend system. By performing this step, the timing of the first channel of each TDM block can be ensured so that the order of channel timing is determined, as shown in Fig. 6(a).

The clock phase synchronization is used to ensure that the ADC and TDM multiplexer clocks are correctly phase synchronized to compensate for the propagation delays in the cabling. This is important as one needs to make sure that the ADC takes the samples when the signal through the interconnection has stabilized rather than during the switching transients. The TDM clock phase can be adjusted using a phase-locked loop (PLL) in the FPGA to determine the optimum phase shift, as shown in Fig. 6(b). The phase of TDM clock is changed with 78 ps steps until channel 1's half maximum points are found, such as  $\Phi_1$  and  $\Phi_2$ . These two points show when the switching transients are occurring, so optimal phase shift is estimated to be in the middle of these two points, which is marked as  $\Phi_{opt}$ . The HF buffer is designed using current feedback source degenerated push-pull type buffers with ~400

Fig. 7. Microphotograph of the 64-channel ICE ASIC, implemented in a 60 V, 0.18-  $\mu$ m HV-BCD CMOS process.

Fig. 8. Timing diagram of the proposed system.

Fig. 9. (a) Measured pulser output from adjacent 8 channels. (b) Multiple consecutive pulse generation for Doppler imaging.

MHz bandwidth, tuned for 75  $\Omega$  cable termination [29].

#### V. EXPERIMENTAL RESULTS

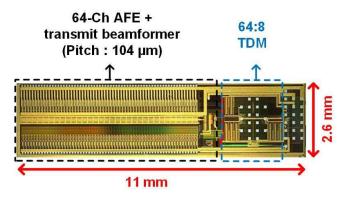

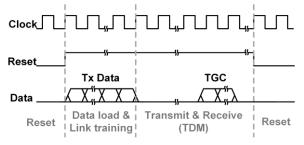

The ASIC is fabricated in a  $0.18\mu$ m 60 V power management 4M1P HV-BCD CMOS process. It consists of 64 channel AFE (pulser, Tx/Rx switch, LNA, and buffer), Tx beamformer, and symmetrically designed TDM, which occupies  $2.6 \times 11$  mm<sup>2</sup>, as shown in Fig. 7. The pads for supplies, control signals and TDM outputs are located on the right side of ASIC, which are designed to be compatible with flip-chip interconnect based catheter cable connection. The chip consumes 401 mW of power on average for B-mode imaging using phased-array beamforming, 42% of which is used for TDM and drivers. Fig. 8 shows the timing diagram of the proposed system. The ASIC requires clock, reset, and data inputs. Once the Tx data is loaded properly after link training from the TDM side, the Tx beamformer triggers pulsers to fire

Fig. 10. Measured and simulated frequency response of variable gain LNA with different 4 gains.

Fig. 11. Comparison between the signal generator and TDM output signals after digital signal processing.

HV pulses based on the beamforming profile, and Rx circuits are receiving at the same time. TGC signal can be loaded through data line to control the Rx gain at specific times. To eliminate the dead time during the Tx data loading, another set of Tx beamforming data can be loaded during receive period after Tx firing is done. After receiving the echo signals, reset signal returns the entire system back to the initial state. The link training always needs to be done before loading beamforming data, that compensates any change of the delay of the cable due to temperature change or bending.

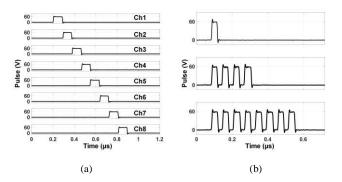

#### A. Electrical Characterization for Tx Circuitry

The ASIC was wire-bonded to a custom printed circuit board (PCB) to probe the output of the pulsers with the effective loading of ~15 pF, which is the equivalent capacitance of 1D piezo-array with 80 membranes (each membrane occupies  $46 \times 46 \ \mu m^2$ ). The FPGA generates beamforming profile where each channel has the pulse width of 80 ns, and is delayed by 80 ns relative to the previous channel. Fig. 9(a) shows the measured pulse output from channel 1 to channel 8. The pulsers successfully generate 60 V pulses with rise and fall time of 6 ns, which is suitable for driving a center frequency of 7 MHz pulse. Fig. 9(b) shows that the proposed Tx beamformer can generate up to 8 pulses for Doppler operation.

#### B. Electrical Characterization for LNA and Rx TDM

Fig. 10 compares the measured and simulated frequency response of variable gain LNA with different gain settings, which shows 15 dB, 21 dB, 27 dB, and 32 dB at center

Fig. 12. Crosstalk measurement of 8 channels of TDM circuitry.

frequency of 7 MHz with 3 dB bandwidth of 11 MHz. The measured input referred noise at 7 MHz for different gain levels show less than 4.1 nV/ $\sqrt{\text{Hz}}$  on average, close to the design target value of 5 nV/ $\sqrt{\text{Hz}}$ , which is calculated from the assumed LNA input dynamic range.

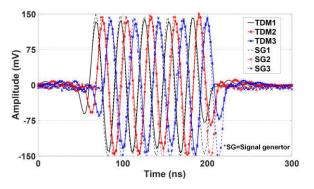

The proposed Rx TDM was separately characterized with a test chip to evaluate the performance of TDM circuitry. The test chip included a subset of blocks in the main ASIC, the ones needed to evaluate a block of 8 channels of TDM, as shown in Fig. 5(a), with an additional control block for link training. A custom PCB was designed to connect 8 input signals from external signal generators, and TDM output signal was connected to one of the backend TDM input terminals. The ADC samples the corresponding channel signals, then the FPGA performs DDD and further digital processing for interpolation, decimation, phase correction, and filtering to recover the original input data [7]. To test this signal chain, channel 1, 2, and 3 were connected to signal generators, which generated 7 MHz sine waves with 50 ns delay. Fig. 11 shows the comparison between digitized signal generator output and recovered TDM output signals after signal processing, which shows good agreement. The mismatch between the TDM outputs and signal generator outputs in the first and the last bursts is the result of band pass filtering. The mismatch between the channels is measured to be less than 0.6 dB in amplitude.

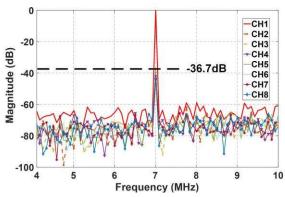

The level of crosstalk was also characterized in the TDM test chip. A 7 MHz sine wave was applied to channel 1, while inputs to other channels were grounded. The TDM signal was recovered for all 8 channels and analyzed using fast Fourier transform (FFT). Fig. 12 shows that the maximum crosstalk level is -36.7 dB when compared to channel 1, which is suitable for ICE application [9]. It is noteworthy that this measurement of the crosstalk is between the signals of the same TDM block over the same cable as a result of the multiplexing scheme, which represent the worst case scenario. The crosstalk level between separate TDM blocks on different cables was measured to be below -60 dB.

#### C. Ultrasound Imaging with the Entire System

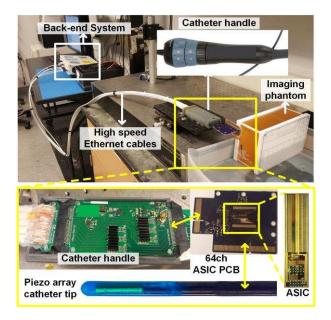

The proof-of-concept imaging experiments were performed by connecting the ASIC wire-bonded on a PCB, to a 64 channel piezoelectric transducer array at the tip of an ICE catheter using cables as shown in Fig. 13. The ASIC PCB is directly

7

Fig. 13. Ultrasound imaging measurement setup with piezo-array immersed in the water facing standard phantom.

Fig. 14. (a) B-mode image of 10 nylon wires, and (b) 2 cysts image in a standard phantom.

connected to catheter handle, which the TDM signals are amplified prior to passing through to the ADCs in the backend system via 3 m of Ethernet (Cat7A) cable to allow the system to be placed away from the MRI bore or the ultrasound mainframe in practice. In the future, the piezoelectric array will be either flip-chip bonded to the ASIC or the CMUT-on-CMOS technique will be applied for compact assembly, both of which are expected to reduce the parasitics and improve the resulting image.

| Parameter                               | This work     | [12]             | [13]       | [25]       | [32]          | [33]          |

|-----------------------------------------|---------------|------------------|------------|------------|---------------|---------------|

| Single chip integrated                  | Yes           | No               | No         | No         | No            | No            |

| Tx-Rx system                            |               |                  |            |            |               |               |

| Shared Tx-Rx array                      | Yes           | No               | N/A        | No         | No            | No            |

| aperture with pitch match               |               |                  |            |            |               |               |

| Rx wire reduction                       | TDM           | ADC + S/H analog | ADC + FIFO | S/H analog | Analog filter | S/H + Digital |

| Tx Wire reduction                       | Yes           | No               | No         | No         | No            | No            |

| Rx raw data accessibility               | Yes           | No               | Yes        | No         | No            | No            |

| Center frequency (MHz)                  | 7             | 5                | 5          | 5          | 40            | 3             |

| Tx delay min (ns)/max( $\mu$ s)         | 5/10.235      | -                | -          | -          | -             | -             |

| Die size (mm <sup>2</sup> )             | 2.6×11        | 2.5×4.8          | 2.93×3.2   | 6.1×6.1    | 1.2×0.3       | 4.5×4.3       |

| Power/ Rx channel (mW)                  | 6.26          | 0.91             | 17.5       | 0.27       | 4.62          | 17.81         |

| Active area/ channel (mm <sup>2</sup> ) | 0.27          | 0.026            | 0.088      | 0.026      | 0.045         | 0.303         |

| Power/ Rx active area                   | 23.18         | 35               | 198.96     | 10.38      | 102.66        | 58.77         |

| $(mW/mm^2)$                             |               |                  |            |            |               |               |

| # of channels                           | 64Tx/64Rx     | 144Rx            | 16Rx       | 1024Rx     | 8Rx           | 64Rx          |

| # of wires / Rx channels                | 8/64          | 4/144            | 1/16       | 96/1024    | 1/8           | 1/64          |

| # of wires/ Tx channels                 | 0.0625 (4/64) | 1                | 1          | 1          | 1             | 1             |

| Tx amplitude                            | 60V           | -                | -          | -          | -             | -             |

| Transducer                              | 1D            | 2D PZT           | 2D CMUT    | 2D PZT     | Annular       | 2D CMUT       |

|                                         | PZT/CMUT      |                  |            |            | CMUT          |               |

| Process                                 | 0.18 μm HV    | 0.18 µm          | 28 nm      | 0.18 µm    | 0.35 µm       | 0.13 μm       |

TABLE I

BENCHMARKING OF THE REDUCED-WIRE ULTRASOUND ASIC SYSTEMS

The piezoelectric transducer array is immersed in a water tank, facing a multi-purpose standardized tissue mimicking imaging phantom (N-365, Kyoto Kagaku, Japan). To form a cross-sectional B-scan image of the phantom, in Tx mode, the Tx beamformer is programmed to generate 123 focused and steered beams using suitable delay schemes to scan the ±45° sector image. In Rx mode, the echo signals captured by the ASIC front-end are transferred to the back-end system where the signals are post-processed and dynamic Rx beamforming is performed to reconstruct B-scan images [6]. Two different imaging targets inside the imaging phantom were used to test the performance of the system. First, a set of 10 nylon wire targets of 100  $\mu$ m diameter were imaged. Fig. 14(a) shows the image of the 10 wire target, in which each wire is located 1 cm apart from others up to a depth ~5 cm, as shown in the diagram on the right. The second target was 2 gray scale cyst phantoms at a depth of 3 cm, as shown in Fig. 14(b). Both images are presented with a dynamic range (DR) of 40 dB. The contrast-to-noise-ratio (CNR) was also calculated for the cyst target to quantify the system performance. The CNR is defined as [30],

$$CNR = \frac{|\mu_C - \mu_B|}{\sqrt{\sigma_C^2 + \sigma_B^2}},\tag{1}$$

where  $\mu_{\rm C}$  and  $\mu_{\rm B}$  are the mean intensities of the regions inside the cyst and outside the cyst, respectively, and  $\sigma_{\rm C}^2$  and  $\sigma_{\rm B}^2$  are the corresponding variances. The CNR values for T<sub>1</sub> and T<sub>2</sub> cyst (Fig. 14(b)) were calculated as 1.55 and 1.23 with a relative contrast difference of 2 dB, which is in reasonable agreement with specs of the phantom [31].

#### VI. DISCUSSION

Overall, these results demonstrate the full functionality of the ASIC and backend system with a performance suitable for the targeted ICE application. Since the size of the pulser often limits the minimum size of Tx/Rx elements on the ASIC, the reduced capacitive loading with smaller 2D array elements will

help to pitch-match the ASIC with a 2D ICE array implementation.

Table I benchmarks this work against the state-of-the-art ultrasound ASIC designs, where detailed information is available. As seen in the overall system comparison, this ASIC is the only system that integrates Tx/Rx without compromising imaging aperture and access to raw Rx data. This ASIC generates Tx delays from 5 ns to 10.235  $\mu$ s to steer the ultrasound beam over the  $\pm 45^{\circ}$  field of view, and has effectively 0 to 11 MHz pulse-echo system bandwidth. The die size is determined by the ICE application to fit in a 9 F catheter as shown in the ASIC micrograph (Fig. 7). Note that the power consumption per active chip area compares favorably with most other Rx cable reduction systems. AFE of each channel occupies 0.27 mm<sup>2</sup>, which is designed to match the pitch for future CMUT-on-CMOS design (element size: 2.6×0.104 mm<sup>2</sup>). Number of Rx cables is reduced by 8:1 TDM. Note that in case of a 2D array when TDM is used in conjunction with 3x3 subarray beamforming with switched-capacitor delay, this ratio can increase to 72:1.

The number of wires per Tx channel is reported as 4/64, including the data and clock wires, which is a significant advantage of this particular ASIC. It should be noted that this figure will further improve by increasing number of Tx channels for a system with larger number of elements as the required number of wires will remain the same. The size and power can be further optimized as the proposed ASIC is the first prototype for proof-of-concept for catheter-based ICE application, however even with non-ideal PCB based interconnect and partly operational PZT array, overall this novel system provides high dynamic range images of tissue mimicking phantoms.

#### VII. CONCLUSIONS

This work integrates both Tx beamformer and TDM based Rx in a single chip to reduce the number of interconnect wires

in a 64 element 2D imaging ICE catheter. The Tx beamformer is capable of steering and focusing the Tx beams in a wide angular range and can be programmed in every firing using a single data line. The crosstalk levels and overall SNR of the resulting images indicate suitable performance for 2D imaging with 1D ICE arrays. The number of wires has been reduced from more than 64 down to 22 for this application, while maintaining full access to the raw data from each channel. More significant reduction is expected for 2D array-based systems with a larger number of elements. The reduction in cable count will not only create the potential for operation under MRI and reduce catheter cost, but it will also increase the mechanical flexibility and possibility of additional functionality in ICE catheters.

#### REFERENCES

- W. Saliba and J. Thomas, "Intracardiac echocardiography during catheter ablation of atrial fibrillation," Europace, vol. 10, no. suppl 3, pp. 42–47, 2008.

- [2] S. S. Kim, Z. M. Hijazi, R. M. Lang, and B. P. Knight, "The use of intracardiac echocardiography and other intracardiac imaging tools to guide noncoronary cardiac interventions," Journal of the American College of Cardiology, vol. 53, no. 23, pp. 2117 – 2128, 2009.

- [3] D. Wildes, W. Lee, B. Haider, S. Cogan, K. Sundaresan, D. M. Mills, C. Yetter, P. H. Hart, C. R. Haun, M. Concepcion, J. Kirkhorn, and M. Bitoun, "4-D ICE: A 2-D array transducer with integrated ASIC in a 10-Fr catheter for real-time 3-D intracardiac echocardiography," IEEE Trans. Ultrason., Ferroelect., Freq. Control, vol. 63, no. 12, pp. 2159–2173, Dec. 2016.

- [4] M. F. Dempsey, B. Condon, and D. M. Hadley, "Investigation of the factors responsible for burns during MRI," Journal of Magnetic Resonance Imaging, vol. 13, no. 4, pp. 627–631, 2001.

- [5] S. A. Mirbozorgi et al., "A feasibility study for MRI guided CMUT-based intracardiac echocardiography catheters," IEEE Ultrasonics Symp., pp. 1-4, 2017.

- [6] T. L. Szabo, Diagnostic Ultrasound Imaging: Inside Out (Second Edition), Boston: Academic Press, 2014. pp. 209-250.

- [7] T. M. Carpenter, M. W. Rashid, M. Ghovanloo, D. M. J. Cowell, S. Freear, and F. L. Degertekin, "Direct digital demultiplexing of analog TDM signals for cable reduction in ultrasound imaging catheters," IEEE Trans. Ultrason., Ferroelect., Freq. Control, vol. 63, no. 8, pp. 1078–1085, Aug. 2016.

- [8] Qilong Liu, Chao Chen, Z. Chang, C. Prins and M. A. P. Pertijs, "A mixed-signal multiplexing system for cable-count reduction in ultrasound probes," IEEE Ultrasonics Symp., 2015, pp. 1-4.

- [9] C. Oakley, J. Mueller, D. Dietz and J. Kuhnke, "A minimally invasive ultrasound probe using non-coax cabling," IEEE Ultrasonics Symp., vol. 2, pp. 1011-1016, Oct. 2001.

- [10] M. W. Rashid, C. Tekes, M. Ghovanloo, and F. L. Degertekin, "Design of frequency-division multiplexing front-end receiver electronics for CMUT-on-CMOS based intracardiac echocardiography," IEEE Ultrasonics Symp., pp. 1540–1543, Sep. 2014.

- [11] B. Savord and R. Solomon, "Fully sampled matrix transducer for real time 3D ultrasonic imaging," IEEE Ultrasonics Symp., pp. 945-953 Vol.1. 2003.

- [12] C. Chen et al., "A Pitch-Matched Front-End ASIC With Integrated Subarray Beamforming ADC for Miniature 3-D Ultrasound Probes," IEEE J. Solid-State Circuits, Sep. 2018.

- [13] M.C. Chen, et al., "A pixel-pitch-matched ultrasound receiver for 3d photoacoustic imaging with integrated delta-sigma beamformer in 28nm UTBB FDSOI," ISSCC Dig. Tech. Papers, pp. 456-457, Feb. 2017.

- [14] P. Santos, G. U. Haugen, L. Løvstakken, E. Samset and J. D'hooge, "Diverging Wave Volumetric Imaging Using Subaperture Beamforming," IEEE Trans. Ultrason., Ferroelect., Freq. Contr., vol. 63, no. 12, pp. 2114-2124, Dec. 2016.

- [15] Y. Katsube, et al., "Single-chip 3072ch 2D array IC with RX analog and all-digital TX beamformer for 3D ultrasound imaging," ISSCC Dig. Tech. Papers, pp. 458-459, Feb. 2017.

- [16] K. Chen, H. S. Lee, and C. G. Sodini, "A column-row-parallel asic architecture for 3-d portable medical ultrasonic imaging," IEEE J. Solid-State Circuits, vol. 51, no. 3, pp. 738–751, March 2016.

- [17] A. Bhuyan, J. Choe, B. C. Lee, I. Wygant, A. Nikoozadeh, O. Oralkan, and B. Khuri-Yakub, "3D volumetric ultrasound imaging with a 32 x 32 CMUT array integrated with front-end ICs using flip-chip bonding technology," ISSCC Dig. Tech. Papers, pp. 396–397 Feb. 2013.

- [18] A. Bhuyan, J. Choe, B. C. Lee, I. Wygant, A. Nikoozadeh, O. Oralkan, and B. Khuri-Yakub, "Integrated circuits for volumetric ultrasound imaging with 2-D CMUT arrays," IEEE Trans. Biomed. Circuits Syst., vol. 7, no. 6, pp. 796-804, Dec. 2013.

- [19] M. W. Rashid et al., "Front-end electronics for cable reduction in Intracardiac Echocardiography (ICE) catheters," IEEE Ultrasonics Symp., pp. 1-4, Sep. 2016.

- [20] S. J. Jung, J. K. Song and O. K. Kwon, "Three-side buttable integrated ultrasound chip with a 16x16 reconfigurable transceiver and capacitive micromachined ultrasonic transducer array for 3-D ultrasound imaging systems," IEEE Trans. Electron Devices, vol. 60, no. 10, pp. 3562-3569, Oct. 2013.

- [21] G. Gurun, P. Hasler and F. L. Degertekin, "Front-end receiver electronics for high-frequency monolithic CMUT-on-CMOS imaging arrays," IEEE Trans. Ultrason. Ferroelectr. Freq. Control., vol. 58, no. 8, pp. 1658-1668, Aug. 2011.

- [22] P. R. Smith, D. M. J. Cowell and S. Freear, "Width-modulated square-wave pulses for ultrasound applications," IEEE Trans. Ultrason., Ferroelect., Freq. Control, vol. 60, no. 11, pp. 2244-2256, Nov. 2013.

- [23] G. Jung, C. Tekes, A. Pirouz, L. Degertekin and M. Ghovanloo, "Supply-doubled pulse-shaping high voltage pulser for CMUT arrays," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 65, no. 3, pp. 306-310, March 2018.

- [24] K. Chen, H.-S. Lee, A. P. Chandrakasan, and C. G. Sodini, "Ultrasonic imaging transceiver design for CMUT: A three-level 30-Vpp pulse-shaping pulser with improved efficiency and a noise-optimized receiver," IEEE J. Solid-State Circuits, vol. 48, no. 11, pp. 2734–2745, Nov. 2013.

- [25] C. Chen, et al., "A Front-End ASIC with Receive Sub-Array Beamforming Integrated with a 32 x 32 PZT Matrix Transducer for 3-D Transesophageal Echocardiography," IEEE J. Solid-State Circuits, vol. 52, no. 4, pp. 994-1006, Apr. 2017.

- [26] M. Sautto, A. S. Savoia, F. Quaglia, G. Caliano, A. Mazzanti, "A comparative analysis of CMUT receiving architectures for design optimization of integrated transceiver front-ends," IEEE Trans. Ultrason., Ferroelect., Freq. Contr., Feb. 2017.

- [27] H. P. E. Stern and S. A. Mahmoud, Communication Systems: Analysis and design. Prentice Hall, 2004.

- [28] D. Spirit, A. D. Ellis, and P. Barnsley, "Optical time division multiplexing: systems and networks," IEEE Communications Magazine, vol. 32, no. 12, pp. 56-62, Dec. 1994.

- [29] Manetakis, K.; Toumazou, C.; Papavassiliou, C., "A 120 MHz, 12 mW CMOS current feedback opamp," Custom Integrated Circuits Conference, Proceedings of the IEEE, pp. 365-368, May 1998.

- [30] M. Karaman, P. C. Li, and M. O'Donnell, "Synthetic aperture imaging for small scale systems," IEEE Trans. Ultrason., Ferroelect., Freq. Contr., vol. 42, no. 3, pp. 429–442, 1995.

- [31] Kyoto Kagaku America Inc., "US-2: N-365 multipurpose QA phantom", [Online], Available: https://www.kkamerica-inc.com/us-2\_n-365\_multip urpose\_qa\_phantom. [Accessed: 18- July- 2018].

- [32] G. Gurun, et al., "An analog integrated circuit beamformer for high-frequency medical ultrasound imaging," IEEE Trans. Biomed. Circuits Syst., vol. 6, no. 5, pp. 454-467, Oct. 2012.

- [33] J.Y. Um, et al., "An analog-digital-hybrid single-chip Rx beamformer with non-uniform sampling for 2D-CMUT ultrasound imaging to achieve wide dynamic range of delay and small chip area," ISSCC Dig. Tech. Papers, pp. 426-427, Feb. 2014.

**Gwangrok Jung** received the B.S. and M.S. degrees in electrical engineering from Seoul National University, Seoul, Korea in 2007 and 2009, respectively. He was with DMC R&D center at Samsung Electronics, where he was involved in development of Integrated Circuits for portable ultrasound system. He is currently working toward Ph.D. degree in electrical and computer engineering at Georgia Institute of Technology, Atlanta, GA, USA. His research is developing intracardiac echocardiography (ICE) system with capacitive micromachined ultrasonic transducer (CMUT) and piezo-transducer. His research interests include analog, digital, mixed-mode circuits design for biomedical applications, sensor interface IC, high voltage circuit design, and system integration.

**Coskun Tekes** (S'04-M'11) was born in Istanbul, in 1976. He received the B.S. degree from Istanbul Technical University, Istanbul, Turkey in 1998, and the M.S. and Ph.D. degrees from Isik University, Istanbul, Turkey, in 2002 and 2010, respectively, all in electrical and electronics engineering. He was a research assistant in the Electronics

Engineering Department of Isik University between 2004 and 2010. He worked as a research engineer in

the George W. Woodruff School of Mechanical Engineering, Georgia Institute of Technology between 2010 and 2018. He is currently working at School of Computer Engineering at the Kennesaw State University, Marietta, GA, USA as an assistant professor. His research interests include medical ultrasonic imaging, signal and image processing.

**M. Wasequr Rashid** (S'10) received the B.Sc. degree in electrical and electronis engineering from the Bangladesh University of Engineering and Technology, Dhaka, Bangladesh, in 2004, the M.S. degree in electrical and computer engineering from New Mexico State University, Las Cruces, NM, USA, in 2010, and the Ph.D. degree in electrical and computer engineering from the Georgia Institute of Technology, Atlanta, GA, USA. He is currently Seattle Washington USA

working at Impinj Inc., Seattle, Washington, USA.

Thomas M. Carpenter received the M.Eng. degree in electronic and electrical engineering from the University of Leeds, Leeds, U.K., in 2014. He joined the Georgia Institute of Technology, Atlanta, GA, USA, as a Research Engineer developing high-speed field-programmable gate array (FPGA) designs for ultrasound imaging applications. He is currently a Visiting Researcher with the Ultrasound Research Group, University of Leeds. His current research

interests include embedded systems and FPGA design, both in the biomedical field and for industrial applications.

**David Cowell** (M'14) received the Ph.D. degree from the University of Leeds, Leeds, U.K., in 2008, for research on advanced coding techniques and excitation circuit design for industrial instrumentation and medical imaging ultrasound systems. He performed extensive consultancy in instrumentation, field-programmable gate arrays, and high-speed digital hardware design. Following work as a Research Consultant in measurement and instrumentation, he

joined the Ultrasound Group, University of Leeds, as a Research Fellow. His current research interests include noninvasive industrial ultrasound measurement and advanced miniaturized ultrasound excitation systems with low harmonic distortion for phased array imaging, ultrasound system design, and signal processing.

**Steven Freear** (S'95–M'97–SM'11) received the doctorate degree in 1997 and subsequently worked in the electronics industry for 7 years as a medical ultrasonic system designer. He was appointed Lecturer (Assistant Professor), Senior Lecturer (Associate Professor), and then Professor in 2006, 2008, and 2016, respectively, at the School of Electronic and Electrical Engineering at the University of Leeds, U.K. In 2006, he formed the Ultrasound Group,

specializing in both industrial and biomedical research. His main research

interest is concerned with advanced analog and digital signal processing and instrumentation for ultrasonic systems. He teaches digital signal processing, VLSI and embedded systems design, and hardware description languages at both undergraduate and postgraduate levels. He was elected Editor-in-Chief in 2013 for the IEEE Transaction on Ultrasonics, Ferroelectrics, and Frequency Control. In June 2014, he was appointed Visiting Professor at Georgia Tech. He is External Examiner to undergraduate programmes in Electronic Engineering at Queens University, Belfast.

**F. Levent Degertekin** received the B.S. degree in 1989 from the Middle East Technical University, Turkey; the M.S. degree in 1991 from Bilkent University, Turkey; and the Ph.D. degree in 1997 from Stanford University, CA, all in electrical engineering. He worked at the E.L. Ginzton Laboratory of Stanford University first as a Visiting Scholar during the 1992-93 academic year and then as an Engineering Research Associate from 1997 to 2000. Currently, he

holds the G.W. Woodruff Chair in Mechanical Systems, and is a Professor at the G.W. Woodruff School of Mechanical Engineering and the School of Electrical and Computer Engineering, Georgia Institute of Technology, GA. His research interests have been in micromachined acoustic and opto-acoustic devices, medical ultrasound imaging bioanalytical instrumentation, and atomic force microscopy. He has authored over 50 U.S. patents and over 100 journal publications. Dr. Degertekin was an associate editor for the IEEE Sensors Journal and currently serves as an associate editor for the IEEE Transactions on Ultrasonics, Ferroelectrics and Frequency Control. He also serves on the Technical Program Committee of the IEEE Ultrasonics Symposium. Dr. Degertekin has received an NSF CAREER award for his work on ultrasonic atomic force microscopy in 2004, and with his students, the IEEE Ultrasonics, Ferroelectrics, and Frequency Control (UFFC) Society 2004 Outstanding Paper award, and most recently the IEEE UFFC Society 2014 Carl Hellmuth Hertz Ultrasonic Achievement Award.

**Maysam Ghovanloo** (S'00–M'04–SM'10) received the B.S. degree in electrical engineering from the University of Tehran, and the M.S. degree in biomedical engineering from the Amirkabir University of Technology, Tehran, Iran in 1997. He also received the M.S. and Ph.D. degrees in electrical engineering from the University of Michigan, Ann Arbor, in 2003 and 2004.

From 2004 to 2007 he was an Assistant Professor

in the Department of ECE at the North Carolina State University, Raleigh, NC. Since 2007 he has been with the Georgia Institute of Technology, School of Electrical and Computer Engineering, where he is a Professor and the founding director of the GT-Bionics Lab. He has 5 issued patents and authored or coauthored more than 200 peer-reviewed conference and journal publications on implantable microelectronic devices, integrated circuits and micro-systems for IMD applications, and modern assistive technologies.

Dr. Ghovanloo is an Associate Editor of the IEEE Transactions on Biomedical Engineering and IEEE Transactions on Biomedical Circuits and Systems. He was the general chair of the IEEE Biomedical Circuits and Systems (BioCAS 2015) in Atlanta, GA in Oct. 2015. He served as an Associate Editor of IEEE Transactions on Circuits and Systems, Part II (2008-2011), as well as a Guest Editor for the IEEE Journal of Solid-State Circuits and IEEE Transactions on Neural Systems and Rehabilitation Engineering. He has received the National Science Foundation CAREER Award, the Tommy Nobis Barrier Breaker Award for Innovation, and Distinguished Young Scholar Award from the Association of Professors and Scholars of Iranian Heritage.