This is a repository copy of *Elimination of leakage in GaN-on-diamond*.

White Rose Research Online URL for this paper: http://eprints.whiterose.ac.uk/112526/

Version: Accepted Version

## **Proceedings Paper:**

Alvarez, B., Francis, D., Faili, F. et al. (4 more authors) (2016) Elimination of leakage in GaN-on-diamond. In: Compound Semiconductor Integrated Circuit Symposium (CSICS), 2016 IEEE. 2016 IEEE CSIC Symposium, 23–26 October 2016, Austin, TX, USA. IEEE, pp. 114-117.

https://doi.org/10.1109/CSICS.2016.7751039

© 2016 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other users, including reprinting/ republishing this material for advertising or promotional purposes, creating new collective works for resale or redistribution to servers or lists, or reuse of any copyrighted components of this work in other works.

## Reuse

Unless indicated otherwise, fulltext items are protected by copyright with all rights reserved. The copyright exception in section 29 of the Copyright, Designs and Patents Act 1988 allows the making of a single copy solely for the purpose of non-commercial research or private study within the limits of fair dealing. The publisher or other rights-holder may allow further reproduction and re-use of this version - refer to the White Rose Research Online record for this item. Where records identify the publisher as the copyright holder, users can verify any specific terms of use on the publisher's website.

## Takedown

If you consider content in White Rose Research Online to be in breach of UK law, please notify us by emailing eprints@whiterose.ac.uk including the URL of the record and the reason for the withdrawal request.

eprints@whiterose.ac.uk https://eprints.whiterose.ac.uk/

# Elimination of leakage in GaN-on-diamond

B. Alvarez<sup>1</sup>, D. Francis<sup>1</sup>, F. Faili<sup>1</sup>, F. Lowe<sup>1</sup>, D. Twitchen<sup>1</sup>, K.B. Lee<sup>2</sup>, P. Houston<sup>2</sup>

(email: Daniel.Francis@e6.com)

1. Element Six, Santa Clara, CA, USA,

2. Department of Electronic and Electrical Engineering, University of Sheffield, Sheffield UK

Abstract – The use of chemical vapor deposition diamond as a substrate for Gallium Nitride to form GaN-on-diamond has the potential to allow for higher linear power densities in GaN HEMTs. The increase in GaN HEMT power density on diamond has been limited to date by the electrical leakage in GaN-ondiamond substrates. In this paper we show that to eliminate bulk leakage in silicon based GaN-ondiamond you have to completely remove the transition layers used to grow high quality GaN on the original host silicon. We show that by completely removing the transition layers in GaN-on-diamond we demonstrated bulk leakage comparable to the leakage in GaN on silicon carbide.

#### Index Terms – GaN-on-Diamond, HEMT, GaN

#### I. INTRODUCTION

The introduction of CVD diamond as a viable substrate for GaN HEMTs [1], [2] makes it attractive to run higher power densities through the GaN HEMT than is normally used for traditional GaN host substrates [3]. While power densities of 20 and 40W/mm have been demonstrated for pulsed devices on SiC [4], continuous powers exceeding 10W/mm will reduce the lifetime of the GaN HEMTs due to self-heating.

GaN-on-diamond holds a promise of reducing the problems associated with self-heating and allow for increases in the power density of HEMT devices. To date, GaN-on-diamond has been shown to allow for higher areal power densities than GaN-on-SiC [5], [6].

The increase in areal power density is achieved by reducing the gate to gate spacing in a HEMT. While increasing the areal density by reducing the gate to gate spacing is a useful way to get higher power densities it still runs into practical limits associated with via holes and metal lines with aspect ratios difficult to fabricate. Another way to increase the power density is to increase the device bias voltage. By increasing the bias voltage without changing the device design one can get to higher power densities. One factor limiting increases in bias voltage for GaNon-diamond has been the device leakage. As the bias is increased the leakage current limits the shut-off of the devices.

Leakage in GaN HEMT devices can be on the GaN surface, in the GaN bulk, or at the interface between

the GaN and the diamond. In this paper we investigate the sources of GaN-on-diamond leakage in the bulk and at the interface between the GaN and the diamond (for simplicity in the rest of the paper we will refer to the combination of bulk and interface leakage as bulk leakage). The goal is to understand the sources of leakage and ultimately control the leakage so that higher bias voltages can be used to increase the linear power density in GaN-on-diamond devices.

#### II. METHOD OF MAKING GAN-ON-DIAMOND

The method used to create GaN-on-diamond, (described in more detail in [7]) involves a double flip of the GaN epi, an etch of nucleation layers and a diamond growth which exposes the GaN epi to elevated temperatures for an extended period. We have shown in the past that the resulting epi exhibits leakage at higher bias voltages on devices. It is our belief that surface currents must be controlled at the device fabrication level, bulk leakage must be controlled at the materials level. To understand bulk leakage we fabricated test devices that removed the 2DEG and isolated the surface allowing us to focus exclusively on the leakage currents through the bulk GaN buffer. Our objective with this study was to understand the mechanisms which drive the leakage with the intention of eliminating them.

A. GaN-on-Diamond Test Devices

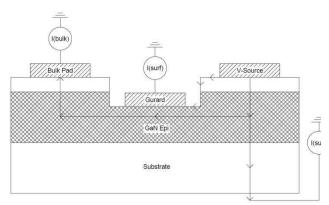

GaN-on-diamond test devices are made by depositing contact metals and annealing to form Ohmic contacts. Isolation channels are etched into the GaN then Schottky contacts and overlay metals are deposited. The isolation region is about 10 microns long and 100 microns wide. A cross-sectional schematic is shown in Figure 1. The voltage is applied between  $V_{source}$  and Bulk pad. Any surface current is collected in the guard ring. A detailed description of the fabrication and design is found in [8].

Fig. 1 Test structure used to measure bulk, surface and substrate leakage.

#### **III. EFFECT OF THE TRANSITION LAYERS**

The transition or nucleation layers in GaN-ondiamond are a highly defective superlattice of different compositions of AlGaN. As the superlattice grows the number of defects is reduced. The problem with GaN on silicon is that the transition layers (TLs) have defects which have poor electrical and thermal properties. The thermal conductivity, measured at 10 W/mK [9] is reason enough for wanting to remove these layers. However, in most systems removing the TLs is not possible because they are critical for forming high quality GaN on host substrate. In our GaN-on-diamond fabrication process we have direct access to the defective AlGaN so have the ability to remove them. The problem in removing the AlGaN layers is that the high level of defects also leads to non-uniform etching which can mean incomplete removal of the AlGaN.

In addition to the poor thermal conductivity the electrical properties are also undesirable. The formation of the AlGaN typically dopes the silicon creating a back barrier which impairs the performance of both GaN power and GaN high electron mobility (HEMT) devices. In this paper, we investigate the effects of the removal process and replacement with diamond has on the electrical properties of the buffer GaN and the interface between the GaN and the diamond.

Having removed the TLs multiple teams have demonstrated that the thermal properties of the GaNon-diamond exceed that of GaN on silicon carbide [5],[6]. The electrical properties however still limit the performance. In this paper we compare the electrical properties of GaN: on diamond, on silicon and on silicon carbide. The criteria we are using for inspection is the residual charge or minimum capacitance after the 2DEG has been fully depleted and the leakage which flows in the bulk GaN material.

#### IV. FABRICATION AND MEASUREMENTS

For devices we look at the buffer leakage in our case the current flowing through the buffer and possibly along the interface between the GaN and the diamond given that we can't isolate these two measurements, for the rest of the paper we will refer to this measurement as bulk GaN leakage. The device level bulk GaN leakage current measurements are made on the above described devices with the 2DEG eliminated and the surface currents collected. By eliminating the 2DEG and capturing the surface currents, the current flow measured is only in the bulk GaN leakage.

We chose not to investigate the surface leakage currents because each device manufacturer who uses our GaN-on-diamond wafer will have a slightly different surface condition and will need to work out surface passivation separately. However, bulk leakage currents are a materials problem which would be much harder to solve at the device level. Here we seek to characterize the quality of the bulk GaN and compare it to the bulk GaN grown on SiC without having been transferred to diamond.

Our critical parameter on wafer level measurements is the residual capacitance left after the 2DEG has been depleted. We typically make the wafer level measurements with the GaN surface passivated with 500 angstroms of silicon nitride. The surface passivation allows us to isolate the buffer characteristics without having the surface currents affect our measurements. In the CV measurements we deplete the GaN up to 30V to investigate the charges well into the host substrate.

If the GaN buffer has been damaged during the epi transfer process either from silicon to diamond we expect to see greater leakage currents on devices and higher residual capacitance on mercury probe measurements. The possible damage mechanisms are exposure to temperature and strain during diamond synthesis, exposure of the nitrogen face GaN during the process, residual damage left after the removal of the AlGaN transition layer removal or possibly bending induced strain due to the difference in expansion coefficient between the silicon and the diamond.

#### IV. RESULTS AND DISCUSSION

#### A. Device Measurements

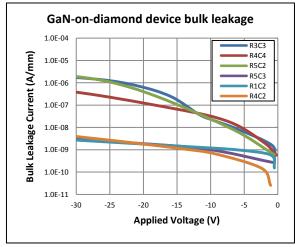

Fig. 2 shows measurements of 6 devices on one wafer. The leakage in all cases stays below  $50\mu$ A/mm at 30V. This corresponds to a bulk resistance of approximately  $10M\Omega$  which corresponds to a resistivity of  $8000\Omega$ ·cm. However we notice that there is a binomial distribution in the

leakage plots. Some devices have leakage of less than  $1\mu A$  others have leakage close to  $50\mu A$ . This distribution of results points to a localized leakage phenomena.

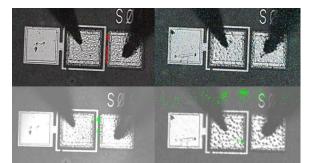

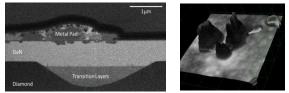

We used emission microscopy (EMMI) and optical-beam induced resistance change (OBIRCH) microscopy to identify where the leakage spots in both low leakage and high leakage devices on this wafer. Low leakage devices (Fig. 3a and b) showed no specific leakage spots when compared to the background and noise levels. The high leakage devices (Fig. 3c and d) showed specific leakage spots in both EMMI and OBIRCH techniques; leakage spots were identical in location with both techniques. We cross-sectioned a high leakage device using a focused ion beam etcher (FIB) to identify the cause of the leakage. The leakage spot and can be seen in Fig. 4a. The defect we found was a remnant of the TLs that were not etched during the TL removal. Fig. 4b shows an example of what

Fig. 2 Wafer 538 bulk leakage measurements for various devices across the wafer.

this residue looks like before diamond growth. Previous etch techniques left this residue, which lead to a larger leakage current (**Error! Reference source not found.**a). We found that carefully removing all the TLs results in lower leakage current. The lower leakage results are noticeable at wafer level CV measurement.

Fig. 3 a) An EMMI image of a low leakage device and an b) OBIRCH of the same low leakage device. C) An EMMI of a high leakage device an d) OBIRCH of the same high leakage device.

Fig. 4 a) FIB cross-section and b) laser confocal microscope image showing post transition etch residue.

#### B. Wafer Level CV Measurements

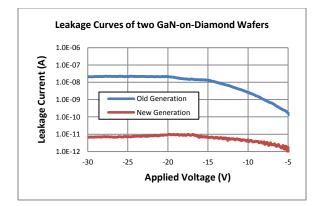

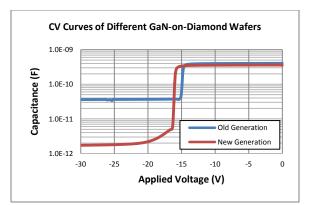

The mercury probe capacitance-voltage (C-V) measurements of the AlGaN/GaN HEMT structures allow us to probe the quality of the GaN buffer and interface material. The flat band capacitance (capacitance at high reverse bias) is indicative of negligible GaN buffer and interface charge/doping seen in Fig. 5b [10].

Fig. 5 a) Mercury probe CV of a wafer with residue (Old Generation) and a wafer without residue (New Generation). b) Mercury probe leakage of a wafer with residue (Old) and a wafer without residue (New).

GaN-on-diamond material with no residue has a flat band capacitance of approximately 2.5pF; this is a similar value as seen with as-grown GaN-on-SiC material (Table I). This is far lower than what is seen on GaN-on-Si, which is approximately 18pF.

Table I Flat Band Capacitances of Various Wafers Measured from Mercury Probe CV.

| Wafer<br>Type  | # of<br>Samples | Average<br>Flat Band<br>Capacitance<br>(pF) | Standard<br>Deviation<br>(pF) |

|----------------|-----------------|---------------------------------------------|-------------------------------|

| GaN-on-Diamond | 17              | 2.54                                        | 1.454                         |

| GaN-on-Si      | 10              | 17.81                                       | 0.126                         |

| GaN-on-SiC     | 1               | 1.91                                        | N/A                           |

#### CONCLUSIONS

Mercury probe CV and device measurements show that the transition layers from GaN-on-Si to GaN-on-Diamond must be removed to ensure low flat band capacitance and low leakage current. As the defective transition layers are removed, the electrical properties of the GaN-on-Diamond material are comparable to that of GaN-on-SiC and an improvement compared GaN on its original host silicon.

#### REFERENCES

- [1] J.G. Felbinger, M.V.S. Chandra, Y. Sun, L.F. Eastman, J. Wasserbauer, F. Faili, D. Babic, D. Francis, and F. Ejeckam, "Comparison of GaN HEMTs on diamond and SiC substrates," Electron Device Letters, IEEE 28 (11), 2007, 948-950; B)

- [2] J. Felbinger, M. V. S. Chandra, Y. Sun, L. F. Eastman, F. Ejeckam, D. Francis and J. Wasserbauer "Fabrication & Characterization of GaN-on-Diamond HEMTs" presented at

WOCSEMMAD, Feb 18-22, 2007, Savannah, GA

- [3] Microsemi PPG, "Gallium Nitride (GaN) versus Silicon Carbide (SiC) In The High Frequency (RF) and Power Switching Applications," www.Digikey.com

- [4] Wu, Y. F., Moore, M., Saxler, A., Wisleder, T., & Parikh, P. (2006, June). 40-W/mm double field-plated GaN HEMTs. In Device Research Conference, 2006 64th (pp. 151-152). IEEE.

- [5] D. Altman, M. Tyhach, J. McClymonds, S. Kim, S Graham, J. Cho, K. Goodson, D. Francis, F. Faili, F. Ejeckam, and S. Bernstein, "Analysis and Characterization of Thermal Transport in GaN HEMTs on Diamond Substrates", submitted to I-THERM 2014 Conference in Orlando, FL.

- [6] D.C. Dumka, T.M. Chou, D. Francis, F. Faili, and F. Ejeckam, "AlGaN/GaN HEMTs on Diamond Substrate with over 7 W/mm Output Power Density at 10GHz", accepted to IEEE Electronics Letters (Issue #20, 2013).

- [7] F. Ejeckam, D. Francis, F. Faili, F. Lowe, D. Twitchen, and B. Bolliger, "GaN-on-Diamond Wafers: A Progress Report" in GOMACTech-14 Conference, Mar 31 – Apr 3, Charleston, S.C. Results recently submitted to IMAPS (Oct 14-16, 2014, San Diego, CA) by Prof. Grace Xing of Notre Dame University.

- [8] Tan, W.S., Uren, M.J., Houston, P.A., Green, R.T., Balmer, R.S. and Martin, T., 2006. Surface leakage currents in SiN x passivated AlGaN/GaN HFETs. Electron Device Letters, IEEE, 27(1), pp.1-3.

- [9] Cho, Jungwan, et al. "Improved thermal interfaces of GaN-diamond composite substrates for HEMT Applications." Components, Packaging and Manufacturing Technology, IEEE Transactions on 3.1 (2013): 79-85.

- [10] Mishra, U.K., Shen, L., Kazior, T.E. and Wu, Y.F., 2008. GaN-based RF power devices and amplifiers. Proceedings of the IEEE, 96(2), pp.287-305.