This is a repository copy of Arbitrarily fast delayed signal cancellation PLL for grid-integration of renewable energy sources.

White Rose Research Online URL for this paper: <a href="https://eprints.whiterose.ac.uk/id/eprint/207555/">https://eprints.whiterose.ac.uk/id/eprint/207555/</a>

Version: Published Version

### Article:

Ahmed, H. orcid.org/0000-0001-8952-4190, Ushirobira, R. and Efimov, D. (2025) Arbitrarily fast delayed signal cancellation PLL for grid-integration of renewable energy sources. IET Renewable Power Generation, 19 (1). e12657. ISSN 1752-1416

https://doi.org/10.1049/rpg2.12657

### Reuse

This article is distributed under the terms of the Creative Commons Attribution-NonCommercial-NoDerivs (CC BY-NC-ND) licence. This licence only allows you to download this work and share it with others as long as you credit the authors, but you can't change the article in any way or use it commercially. More information and the full terms of the licence here: https://creativecommons.org/licenses/

### Takedown

If you consider content in White Rose Research Online to be in breach of UK law, please notify us by emailing eprints@whiterose.ac.uk including the URL of the record and the reason for the withdrawal request.

Check for updates

DOI: 10.1049/rpg2.12657

### ORIGINAL RESEARCH

## Arbitrarily fast delayed signal cancellation PLL for grid-integration of renewable energy sources

Hafiz Ahmed<sup>1</sup> Rosane Ushirobira<sup>2</sup> Denis Efimov<sup>2</sup>

<sup>2</sup>Inria, Univ. Lille, CNRS, UMR 9189 CRIStAL, Lille, France

#### Correspondence

Hafiz Ahmed, Nuclear Futures Institute, Bangor University, Bangor LL57 1UT, UK. Email: hafiz.ahmed@bangor.ac.uk; hafiz.h.ahmed@ieee.org

### Funding information

European Regional Development Fund, Grant/Award Number: Sêr Cymru II 80761-BU-103

### **Abstract**

Integrating renewable energy sources into an unbalanced distribution network requires fast and accurate extraction of fundamental frequency positive- and negative-sequence components from the unbalanced three-phase grid voltage signals. For this purpose, various methods are already available in the literature. Out of them, delayed signal cancellation (DSC) is prevalent. Conventional DSC can separate the sequence components using a quarter-cycle delay. Fast DSC tools can achieve the same with less than a quarter-cycle delay. However, neither conventional nor fast DSC can handle DC offset without requiring additional delayed signals. This article addresses this issue by proposing a modified DSC to estimate the sequence components with DC offset rejection and having arbitrarily fast convergence speed, that is, low memory requirement. Two equidistant delayed samples of the measured grid voltages/currents are required to implement the proposed technique and can easily be applied in a phase-locked loop (PLL). Comparative experimental results demonstrate the suitability of the proposed approach over other DSC methods.

### INTRODUCTION

In order to mitigate the negative impact of burning fossil fuels, renewable energy sources (RES) are becoming very popular worldwide. Many RES are now price competitive and/or cheaper compared to conventional gas/coal-fired electricity production. This has contributed to a broader societal acceptance of RES and also led to the large-scale integration of RES into the grid. RES, such as solar or wind, are interfaced with the power grid through power electronic converters. When the RES-powered grid-connected converter (GCC) operates in synchronization with the grid, maximum power transfer can be ensured. To achieve this, the control system of GCC requires the information on the grid, for example, phase, frequency, and amplitude in real-time. This process is commonly known as grid-synchronization [1–9], typically performed by the phase-locked loop (PLL).

RES are usually connected to the grid at the distribution network level. Due to the presence of single- and three-phase loads, per-phase loading of low-voltage distribution substations are not identical. This uneven connection of particularly single-phase loads causes phase unbalance at the distribution

network level [10-15]. Integrating RES into the unbalanced distribution network is challenging due to the simultaneous presence of fundamental frequency positive-sequences (FFPS) and fundamental frequency negative-sequences (FFNS) components in the grid voltage. Fast and accurate estimation of these components is essential for grid fault-tolerant control of RES-interfaced power converters. Typical examples are faultride through (FRT) control [16-18], voltage compensation for sensitive loads [19], and PLL implementation [20-22], to name a few.

Delayed signal cancellation (DSC) [23, 24] is a popular method in the literature to estimate FFPS and FFNS components from unbiased and unbalanced three-phase signals. This technique uses quarter-cycle delayed samples of the measured grid voltage/currents to estimate the sequence components. A modified DSC operation with fast convergence is proposed in [25–28] to reduce the estimation delay. An equivalent version of this approach with the same delay but lower computational complexity is proposed in [29]. However, these modified DSCs cannot reject DC offset without using an additional half-cycle DSC operation. A key limitation of [28] and [29] is that this approach can work only when no DC offset is presented in

This is an open access article under the terms of the Creative Commons Attribution-NonCommercial-NoDerivs License, which permits use and distribution in any medium, provided the original work is properly cited, the use is non-commercial and no modifications or adaptations are made. © 2022 The Authors. IET Renewable Power Generation published by John Wiley & Sons Ltd on behalf of The Institution of Engineering and Technology.

<sup>&</sup>lt;sup>1</sup>Nuclear Futures Institute, Bangor University, Bangor, UK

AHMED ET AL.

the grid. DC offset may appear due to a variety of reasons, for example, analog to digital conversion of measured signals [30], grid fault [31], current transformer saturation, geomagnetically induced currents [32] etc. In the presence of DC offset, the output of PLL has steady-state ripple, which causes undesirable reactive power injection to the grid. In addition, active power oscillation can also be observed, which degrades the power quality [33]. As such, mitigation of this DC offset is essential to ensure high-performance control of grid-connected converters.

To reject measurement bias, that is, DC offset, cascaded DSC (CDSC) is proposed in [23, 29]. In CDSC, an additional delayed signal cancellation block with a half-cycle delay is considered to reject the DC offset, increasing the overall estimation delay and augmenting the required memory to store the delayed samples. An improved DSC operation is presented in this work to overcome this issue. Our approach uses two equidistantly delayed samples of the measured signals to estimate the sequence components with DC offset rejection. The proposed solution is arbitrarily fast and has low computational complexity. Unlike other two-delayed-samplesbased FFPS sequence component estimation techniques [34], our solution is generic since it can estimate FFPS and FFNS components. In addition, our method can reject DC offset, unlike [34].

Like various variants of conventional DSCs [28, 29], the proposed modified DSC is also affected by voltage/current harmonics. Additional pre-loop and/or in-loop filtering stages or cascaded DSCs [21, 23] have to be implemented. This issue is addressed by integrating our method into a CDSC-PLL where the proposed technique replaces the DC offset and FFNS rejection DSC blocks. Reducing the memory requirement, and, consequently making the convergence time faster for DSC-PLL, is this work's main contribution. Compared to existing DSC-PLLs [23, 28], the proposed method can have up to 26% lower memory requirement, which makes the technique very suitable for real-time implementation in low-cost embedded devices.

The rest of this article is organized as follows: development of the proposed estimator is given in Section 2, experimental results are provided in Section 3, and finally, concluding remarks are given in Section 4.

## 2 | ESTIMATOR DESIGN

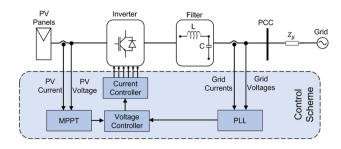

An overview of solar energy-powered GCC, including the control system block, is given in Figure 1. As shown in Figure 1, grid-synchronization through PLL plays an important role in the outer voltage controller. Here, PLL separates the sequence components and extracts the grid voltage phase for the in-phase operation of the GCC with the grid. It is to be noted here that in this work, the focus is on PLL only, and Figure 1 is used solely to contextualize the location of PLL in the converter control system. To facilitate this, let us consider the unbalanced three-phase grid voltages with measurement offset in the stationary

**FIGURE 1** An overview of a general grid-connected converter control system with PLL-based grid-synchronization method

reference frame as given by:

$$v_{\alpha}(t) = V_{\alpha 0} + V^{+} \cos(\omega t + \delta^{+}) + V^{-} \cos(\omega t + \delta^{-}),$$

(1)

$$v_{\beta}(t) = V_{\beta 0} + V^{+} \sin(\omega t + \delta^{+}) - V^{-} \sin(\omega t + \delta^{-}), \quad (2)$$

where the superscripts + and - denote the positive and negative sequences,  $\theta^{\pm} = \omega t + \delta^{\pm}$  are the total phase,  $V^{\pm}, \omega$ ,  $\delta^{\pm}$ ,  $V_{\alpha 0}$ , and  $V_{\beta 0}$  represent the amplitude, angular frequency, phase angle, and DC offsets in phases  $\alpha$  and  $\beta$ , respectively. The extraction of the FFPS components  $v_{\alpha}^{+} = V^{+}\cos(\theta^{+})$ ,  $v_{\beta}^{+} = V^{+}\sin(\theta^{+})$ ; of the FFNS components  $v_{\alpha}^{-} = V^{-}\cos(\theta^{-})$ ,  $v_{\beta}^{-} = V^{-}\sin(\theta^{-})$ , and of the DC offsets  $V_{\alpha 0}$ ,  $V_{\beta 0}$  are considered in this article. In the sequel, the time-dependence of a signal is often not explicitly stated for convenience. Moreover, continuous- and discrete-time signals may be mixed for brevity.

# 2.1 Delayed signal cancellation based sequence separation

Let us consider the voltage vector of (1), (2) defined as  $\vec{v}_{\alpha\beta} = v_{\alpha} + jv_{\beta}$ . Then, by applying the DSC method, the FFPS and FFNS sequences can be estimated as [35]:

$$\widehat{\vec{v}}_{\alpha\beta}^{+}(t) = \frac{1}{2} \left( \vec{v}_{\alpha\beta}(t) + j \vec{v}_{\alpha\beta} \left( t - \frac{T}{n} \right) \right), \tag{3}$$

$$\widehat{\vec{v}}_{\alpha\beta}(t) = \frac{1}{2} \left( \vec{v}_{\alpha\beta}(t) - j \vec{v}_{\alpha\beta} \left( t - \frac{T}{n} \right) \right), \tag{4}$$

where T is the nominal signal period and n=4 is the delay factor. This delay factor represents a quarter-cycle delay. However, this delay can not block the DC offset. Another DSC operation with n=2 needs to be connected in series ([23]) to block the DC offset. As such, the total delay of sequence separation operation reaches three-quarters of a cycle. To reduce the quarter-cycle delay of sequence separation in the unbiased measurement case, that is, without any DC offset, enhanced DSC is proposed in [28], requiring less than a quarter-cycle delay. Any arbitrary value of n < 4 can be used for sequence

7521424, 0, Downloaded from https://ireresearch.onlinelibrary.wiley.com/doi/10.1049/tpg2.12657 by Test, Wiley Online Library on [2401/2024]. See the Terms and Conditions (https://onlinelibrary.wiley.com/terms-and-conditions) on Wiley Online Library for rules of use; OA articles are governed by the applicable Creative Commons. Licensearch.

AHMED ET AL. 3

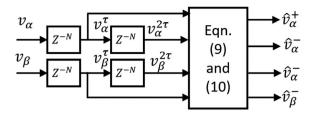

FIGURE 2 Proposed arbitrarily fast modified DSC method

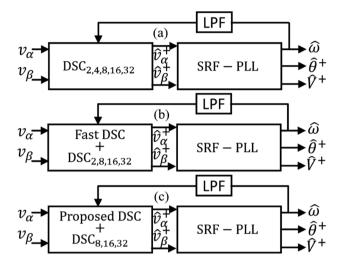

FIGURE 3 DSC-based PLL implementations: (a) conventional CDSC-PLL; (b) fast CDSC-PLL; and (c) proposed method

separation, making this method arbitrarily fast. A simplified version of this tool is proposed in [29]. However, it still requires another DSC operation in-series with n = 2. So, the total delay is less than three-quarters of a cycle but more than half-cycle of the signal period. Higher memory requirements and slow convergence issues are addressed below through our technique.

## 2.2 | Proposed method

To facilitate the calculations, let us write  $v_{\alpha}^{\tau} = v_{\alpha}(t-\tau)$ ,  $v_{\alpha}^{2\tau} = v_{\alpha}(t-2\tau)$ ,  $v_{\beta}^{\tau} = v_{\beta}(t-\tau)$  and  $v_{\beta}^{2\tau} = v_{\beta}(t-2\tau)$ , where the time delay  $\tau = NT_s$  with N being the number of delayed samples and  $T_s$  the sampling time. Then, the grid voltage (1), (2) and its two equidistant delayed samples  $v_{\alpha}^{\tau}$ ,  $v_{\alpha}^{2\tau}$ ,  $v_{\beta}^{\tau}$  and  $v_{\beta}^{2\tau}$  are given by:

$$v_{\alpha}^{\tau}(t) = V_{\alpha 0} + \left(V^{+} \cos\left(\theta^{+}\right) + V^{-} \cos\left(\theta^{-}\right)\right) \cos\left(\phi_{\tau}\right) + \left(V^{+} \sin\left(\theta^{+}\right) + V^{-} \sin\left(\theta^{-}\right)\right) \sin\left(\phi_{\tau}\right), \tag{5a}$$

$$v_{\alpha}^{2\tau}(t) = V_{\alpha 0} + \left(V^{+} \cos\left(\theta^{+}\right) + V^{-} \cos\left(\theta^{-}\right)\right) \cos\left(2\phi_{\tau}\right)$$

$$+ \left(V^{+} \sin\left(\theta^{+}\right) + V^{-} \sin\left(\theta^{-}\right)\right) \sin\left(2\phi_{\tau}\right), \tag{5b}$$

$$v_{\beta}^{\tau}(t) = V_{\beta 0} + \left(V^{+} \sin\left(\theta^{+}\right) - V^{-} \sin\left(\theta^{-}\right)\right) \cos\left(\phi_{\tau}\right)$$

$$+ \left(V^{-} \cos\left(\theta^{-}\right) - V^{+} \cos\left(\theta^{+}\right)\right) \sin\left(\phi_{\tau}\right), \tag{6a}$$

$$\nu_{\beta}^{2\tau}(t) = V_{\beta 0} + \left(V^{+} \sin\left(\theta^{+}\right) - V^{-} \sin\left(\theta^{-}\right)\right) \cos\left(2\phi_{\tau}\right)$$

$$+ \left(V^{-} \cos\left(\theta^{-}\right) - V^{+} \cos\left(\theta^{+}\right)\right) \sin\left(2\phi_{\tau}\right), \tag{6b}$$

where  $\phi_{\tau} = \omega \tau$ . Then, the following algebraic relationship between the sequence components, DC offset, measured voltages, and its two equidistant delayed samples can be obtained as:

$$v = \Phi \Omega,$$

(7)

where

$$\mathbf{v} = \begin{bmatrix} v_{\alpha} & v_{\beta} & v_{\alpha}^{\tau} & v_{\beta}^{\tau} & v_{\alpha}^{2\tau} & v_{\beta}^{2\tau} \end{bmatrix}^{T},$$

$$\mathbf{\Omega} = \begin{bmatrix} V_{\alpha 0} & v_{\alpha}^{+} & v_{\alpha}^{-} & V_{\beta 0} & v_{\beta}^{+} & v_{\beta}^{-} \end{bmatrix}^{T},$$

$$\Phi = \begin{bmatrix} 1 & 1 & 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 & 1 & -1 \\ 1 & c_{\tau} & c_{\tau} & 0 & s_{\tau} & s_{\tau} \\ 0 & -s_{\tau} & s_{\tau} & 1 & c_{\tau} & -c_{\tau} \\ 1 & c_{2\tau} & c_{2\tau} & 0 & s_{2\tau} & s_{2\tau} \\ 0 & -s_{2\tau} & s_{2\tau} & 1 & c_{2\tau} & -c_{2\tau} \end{bmatrix}$$

$c_{\tau} = \cos(\phi_{\tau})$ ,  $c_{2\tau} = \cos(2\phi_{\tau})$ ,  $s_{\tau} = \sin(\phi_{\tau})$ , and  $s_{2\tau} = \sin(2\phi_{\tau})$ . From (7),  $\Omega$  can be estimated as follows:

$$\widehat{\mathbf{\Omega}} = \Phi^{-1} \mathbf{v},\tag{8}$$

where  $\hat{\cdot}$  indicates estimated value and

4 AHMED ET AL.

$$\Phi^{-1} = \begin{bmatrix} \frac{1}{2(1-c_{\tau})} & 0 & \frac{c_{\tau}}{c_{\tau}-1} & 0 & \frac{1}{2(1-c_{\tau})} & 0 \\ \frac{1+c_{\tau}-c_{\tau}^2-2c_{\tau}^3}{2\left(1-c_{\tau}^2\right)} & \frac{1+c_{\tau}-2c_{\tau}^2}{2s_{\tau}} & \frac{2c_{\tau}^2-1}{2(1-c_{\tau})} & \frac{1-2s_{\tau}^2}{2s_{\tau}} & \frac{s_{\tau}^2-1}{2s_{\tau}^2} & -\frac{c_{\tau}}{2s_{\tau}} \\ \frac{c_{\tau}\left(2+c_{\tau}-2c_{\tau}^2\right)}{2\left(c_{\tau}^2-1\right)} & \frac{-\left(c_{\tau}-2c_{\tau}^2+1\right)}{2s_{\tau}} & \frac{1+2c_{\tau}-2c_{\tau}^2}{2(1-c_{\tau})} & \frac{2s_{\tau}^2-1}{2s_{\tau}} & \frac{1+c_{\tau}-c_{\tau}^2}{2\left(c_{\tau}^2-1\right)} & \frac{c_{\tau}}{2s_{\tau}} \\ \frac{1+2c_{\tau}}{2s_{\tau}} & 1 & \frac{-\left(1+c_{\tau}\right)}{s_{\tau}} & 0 & \frac{1}{2s_{\tau}} & 0 \\ \frac{-c_{\tau}\left(1+2c_{\tau}\right)}{2s_{\tau}} & \frac{1}{2}-c_{\tau} & \frac{c_{\tau}\left(1+c_{\tau}\right)}{s_{\tau}} & c_{\tau} & -\frac{c_{\tau}}{2s_{\tau}} & -\frac{1}{2} \\ \frac{-\left(1+c_{\tau}-2c_{\tau}^2\right)}{2s_{\tau}} & c_{\tau}-\frac{1}{2} & s_{\tau} & -c_{\tau} & \frac{c_{\tau}-1}{2s_{\tau}} & \frac{1}{2} \end{bmatrix}$$

By simplifying (8), the sequences can be found as:

$$\hat{v}_{\alpha}^{\pm} = \frac{1}{\gamma} \left( 2s_{\tau} c_{\tau} \left( v_{\alpha} - v_{\alpha}^{\tau} \right) \pm \left( 1 - 2s_{\tau}^{2} \right) \left( v_{\beta} - v_{\beta}^{\tau} \right) \right) \\

\pm c_{\tau} \left( v_{\beta}^{2\tau} - v_{\beta} \right) \pm \left( v_{\beta}^{\tau} - v_{\beta}^{2\tau} \right) + s_{\tau} \left( v_{\alpha}^{2\tau} - v_{\alpha} \right) , \quad (9)$$

$$\hat{v}_{\beta}^{\pm} = \frac{1}{\gamma} \left( \pm 2s_{\tau} c_{\tau} \left( v_{\beta} - v_{\beta}^{\tau} \right) + \left( 1 - 2s_{\tau}^{2} \right) \left( v_{\alpha}^{\tau} - v_{\alpha} \right) \right) \\

c_{\tau} \left( v_{\alpha} - v_{\alpha}^{2\tau} \right) + \left( v_{\alpha}^{2\tau} - v_{\alpha}^{\tau} \right) \pm s_{\tau} \left( v_{\beta}^{2\tau} - v_{\beta} \right) , \quad (10)$$

where  $\gamma = 4s_{\tau}(c_{\tau} - 1)$ . The presented sequence separation equations require few arithmetic operations and are very simple to implement in real-time. As shown in (9) and (10), two trigonometric operations are required to implement the equations. The implementation block diagram of the proposed technique is given in Figure 2.

## 2.3 | Application to phase-locked loop

Sequence separation formulas, as developed in Section 2.2, require the information on actual grid frequency. To obtain the actual grid frequency, CDSC-PLL [23] can be a suitable choice. An overview of the CDSC-PLL is given in Figure 3a. For more details about this PLL, the interested reader may consult [23, 36] and the references therein. In this approach, several DSC blocks are cascaded to eliminate the effect of harmonics and DC offset. Out of the five different DSC blocks, DSC<sub>2</sub> is used to eliminate the effect of DC offset, while DSC<sub>4</sub> is used to extract the FFPS component. These two blocks can be replaced by our method while the other DSC blocks are used as it is. CDSC-

PLL with the proposed sequence extraction formulas is shown in Figure 3c. Directly using the estimated frequency in the DSC blocks can cause instability. A low-pass filter (LPF) is added to ensure stability and to avoid any algebraic loop.

## 3 | RESULTS AND DISCUSSIONS

An overview of the experimental setup used in this work is given in Figure 4. In this setup, a dSPACE 1104 board is used to generate the grid voltage signals. This signal is then passed through digital-to-analog converters (DAC). A Texas Instrument C2000 F28379D digital signal processor (DSP) is used for the practical implementation of the algorithms. These algorithms were exported from Matlab/Simulink using code generation. A sampling frequency of 16 kHz is considered. Experimental results are exported to Matlab for plotting purposes. As comparative techniques, we have selected CDSC-PLL [23] (Figure 3a) and Fast DSC-PLL (FDSC-PLL) (Figure 3b). In the CDSC-PLL, five DSC blocks are used in series namely DSC<sub>2</sub>, DSC<sub>4</sub>, DSC<sub>8</sub>, DSC<sub>16</sub>, and DSC<sub>32</sub>. In FDSC-PLL, only the DSC<sub>4</sub> operator of CDSC-PLL is replaced by the fast DSC method proposed in [28, 29], whereas the remained DSC blocks of CDSC-PLL are kept as it is. Similarly, in the proposed method, only the DSC<sub>2</sub> and DSC<sub>4</sub> blocks are replaced by the developed single DSC block. Parameters of the synchronous reference frame (SRF)-PLL [37] are selected the same for all three techniques. Cut-off frequency of the low-pass filter is selected as 60Hz. To imple-

FIGURE 4 Overview of the experimental setup

AHMED et al.

TABLE 1 Comparative time-domain performance summary

| Performance indicators $\Downarrow$   | CDSC             | FDSC             | Proposed         |

|---------------------------------------|------------------|------------------|------------------|

| Frequency settling time (±0.1Hz) (s)  | 0.94             | 0.0914           | 0.0884           |

| Frequency peak overshoot (Hz)         | 0.35             | 0.26             | 0.18             |

| Phase error settling time (±0.2°) (s) | 0.164            | 0.15             | 0.115            |

| Peak phase error (°)                  | 7.68             | 6.07             | 4.62             |

| FFPS settling time (±0.02 p.u.)       | 0.0168           | 0.016            | 0.0133           |

| FFNS settling time (±0.02 p.u.)       | 0.0172           | 0.0152           | 0.0139           |

| Total delay                           | $\frac{31T}{32}$ | $\frac{27T}{32}$ | $\frac{23T}{32}$ |

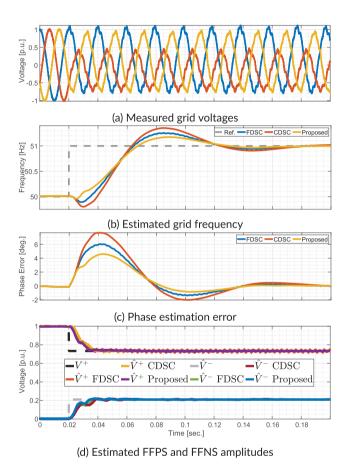

FIGURE 5 Comparative experimental results

ment the proposed DSC method,  $\tau = T/4$  is considered while  $\tau = T/8$  is considered for the fast DSC method. Total delays of the comparative techniques are given in Table 1.

For experimental validation, initially, the grid was balanced. At t=0.02 s, the grid became unbalanced, distorted, and biased. The considered unbalanced grid is composed of  $\vec{v}^{+1}=0.733\angle 0^{\circ}, \vec{v}^{-1}=0.21\angle -45^{\circ}, \vec{v}^{-5}=0.031\angle 45^{\circ}, \ \vec{v}^{+7}=0.028\angle -45^{\circ}, \ \vec{v}^{-11}=0.024\angle 180^{\circ}, \ \vec{v}^{+13}=0.015\angle -180^{\circ}, \ \text{and} \ \vec{v}^{+30\text{Hz}}=0.01\angle 90^{\circ}.$  In addition, DC offsets of 0.15p.u., -0.15p.u, and 0.1p.u. are added to the first, second and third phases of the three-phase voltage signals, respectively. The experimental signal had a signal-to-noise ratio of 38dB. Experimental results are given in Figure 5. In this test, frequency

step change of +1Hz is considered. Despite using the same loop-filter gain for all PLLs, the proposed method has a faster convergence with lower peak overshoot for the frequency estimation, as shown in Figure 5a. Similar performance can be observed for the phase estimation error as well. This is particularly important as the estimated phase is used for reference fame transformation in the control system of grid-connected converter. So, a fast convergence would imply improved stability margin, facilitating a large-scale integration of RES in the power grid. The summary of the results is tabulated in Table 1. Results show that the proposed method has the fastest convergence time and the lowest peak overshoot in all indicators. The estimated FFPS and FFNS amplitudes in Figure 5d show that fast DSC is sensitive to noise and harmonics. However, despite using lower memory than the conventional CDSC method, the steady-state performance of our method is similar to CDSC. So, it can be claimed that the proposed method can help achieve a faster convergence time without sacrificing the steady-state accuracy. The total memory requirement of the proposed method can be reduced further if  $\tau = T/8$  is considered. However, this value amplifies the measurement noise. If the signal is fairly clean and undistorted, we recommend this value. Otherwise,  $\tau = T/4$  can be a suitable choice in the presence of noise and harmonics.

### 4 | CONCLUSION AND FUTURE WORKS

An enhanced delayed signal cancellation method was proposed in this article for the grid-integration of distributed RES. The developed method can easily be integrated into the conventional cascaded delayed signal cancellation phase-locked loop, making it suitable as a grid-synchronization tool for grid-connected converters. The developed approach can estimate FFPS and FFNS components with a fast settling time. The proposed technique can estimate the signals within a fraction of the delay compared to the conventional counterpart being arbitrarily fast. However, a judicious choice must be made for the practical implementation between the convergence time, noise sensitivity, and peak overshoot. Experimental results showed that a total delay of half-cycle is a good choice for the proposed DSC technique in a distorted grid with noisy measurements. The method proposed in this work will ensure a fast and accurate integration of RES into an unbalanced distribution grid.

PLL is an integral part of the grid-connected converter system. Typically, a small-signal model of PLL is required for comprehensive tuning and stability analysis of the converter control system. Developing a small-signal model of the PLL can be considered as a future work. There is a growing interest in the power system community on studying the harmonic distortion caused by supraharmonics (i.e. between 2kHz and 150kHz). Sensitivity analysis of the proposed PLL to suprahramonics can also be considered as future work.

### **AUTHOR CONTRIBUTIONS**

Hafiz Ahmed (GE): Conceptualization, formal analysis, funding acquisition, methodology, software, validation, visualization,

AHMED ET AL.

writing - original draft, writing - review and editing. Rosane Ushirobira: Conceptualization, formal analysis, methodology, supervision, writing - original draft, writing - review and editing. Denis Efimov: Conceptualization, formal analysis, methodology, supervision, writing - original draft, writing - review and editing.

### CONFLICT OF INTEREST

The authors have declared no conflict of interest.

### DATA AVAILABILITY STATEMENT

The data that support the findings of this study are available from the corresponding author upon reasonable request.

### ORCID

Hafiz Ahmed https://orcid.org/0000-0001-8952-4190

### REFERENCES

- Çelik, D.: Lyapunov based harmonic compensation and charging with three phase shunt active power filter in electrical vehicle applications. Int. J. Electr. Power Energy Syst. 136, 107564 (2022)

- Safa, A., Gouichiche, A., Verma, A.K., Su, C.-L., Chedjara, Z., Messlem, Y., Berkouk, E.M.: Open loop synchronization techniques benchmarking for distributed energy sources connection. IEEE Access 10, 63 554–63 566 (2022)

- Ahmed, H., Çelik, D.: Sliding mode based adaptive linear neuron proportional resonant control of Vienna rectifier for performance improvement of electric vehicle charging system. J. Power Sources 542, 231788 (2022)

- Chedjara, Z., Massoum, A., Wira, P., Safa, A., Gouichiche, A.: A fast and robust reference current generation algorithm for three-phase shunt active power filter. Int. J. Power Electron. Drive Syst. 12(1), 121 (2021)

- Chedjara, Z., Massoum, A., Wira, P., Safa, A., Gouichiche, A.: A new quasi open loop synchronization technique for grid-connected applications. Electr. Control Commun. Eng. 17(1), 47–58 (2021)

- Verma, A.K., Jarial, R.K., Roncero-Sánchez, P., Ungarala, M.R., Guerrero, J.M.: An improved hybrid prefiltered open-loop algorithm for three-phase grid synchronization. IEEE Trans. Ind. Electron. 68(3), 2480–2490 (2021)

- Meral, M.E., Çelík, D.: A comprehensive survey on control strategies of distributed generation power systems under normal and abnormal conditions. Annu. Rev. Control. 47, 112–132 (2019)

- 8. Verma, A.K., Subramanian, C., Jarial, R.K., Roncero-Sánchez, P., Rao, U.M.: A robust Lyapunov demodulator for tracking of single-/three-phase grid voltage variables. IEEE Trans. Instrum. Meas. 70, 1–11 (2020)

- Safa, A., Berkouk, E.M., Messlem, Y., Chedjara, Z., Gouichiche, A.: A pseudo open loop synchronization technique for heavily distorted grid voltage. Electr. Power Syst. Res. 158, 136–146 (2018)

- Klusacek, J., Drapela, J., Langella, R.: Power symmetrical components as grid usage indicator for unbalanced prosumers. In: 2022 20th International Conference on Harmonics & Quality of Power (ICHQP), pp. 1–6. IEEE, Piscataway (2022)

- Pereira, O., Quiros-Tortos, J., Valverde, G.: Phase rebalancing of distribution circuits dominated by single-phase loads. IEEE Trans. Power Syst. 36(6), 5333–5344 (2021)

- Nuno Fidalgo, J., Moreira, C., Cavalheiro, R.: Impact of load unbalance on low voltage network losses. In: 2019 IEEE Milan PowerTech, pp. 1–5. IEEE, Piscataway (2019)

- Elyasichamazkoti, F., Aminifar, F., Davarpanah, M.: Digital filter-based grid synchronization for autonomous microgrids. IET Renew. Power Gener. 15(15), 3732–3742 (2021)

- Abdul Basit, B., Nguyen, A.T., Ryu, S.-W., Park, H., Jung, J.-W.: A state-of-the-art comprehensive review of modern control techniques for grid-connected wind turbines and photovoltaic arrays distributed generation systems. IET Renew. Power Gener. 16(11), 2191–2222 (2022)

Ahmed, H., Ushirobira, R., Efimov, D.: On biased harmonic signal estimation: Application to electric power grid monitoring. IEEE Trans. Control Syst. Technol. 30(6), 2743–2750 (2022)

- Hamdi, M., Hamouda, M.: A short review of grid voltage sags and current control techniques of voltage source inverters in distributed power generation systems. In: Renewable Energy Production and Distribution, pp. 415–445. Academic Press, London (2022). https://doi.org/10.1016/b978-0-323-91892-3.00012-1

- Benyamina, F., Benrabah, A., Khoucha, F., Zia, M.F., Achour, Y., Benbouzid, M.: An augmented state observer-based sensorless control of grid-connected inverters under grid faults. Int. J. Electr. Power Energy Syst. 133, 107222 (2021)

- Benyamina, F., Benrabah, A., Khoucha, F., Zia, M.F., Achour, Y., Benbouzid, M.: Online current limiting-based control to improve fault ride-through capability of grid-feeding inverters. Electr. Power Syst. Res. 201, 107524 (2021)

- Biricik, S., Komurcugil, H., Tuyen, N.D., Basu, M.: Protection of sensitive loads using sliding mode controlled three-phase DVR with adaptive notch filter. IEEE Trans. Ind. Electron. 66(7), 5465–5475 (2018)

- Özer, A.S., Sevilmiş, F., Karaca, H., Arabacı, H.: Enhanced control method for voltage regulation of dstatcom based seig. Energy Rep. 8, 839–847 (2022)

- Sevilmiş, F., Karaca, H.: Implementation of enhanced non-adaptive cascaded DSC-PLLs for renewable energy systems. Int. J. Electr. Power Energy Syst. 134, 107470 (2022)

- Alturki, M., Abbassi, R., Albaker, A., Jerbi, H.: A new hybrid synchronization PLL scheme for interconnecting renewable energy sources to an abnormal electric grid. Math. 10(7), 1101 (2022)

- Wang, Y.F., Li, Y.W.: Grid synchronization PLL based on cascaded delayed signal cancellation. IEEE Trans. Power Electron. 26(7), 1987–1997 (2011)

- Wang, Y.F., Wei Li, Y.: Analysis and digital implementation of cascaded delayed-signal-cancellation pll. IEEE Trans. Power Electron. 26(4), 1067– 1080 (2011)

- Ahmed, H., Ushirobira, R., Efimov, D.: Robust estimation of fundamental frequency positive-sequence component for grid-integration applications in energy systems. Energy Rep. 8, 357–363 (2022)

- Contreras, C., Guajardo, D., Diaz, M., Rojas, F., Espinoza, M., Cardenas, R.: Fast delayed signal cancellation based pll for unbalanced grid conditions. In: 2018 IEEE International Conference on Automation/XXIII Congress of the Chilean Association of Automatic Control (ICA-ACCA), pp. 1–6. IEEE, Piscataway (2018)

- Cárdenas, R., Díaz, M., Rojas, F., Clare, J., Wheeler, P.: Resonant control system for low-voltage ride-through in wind energy conversion systems. IET Power Electron. 9(6), 1297–1305 (2016)

- Cardenas, R., Rojas, F., Clare, J., et al.: Fast convergence delayed signal cancellation method for sequence component separation. IEEE Trans. Power Del. 30(4), 2055–2057 (2015)

- Mellouli, M.S., Hamouda, M., Slama, J.B.H., Al Haddad, K.: A third-order MAF based QT1-PLL that is robust against harmonically distorted grid voltage with frequency deviation. IEEE Trans. Energy Convers. 36(3), 1600–1613 (2021)

- Ciobotaru, M., Teodorescu, R., Agelidis, V.G.: Offset rejection for PLL based synchronization in grid-connected converters. In: 2008 Twenty-Third Annual IEEE Applied Power Electronics Conference and Exposition, pp. 1611–1617. IEEE, Piscataway (2008)

- Stringer, N.: The effect of DC offset on current-operated relays. IEEE Trans. Ind. Appl. 34(1), 30–34 (1998)

- Nam, S.-R., Park, J.-Y., Kang, S.-H., Kezunovic, M.: Phasor estimation in the presence of DC offset and CT saturation. IEEE Trans. Power Delivery 24(4), 1842–1849 (2009)

- Hwang, S.-H., Liu, L., Li, H., Kim, J.-M.: DC offset error compensation for synchronous reference frame PLL in single-phase grid-connected converters. IEEE Trans. Power Electron. 27(8), 3467–3471 (2012)

- Du, L., Li, M., Tang, Z., Xiong, L., Ma, X., Tang, G.: A fast positive sequence components extraction method with noise immunity in unbalanced grids. IEEE Trans. Power Electron. 35(7), 6682–6685 (2019)

17521424, 0, Downloaded from https://ieresearch.onlinelibrary.wiley.com/doi/10.1049/pgg.1.2657 by Test, Wiley Online Library on [2401/2024]. See the Terms and Conditions (https://onlinelibrary.wiley.com/errms-and-conditions) on Wiley Online Library for rules of use; OA articles are governed by the applicable Creative Commons Licensearch

AHMED ET AL.

Svensson, J., Bongiorno, M., Sannino, A.: Practical implementation of delayed signal cancellation method for phase-sequence separation. IEEE Trans. Power Delivery 22(1), 18–26 (2007)

- Ullah, I., Ashraf, M.: Comparison of synchronization techniques under distorted grid conditions. IEEE Access 7, 101 345–101 354 (2019)

- 37. Kaura, V., Blasko, V.: Operation of a phase locked loop system under distorted utility conditions. IEEE Trans. Ind. Appl. 33(1), 58–63 (1997)

How to cite this article: Ahmed, H., Ushirobira, R., Efimov, D.: Arbitrarily fast delayed signal cancellation PLL for grid-integration of renewable energy sources. IET Renew. Power Gener. 1–7 (2022). https://doi.org/10.1049/rpg2.12657