This is a repository copy of *Effect of SiO2 surface passivation on the performance of GaN polarization superjunction heterojunction field effect transistors*.

White Rose Research Online URL for this paper: <u>https://eprints.whiterose.ac.uk/207128/</u>

Version: Published Version

# Article:

Du, Y., Madathil, S.N.E. orcid.org/0000-0001-6832-1300, Kawai, H. et al. (2 more authors) (2023) Effect of SiO2 surface passivation on the performance of GaN polarization superjunction heterojunction field effect transistors. physica status solidi (a). ISSN 1862-6300

https://doi.org/10.1002/pssa.202300199

## Reuse

This article is distributed under the terms of the Creative Commons Attribution-NonCommercial-NoDerivs (CC BY-NC-ND) licence. This licence only allows you to download this work and share it with others as long as you credit the authors, but you can't change the article in any way or use it commercially. More information and the full terms of the licence here: https://creativecommons.org/licenses/

## Takedown

If you consider content in White Rose Research Online to be in breach of UK law, please notify us by emailing eprints@whiterose.ac.uk including the URL of the record and the reason for the withdrawal request.

eprints@whiterose.ac.uk https://eprints.whiterose.ac.uk/

www.pss-a.com

Check for updates

a

# Effect of SiO<sub>2</sub> Surface Passivation on the Performance of GaN Polarization Superjunction Heterojunction Field Effect Transistors

Yangming Du, Sankara Narayanan Ekkanath Madathil,\* Hiroji Kawai, Shuichi Yagi, and Hironobu Narui

In this article, the effects of the SiO<sub>2</sub> surface passivation layer are reported on normally-on 1.2 kV GaN polarization superjunction (PSJ) heterojunction field effect transistors (HFETs) by comparing the electrical performances of PSJ HFETs with and without SiO<sub>2</sub> surface passivation. A slight recovery of the 2D electron gas sheet density is observed in the slight negative shift of  $V_{th}$  after SiO<sub>2</sub> surface passivation. Passivation also increases the breakdown voltage. This improvement may result from removing positive surface charges in defects along the P-GaN gate sidewall and top u-GaN layer after the specifically designed SiO<sub>2</sub> surface passivation. Furthermore, the SiO<sub>2</sub> surface passivation can also effectively suppress the surface gate leakage currents in the PSJ HFETs by eliminating the conductive channel created by the positive surface charges in defects.

## 1. Introduction

Gallium nitride (GaN) has become one of the most competitive materials for power semiconductor devices due to the high mobility and high density of the 2D electron gas (2DEG)<sup>[1]</sup> formed at the heterointerface of AlGaN/GaN.

Polarization superjunction (PSJ) concept is based on the charge balance of polarization effects of high-density 2DEG with 2D hole gas (2DHG), enabling GaN HEMTs to achieve high breakdown voltage without sacrificing the on-state resistance. High densities of 2DHG and 2D electron gas naturally coexist

Y. Du, S. N. E. Madathil Department of Electronic and Electrical Engineering The University of Sheffield, Sheffield Sir Frederick Mappin Building, Mappin Street S1 3JD, UK E-mail: s.madathil@sheffield.ac.uk H. Kawai, S. Yagi, H. Narui

Powdec K.K 1-23-15 Wakagi-cho, Oyama City, Tochigi 323-0028, Japan

The ORCID identification number(s) for the author(s) of this article can be found under https://doi.org/10.1002/pssa.202300199.

© 2023 The Authors. physica status solidi (a) applications and materials science published by Wiley-VCH GmbH. This is an open access article under the terms of the Creative Commons Attribution-NonCommercial-NoDerivs License, which permits use and distribution in any medium, provided the original work is properly cited, the use is non-commercial and no modifications or adaptations are made.

#### DOI: 10.1002/pssa.202300199

at the respective interfaces of the GaN  $(000\overline{1})/\text{AlGaN}$  (000 $\overline{1}$ ) and AlGaN (000 $\overline{1}$ )/ GaN (0001) double heterostructure, achieving charge balance conditions in the offstate and a flat electric field distribution in the drift region.<sup>[2]</sup> A theoretical tradeoff relationship between specific on-state resistance and breakdown voltage for PSJ power devices has been proposed in ref. [3]. Recent research has shown that the breakdown voltages of the PSJ heterojunction field effect transistors (HFETs) can be linearly increased with the length of the PSJ region.<sup>[2,4,5]</sup> The switching performance of GaN PSI HFETs is similar to that of Si superjunction metal-oxidesemiconductor field-effect transistors

(MOSFETs).<sup>[2]</sup> When the PSJ HFET turns on, the electrons flow via the 2DEG between source and drain to enable current flow. When the device is turned off, along with the extraction of electrons from the drift region, the extraction of 2DHG present over the drift region via the gate causes the formation of a depletion region to support the drain voltage in the drift region.

It is widely accepted that the donor defect states, and bulk donors are the causes of the 2DEG both in the AlGaN/GaN and u-GaN/AlGaN/u-GaN heterostructures.<sup>[6,7]</sup> In the u-GaN/AlGaN/ u-GaN heterostructures, when the GaN cap layer is thin, the effects of 2DEG sheet density are dominated by the surface donor states. However, when the u-GaN layer increases, the 2DEG sheet density decreases which is due to the introduction of the negative polarization charges at the heterointerface of the top u-GaN.<sup>[7]</sup>

Several literatures have reported the impact of SiO<sub>2</sub> surface passivation on the basic electrical performance of AlGaN/GaN HEMTs.<sup>[8–11]</sup> With SiO<sub>2</sub> surface passivation, improved on-state resistances and saturation currents are observed, with negatively shifted  $V_{\rm th}$ .<sup>[11–13]</sup> This is due to the suppression of surface trap effects in the AlGaN/GaN HEMTs. Another explanation for the increase in the 2DEG carrier concentration is reported in ref. [14], which suggests that the charges existing at the oxide/ AlGaN interface or the oxide are responsible. Moreover, surface passivation can also influence the switching performances and current collapse in GaN power devices.<sup>[13,15–17]</sup> It has been found that the breakdown voltage of AlGaN/GaN HEMTs increases following SiO<sub>2</sub> passivation<sup>[18]</sup> due to the suppression of surface electron trapping.

However, the SiO<sub>2</sub> surface passivation and its effects on the 2DEG and 2DHG sheet density in PSJ HFETs have not been explored due to the presence of the top u-GaN layer. This study aims to analyze the impacts of SiO<sub>2</sub> surface passivation on both the sheet density of 2DHG and 2DEG and their further influences on the transfer, on-state, breakdown voltage, and gate leakage current performances in PSJ HFETs.

## 2. Device Structures and Parameters

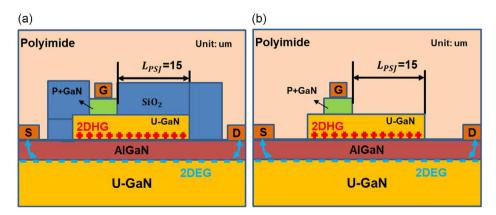

The devices under test are 1.2 kV normally-on p-GaN Ohmic gate PSI HFETs fabricated on the sapphire substrate. PSI heterostructures consist of GaN/AlGaN/GaN shown in Figure 1. They are capped with a P+GaN layer with a Mg doping density of 1e20 cm<sup>-3</sup> to achieve an Ohmic gate metal contact to assist the transportation of 2DHG. The source and drain electrodes are above the AlGaN layer, forming the Ohmic contact with 2DEG. The thickness of the AlGaN layer is 47 nm and the content of Al is 0.23. The top and bottom undoped GaN layers are 20 nm and 1 µm, respectively. Therefore, 2DHG, an undoped AlGaN layer, and 2DEG compose the vertical PiN junction. Figure 1a shows the cross section of PSJ HFETs with the SiO<sub>2</sub> surface passivation. As a comparison, the PSJ HFETs without the SiO<sub>2</sub> passivation are shown in Figure 1b. Polyamide is deposited on the active area of the devices for protection and isolation. The other dimensions and details of the devices are presented in Figure 1a,b. The gate width of them is 1 mm.

### 3. Results and Discussions

#### 3.1. Impact on the Transfer and $I_{ds}-V_{ds}$ Characteristics

In this section, the effects of SiO<sub>2</sub> surface passivation on the transfer and  $I_{\rm ds}$ – $V_{\rm ds}$  characteristics are evaluated. The static characteristics of the devices were measured using a Keysight B1500A Semiconductor Device tester, and all tests were conducted in dark conditions at room temperature.

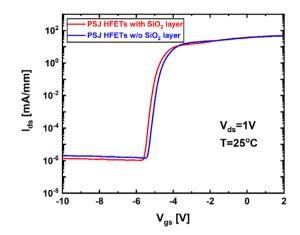

**Figure 2** shows that the  $V_{\rm th}$  for PSJ HFETs with SiO<sub>2</sub> surface passivation is lower and more negative than those without SiO<sub>2</sub> passivation, with values of  $V_{\rm th} = -5.71$  and -5.5 V (extracted at 1 mA mm<sup>-1</sup>), respectively. This difference is because SiO<sub>2</sub>

www.pss-a.com

**Figure 2.** Typical transfer characteristics ( $I_{ds} - V_{gs}$ ) of the PSJ HFETs with and without SiO<sub>2</sub> surface passivation were measured at  $V_{ds} = 1$  V.

surface passivation reduces the influence from the defect states located along the P-GaN sidewall and PSJ region or the charges at the surface of oxide/u-GaN or in the oxide layer causes the increase of the 2DEG sheet density.<sup>[14]</sup> However, due to the existence of a thick top u-GaN layer, only a slight recovery of the 2DEG could be seen based on the slight negative  $V_{\rm th}$  shift observed after surface passivation.

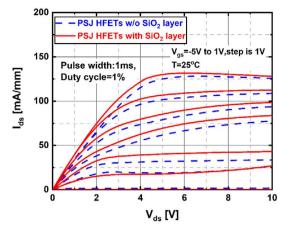

A typical measured pulsed  $I_{ds}-V_{ds}$  is shown in **Figure 3**. It was found that  $R_{on}$  for PSJ HFETs with SiO<sub>2</sub> passivation is relatively lower than devices without it. This is due to a marginal recovery of the 2DEG density.<sup>[7,19]</sup>

#### 3.2. Breakdown Voltage Characteristics

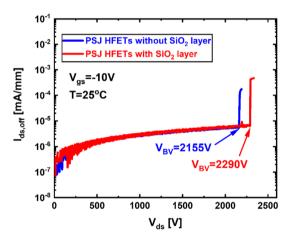

This section describes improvement in the breakdown voltage of PSJ HFETs after the passivation of the SiO<sub>2</sub> surface and explores possible causes. The B1505A Semiconductor Device Analyzer was used to measure their typical off-state breakdown characteristics, displayed in **Figure 4**. The PSJ HFET with SiO<sub>2</sub> surface passivation had a breakdown voltage of 2290 V, which was 145 V higher than that without passivation. The improvement in the breakdown

**Figure 1.** The cross section of the polarization superjunction (PSJ) P-GaN Ohmic gate heterojunction field effect transistors (HFETs) a) with and b) without SiO<sub>2</sub> spacer along the sidewall of the P-GaN gate and the whole top U-GaN layer.

**Figure 3.** Typical pulsed  $I_{ds} - V_{ds}$  characteristics of the PSJ HFETs with and without SiO<sub>2</sub> surface passivation measured at  $V_{gs} = -5-1$  V (gate step voltage = 1 V, pulse width = 1 ms, and the duty cycle is 1%).

Figure 4. The comparison results of the typical off-state breakdown characteristics of PSJ HFETs with and without the SiO<sub>2</sub> passivation layer (at  $V_{\rm gs}=-10$  V).

voltage is assumed to be caused by removing possible positive surface charges in defects along the top u-GaN layer.

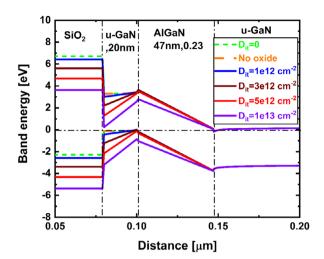

Surface passivation influences the sheet density of 2DEG by modulating the positive surface charge in defects in AlGaN/GaN HEMTs. The positive surface charge in defects at the AlGaN surface influences the concentration of 2DEG by modifying the surface potential in AlGaN/GaN HEMTs, as reported in ref. [20]. Furthermore, the effect of the surface charge in defects on the DC characteristics is investigated through the TCAD simulations.<sup>[19,21-26]</sup> Therefore, following a similar analysis, the trend analysis of the passivation effects with various positive surface charges in defects  $(D_{it})$  on the sheet density of 2DEG and 2DHG is presented and discussed for the PSJ heterostructures. Detailed device simulation was undertaken to identify the effects of different densities of donor and acceptor defect states modeled as positive sheet charges at the interface of the top u-GaN layer and SiO<sub>2</sub> on the band bending and sheet density of 2DEG and 2DHG. The models employed in this simulation were based on

www.pss-a.com

**Figure 5.** The schematic band diagram of PSJ heterostructures (u-GaN/AlGaN/u-GaN) with/without SiO<sub>2</sub> (including various positive surface charges in defects,  $D_{it}$ ) passivation.

the previously reported PSJ simulation model in ref. [27]. The similar surface charges in defects are based on the research work of refs. [20,28].

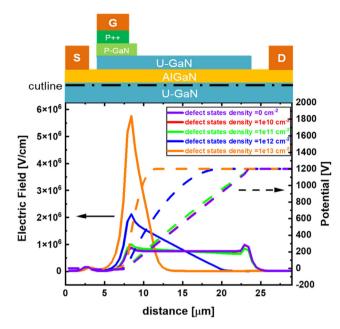

The band diagram of the PSJ heterostructures with and without the SiO<sub>2</sub> passivation layer is shown in Figure 5. It also illustrates the scenario of a SiO2 passivation layer with different positive surface charges in defects, which represent the different levels of surface passivation effects. From the band diagram, it can be observed that the surface potential becomes lower with the increase in the positive surface charges in defects, which is like that reported in the AlGaN/GaN HEMTs.<sup>[20]</sup> With the increase of the positive surface charge on the top u-GaN, the surface electronic potential drops. Figure 5 shows the band bending as defect density is increased from 0 to  $1e13 \text{ cm}^{-2}$ . Due to the existence of a thick top u-GaN layer and AlGaN barrier layer, the band bending has marginal effects on the AlGaN/GaN hetero-barriers and the sheet density of 2DEG but can cause the hole density in the 2DHG to decrease significantly. For the extremely high defect density of  $1e13 \text{ cm}^{-2}$ , the 2DHG is almost fully depleted as seen from the valence band dropping below the Fermi level (Figure 5). The simulated electric field and potential distribution along the 2D electron gas (2DEG) channel of the PSJ HFETs with various positive surface charges in defects ranging from 0 to 1e13 cm<sup>-2</sup> at  $V_{\rm gs} = -10V$  and  $V_{\rm ds} = 1200$  V are shown in Figure 6.

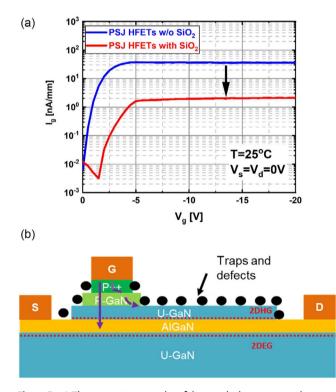

#### 3.3. Suppression of the Gate Leakage Current in the PSJ HFETs

Recently,  $SiO_2$  passivation for P-GaN gate HFETs has been proposed to reduce surface leakage current.<sup>[8,9]</sup> Surface gate leakage current can be reduced by introducing the SiO<sub>2</sub> passivation layer, which also leads to suppressing carrier trapping through positive surface charges in defects and removing the conductive channel<sup>[29–31]</sup> from the gate to the source and drain. The surface leakage current 2D variable range hopping mechanism is one of the possible but important mechanisms of the surface leakage current reported in ref. [31].

**Figure 6.** The modulus of electric field and potential distribution along the 2D electron gas (2DEG) channel of the PSJ HFETs with various positive surface charges in defects ranging from 0 to 1e13 cm<sup>-2</sup> at  $V_{gs} = -10$  V and  $V_{ds} = 1200$  V.

**Figure 7.** a) The comparison results of the gate leakage current characteristics of PSJ HFETs with and without the SiO<sub>2</sub> passivation layer. b) The mechanisms of the surface gate leakage current formation through positive surface charges in defects in PSJ HFETs.

The SiO<sub>2</sub> passivation process has been developed along the sidewall of the P-GaN gate and the top U-GaN layer in PSJ HFETs shown in Figure 1a. Gate leakage current characteristics of PSJ HFETs are shown in Figure 7a. The negative gate bias is applied at the gate (from 0 to -20 V) and the source and drain are grounded. There is a significant reduction in Ig from 36 to 1.94 nA at  $V_g = -10$  V. The gate leakage current of PSJ HFETs is composed of the surface leakage current and vertical PiN junction reverse current.<sup>[31]</sup> Vertical PiN reverse junction current is dominated by the space-charge generation current which is mainly dependent on the AlGaN layer (intrinsic layer),<sup>[32]</sup> representing that SiO<sub>2</sub> surface passivation has negligible effects on it. Therefore, the reduction of gate leakage is mainly induced by the surface leakage current through effectively suppressing positive surface charges in defects with SiO<sub>2</sub> surface passivation in PSJ HFETs, which is like the mechanisms of the P-GaN HEMTs presented in Figure 7b. These results also indicate that the states are located along the surface instead of the u-GaN layer.

## 4. Conclusion

The effect of SiO<sub>2</sub> surface passivation along the sidewall of the P-GaN gate and the top u-GaN layer on the electrical performance of the 1.2 kV normally-on P-GaN gate PSJ HFETs is studied. SiO<sub>2</sub> passivation leads to a slight improvement in the on-state resistance and a marginally negative  $V_{\rm th}$  shift. This is due to the marginally recovered sheet density of 2DEG after SiO<sub>2</sub> passivation. However, the crucial role of SiO<sub>2</sub> passivation lies in maintaining the high density of 2DHG by removing the positive surface charges in defects. It is essential to remove the positive surface charges in defects and maintain the high density of the 2DHG. This is an important process step to optimize the electric field distribution and achieve charge balancing between 2DEG and 2DHG in the off-state, significantly enhancing the breakdown voltage. Furthermore, SiO2 surface passivation is necessary to reduce the gate leakage current by eliminating the conductive channel which is formed by the positive surface charges in defects from gate to source or drain.

# Acknowledgements

The author would like to acknowledge the support from POWDEC.K.K, Japan, for providing the samples and academic comments in this article.

# Conflict of Interest

The authors declare no conflict of interest.

## Data Availability Statement

The data that support the findings of this study are available from the corresponding author upon reasonable request.

IDVANCED

## Keywords

GaN, heterojunction field effect transistors, polarizations, superjunctions, surface passivations

Received: March 16, 2023 Revised: November 22, 2023 Published online:

- M. Asif Khan, A. Bhattarai, J. N. Kuznia, D. T. Olson, *Appl. Phys. Lett.* 1993, 63, 1214.

- [2] H. Kawai, S. Yagi, S. Hirata, F. Nakamura, T. Saito, Y. Kamiyama, M. Yamamoto, H. Amano, V. Unni, E. M. S. Narayanan, *Phys. Status Solidi A* **2017**, *214*, 1600834.

- [3] A. Nakajima, K. Adachi, M. Shimizu, H. Okumura, Appl. Phys. Lett. 2006, 89, 193501.

- [4] A. Nakajima, Y. Sumida, M. H. Dhyani, H. Kawai, E. M. Narayanan, IEEE Electron Device Lett. 2011, 32, 542.

- [5] V. Unni, H. Y. Long, M. Sweet, A. Balachandran, S. E. Madathil, A. Nakajima, H. Kawai, in 2014 IEEE 26th Int. Symp. on Power Semiconductor Devices & IC's (ISPSD), IEEE, Piscataway, NJ 2014, pp. 245–248.

- [6] J. P. Ibbetson, P. T. Fini, K. D. Ness, S. P. DenBaars, J. S. Speck, U. K. Mishra, Appl. Phys. Lett. 2000, 77, 250.

- [7] S. Heikman, S. Keller, Y. Wu, J. S. Speck, S. P. DenBaars, U. K. Mishra, J. Appl. Phys. 2003, 93, 10114.

- [8] S. A. Chevtchenko, M. A. Reshchikov, Q. Fan, X. Ni, Y. T. Moon, A. A. Baski, H. Morkoç, J. Appl. Phys. 2007, 101, 113709.

- [9] D. Gregušová, J. Bernát, M. Držík, M. Marso, J. Novák, F. Uherek, P. Kordoš, Phys. Status Solidi C 2005, 2, 2619.

- [10] J. Bernát, P. Javorka, A. Fox, M. Marso, H. Lüth, P. Kordoš, Solid State Electron. 2003, 47, 2097.

- [11] S. Arulkumaran, T. Egawa, H. Ishikawa, T. Jimbo, Y. Sano, *Appl. Phys. Lett.* 2004, 84, 613.

- [12] W. S. Tan, P. A. Houston, P. J. Parbrook, G. Hill, R. J. Airey, J. Phys. D Appl. Phys. 2002, 35, 595.

- [13] M. Gassoumi, H. Mosbahi, M. A. Zaidi, C. Gaquière, H. Maaref, Semiconductors 2013, 47, 1008.

- [14] W. Wang, J. Derluyn, M. Germain, M. Leys, S. Degroote, D. Schreurs, G. Borghs, Jpn. J. Appl. Phys 2006, 45, L224.

- [15] N. Zhang, B. Moran, S. P. DenBaars, U. K. Mishra, X. W. Wang, T. P. Ma, in Inter. Electron Devices Meeting. Technical Digest (Cat. No.01CH37224), Washington, DC, USA 2001, pp. 25.5.1–25.5.4.

- 18626319, 0, Downloaded from https://onlinelibrary.wiley.com/doi/10.1002/pssa.202300199 by University Of Sheffield, Wiley Online Library on [05/01/2024]. See the Terms and Conditions (https://onlinelibrary.wiley.com/ -andon Wiley Online Library for rules of use; OA articles are governed by the applicable Creative Commons I

- [16] R. Vetury, N. Q. Zhang, S. Keller, U. K. Mishra, IEEE Trans. Electron. Devices 2001, 48, 560.

- [17] B. Luo, R. Mehandru, J. Kim, F. Ren, B. P. Gila, A. H. Onstine, C. R. Abernathy, S. J. Pearton, R. Fitch, J. Gillespie, T. Jenkins, J. Sewell, D. Via, A. Crespo, Y. Irokawa, in *Proc. IEEE Lester Eastman Conf. on High Performance Devices*, IEEE, Piscataway, NJ **2002**, pp. 477–486.

- [18] M.-W. Ha, S.-C. Lee, J.-H. Park, J.-C. Her, K.-S. Seo, M.-K. Han, in *IEEE Int. Symp. on Power Semiconductor Devices and IC's*, IEEE, Piscataway, NJ 20062006, pp. 1–4.

- [19] G. Longobardi, F. Udrea, S. Sque, G. A. M. Hurkx, J. Croon, E. Napoli, J. Šonský, IEEE Electron. Device Lett. 2014, 35, 27.

- [20] P. K. Kaushik, S. K. Singh, A. Gupta, A. Basu, E. Y. Chang, Nanoscale Res. Lett 2021, 16, 159.

- [21] C. Miccoli, V. C. Martino, S. Reina, S. Rinaudo, IEEE Electron. Device Lett. 2013, 34, 1121.

- [22] B. Bakeroot, S. You, T.-L. Wu, J. Hu, M. Van Hove, B. De Jaeger, K. Geens, S. Stoffels, S. Decoutere, *J. Appl. Phys.* **2014**, *116*, 134506.

- [23] C. Mizue, Y. Hori, M. Miczek, T. Hashizume, Jpn. J. Appl. Phys. 2011, 50, 021001.

- [24] G. Meneghesso, G. Verzellesi, R. Pierobon, F. Rampazzo, A. Chini, U. K. Mishra, C. Canali, E. Zanoni, *IEEE Trans. Electron. Devices* 2004, 51, 1554.

- [25] M. Wespel, M. Baeumler, V. Polyakov, M. Dammann, R. Reiner, P. Waltereit, R. Quay, M. Mikulla, O. Ambacher, *Microelectron. Reliab.* 2014, 54, 2656.

- [26] G. Longobardi, F. Udrea, IEEE Trans. Electron. Devices 2017, 64, 4415.

- [27] V. Unni, H. Y. Long, H. Yan, A. Nakajima, H. Kawai, E. M. S. Narayanan, IET Power Electronics 2018, 11, 2198.

- [28] W. Amir, J.-W. Shin, K.-Y. Shin, J.-M. Kim, C.-Y. Cho, K.-H. Park, T. Hoshi, T. Tsutsumi, H. Sugiyama, H. Matsuzaki, T.-W. Kim, *Sci. Rep.* **2021**, *11*, 22401.

- [29] P. Liu, C. Xie, F. Zhang, J. Chen, D. Chen, IEEE Electron. Device Lett. 2013, 34, 1232.

- [30] A. Stockman, E. Canato, A. Tajalli, M. Meneghini, G. Meneghesso, E. Zanoni, P. Moens, B. Bakeroot, in 2018 IEEE Int. Reliability Physics Symp. (IRPS), IEEE, Piscataway, NJ 2018, pp. 4B.5-1–4B.5-4.

- [31] N. Xu, R. Hao, F. Chen, X. Zhang, H. Zhang, P. Zhang, X. Ding, L. Song, G. Yu, K. Cheng, Y. Cai, B. Zhang, *Appl. Phys. Lett.* **2018**, *113*, 152104.

- [32] B. J. Baliga, in Fundamentals of Power Semiconductor Devices, 1st ed., Springer, New York 2008.