This is a repository copy of Soft switching voltage regulation for inductorless piezoelectric transformers: a cyclic mode analysis.

White Rose Research Online URL for this paper: <a href="https://eprints.whiterose.ac.uk/202633/">https://eprints.whiterose.ac.uk/202633/</a>

Version: Accepted Version

#### Article:

Yang, Z. orcid.org/0000-0001-8647-9099, Forrester, J. orcid.org/0000-0002-8102-7576, Davidson, J.N. orcid.org/0000-0002-6576-3995 et al. (2 more authors) (2023) Soft switching voltage regulation for inductorless piezoelectric transformers: a cyclic mode analysis. IEEE Transactions on Power Electronics, 38 (12). pp. 15645-15658. ISSN 0885-8993

https://doi.org/10.1109/tpel.2023.3305558

© 2023 The Authors. Except as otherwise noted, this author-accepted version of a journal article published in IEEE Transactions on Power Electronics is made available via the University of Sheffield Research Publications and Copyright Policy under the terms of the Creative Commons Attribution 4.0 International License (CC-BY 4.0), which permits unrestricted use, distribution and reproduction in any medium, provided the original work is properly cited. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/

## Reuse

This article is distributed under the terms of the Creative Commons Attribution (CC BY) licence. This licence allows you to distribute, remix, tweak, and build upon the work, even commercially, as long as you credit the authors for the original work. More information and the full terms of the licence here: https://creativecommons.org/licenses/

# Takedown

If you consider content in White Rose Research Online to be in breach of UK law, please notify us by emailing eprints@whiterose.ac.uk including the URL of the record and the reason for the withdrawal request.

# Soft switching voltage regulation for inductorless piezoelectric transformers: a cyclic mode analysis

Zijiang Yang<sup>1</sup>, Jack Forrester, Jonathan N. Davidson, Martin P. Foster and David A. Stone

Abstract-This paper describes a novel methodology for predicting the ability of an inductorless driven piezoelectric transformer (PT)-based H-bridge inverters to simultaneously achieve zero-voltage switching and output regulation. A new idea for output voltage regulation by controlling deadtime interval is presented. A model is derived using cyclic-mode analysis to estimate the state-variable parameters of the circuit for a given operating condition. The model is then used to demonstrate operation in the zero-voltage switching (ZVS) region and to estimate the deadtime period, load and operating frequency along the ZVS boundary. The output voltage regulation profile is presented and regions where voltage regulation can be continuously achieved while still obtaining ZVS are shown. Both SPICE simulation and experimental results taken using a ring-dot radial-mode PT are presented as verification. The proposed method for a H-bridge PT-based inverter is able to achieve a 5V output from 15V-60V input with simultaneous ZVS and voltage regulation.

#### I. INTRODUCTION

Piezoelectric transformers (PTs) have raised great research interest over the past few years, and are an exciting alternative to traditional magnetic transformers owing to the advantages in low electromagnetic interference (EMI), high power density (>40W/cm³), high efficiency, reduced weight and simpler manufacturing process [1]–[4]. PTs exhibit high quality factor since they are constructed from high-quality factor materials, such as lead zirconate titanate (PZT), and so are excellent devices for power electronics applications [5]–[8]. By using the electro-mechanical properties of the piezoelectric materials, the energy is transferred from the input to the output electrodes via mechanical vibrations. PTs normally operate in a narrow frequency band close to their primary resonant frequency, and the optimum operating frequency is dependent on parameters such as temperature, load, vibration mode and geometry [1][5][9].

Several circuit topologies have been reported in the literature to drive PTs, such as class-E, push-pull and half-bridge [1][5][10]. However, zero-voltage switching (ZVS) is difficult to achieve due to the large input capacitance of the PT and limited availability of the resonant current. Thus, careful consideration should be taken when designing the control circuit and PT to ensure that sufficient current is available to

charge the PT input capacitance to the DC (direct current) rail during the necessary deadtime period [10][11]. If the deadtime interval is too small or the amplitude of the resonant current is insufficient, the input capacitor voltage cannot reach DC input voltage before the high-side MOSFET is turned on and switching loss occurs (i.e. ZVS is not achieved).

For traditional resonant converters, the deadtime period is small compared to the switching period due to the large resonant current circulating. For these converters, one may assume that the resonant current is constant during deadtime, simplifying analysis [12]. However, for a PT-based converter, this assumption is not valid because the large input capacitance ( $C_{\rm in}$  shown in Fig. 1 requires considerable charging time (typically around a quarter of the switching cycle) meaning one must consider the variation of the resonant current over this quarter cycle. Early implementations [2] of PT-based power supplies used magnetic inductors to simplify soft switching. The inductorless design used in this paper avoid this additional bulky component.

Several authors have developed analytical models to estimate circuit behaviour and ZVS ability in order to maximise the efficiency of a PT-based converter under different operating conditions. In [7], the ZVS characteristics of an inductorless PT-based converter are presented. However, [7] presents an overly conservative estimation of ZVS ability, due to the switching waveform shape assumption of the PT input capacitor voltage (i.e. square wave) and the resonant current phase shift. In addition, its application is limited since only the deadtime period is varied as a control parameter whereas ZVS is also dependent on switching frequency and load.

In [13], the ZVS ability is represented as a function of the input-to-output capacitance ratio and derived using a parametric sweep of the equivalent circuit parameters. Although good agreement between simulation and calculation is indicated by this approach, the ZVS predictions are less accurate as the parameter sweep is dependent on a curve-fit obtained from a specific PT characterisation. In [14], a state-variable model is employed to describe the circuit operating conditions of a PT-based inverter. A fundamental-mode approximation (FMA) is used to describe the nonlinear behaviour of the bridge rectifier and load. A numerical method is then employed to indicate the ZVS region as a function of

All authors are with The University of Sheffield, Department of Electronic and Electrical Engineering, Sir Frederick Mappin Building, Mappin Street, SHEFFIELD, S1 3JD. UK.

Zijiang Yang: zijiang.yang@sheffield.ac.uk

Martin Foster: m.p.foster@sheffield.ac.uk

David Stone: d.a.stone@sheffield.ac.uk

Jack Forrester: jack.forrester@sheffield.ac.uk

David Stone: d.a.stone@sheffield.ac.uk

This work was supported by the Engineering and Physical Sciences Research Council (EP/S031421/1). For the purpose of open access, the authors have applied a creative commons attribution (CC BY) licence to any author accepted manuscript version arising.

duty cycle and switching frequency. Although these methods are presented with improved accuracy, they are difficult to implement in practice due to the lack of both normalised parameter analysis and design example.

In [15], a piecewise linear state-variable model is presented with improved accuracy for predicting ZVS. The ZVS ability of an inductorless PT-based inverter is assessed using cyclic-mode analysis. The ZVS profile is generated as a function of deadtime, switching frequency and load. ZVS boundary has been highlighted for different PTs and the appropriateness of PTs for different applications are assessed.

In [11], an analytical model of the inductorless half-bridge driven PT is derived using a describing function approach. A critical design criterion is derived to guarantee ZVS is achieved and the difficulty associated with multiple parameter control for ZVS operation is highlighted.

However, all of the methods previously described exhibits one or more of following problems: —

- 1) They do not adequately describe how to obtain continuously achievable ZVS, especially when the ZVS region is disconnected at the matched load condition (the worst-case scenario for achieving ZVS).

- They lack a design example and practical implementation requires complex control circuitry for simultaneous parameter control [16] (e.g. switching frequency and deadtime).

Several methods are proposed in literature to regulate the output voltage of a PT-based converter. In [17], a hybrid half-bridge H-bridge converter is employed and output voltage regulation is achieved by separately controlling the on-period for each switch. Energy and charge conservation are used to calculate the state variables and the ZVS boundary is found as a function of voltage gain. A simulated efficiency of 93.6% is achieved with 10W output power at 500V input and 120V output.

To ensure an adjustable voltage gain, a tuneable radial-mode PT (an additional piezoelectric section is added between primary and secondary) with an external control capacitance is presented in [8] and [18], with duty-cycle control used to compensate for input voltage and load variations. The output is regulated at 55V with 220V input and 45% load variation in [8], and 41.5V with 250V input and 30% load variation in [18].

To improve the voltage regulation ability, compensation networks are employed in [19]. A comprehensive analysis of the impacts of the compensation networks on the characteristics of the PT is provided. Several input and output matching networks are employed via different combinations. The voltage gain can be tuned during the design phase by changing the compensation networks. General guidelines for the selection of matching networks are provided for a given PT with output voltage regulation requirements.

These three methods, however, experience one or more of the following drawbacks: —

No analytical model is employed to estimate the circuit behaviour and therefore ZVS cannot be guaranteed during the output regulation process.

- 2) The output regulation ability is limited since the ZVS region as a function of any particular circuit parameter is unclear, especially when the ZVS region is discontinuous.

- 3) Although employing a series inductor would enlarge the ZVS operating region, it reduces the output regulation ability of the converter [19].

In this paper, a novel inductorless H-bridge-driven PT-based power supply is proposed that can simultaneously achieve ZVS and output regulation through the introduction of a zero-voltage level during the deadtime interval. A piecewise linear state-variable model is presented, which provides predictions of switching waveforms from which cyclic mode analysis is used to provide the ZVS profile, ZVS boundary and output voltage characteristics. Output regulation with continuously achievable ZVS is obtained by controlling the duration of the zero-voltage level during the deadtime interval via a H-bridge topology.

The contribution of the proposed work includes: —

- 1) Achieving voltage regulation.

- 2) Achieving ZVS in the PT input capacitance and with all MOSFET capacitances.

- Cyclic mode analysis to estimate circuit behaviour, ZVS and voltage regulation characteristics.

- 4) Control of an H-bridge to achieve the above objectives.

This article is organized as follows: The basic operation of the PT-based inductorless H-bridge inverter is given in section II. Section III describes the piecewise linear state-variable model with the corresponding operating modes and the deadtime interval requirement for each mode. The cyclic modelling analysis and state-variable solution for ZVS and output voltage is given in section IV. Experimental results are demonstrated in section V. Section VI illustrates the ZVS and output voltage characteristics at different circuit conditions. Section VII demonstrates simultaneous voltage regulation and ZVS performance for a given PT. Practical design consideration regarding PT design, ZVS and voltage regulation are demonstrated in section VIII.

# II. Operation of Inductorless H-bridge PT-based Resonant Inverter

#### A. Operating principle

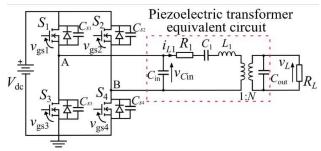

When a PT operates near resonance, it generally exhibits a high quality factor (Q) and its electrical behaviour can be modelled by the Mason equivalent circuit shown within the dashed box in Fig. 1. The input capacitor  $(C_{\text{in}})$  and output capacitor  $(C_{\text{out}})$  represent the capacitances created between the electrodes of the PT. Components  $C_1$ ,  $L_1$ , and N model the mechanical resonant behaviour, and  $R_1$  corresponds to the loss (or damping) in the PT. Sufficient dead-time intervals are applied between the gate signals of the MOSFETs to prevent shoot-through and to achieve ZVS by allowing time for the resonant current  $i_{L1}$  to charge  $C_{\text{in}}$  from  $-V_{\text{dc}}$  to  $+V_{\text{dc}}$  (and vice versa).

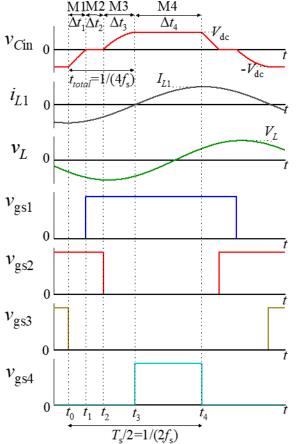

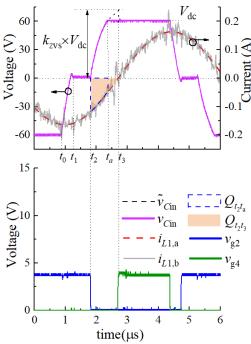

Fig. 2 shows the steady-state switching waveforms for the inverter shown in Fig. 1 under ZVS condition, where  $v_{Cin}$ ,  $i_{L1}$  and  $v_L$  are the PT input capacitor voltage, resonant current and

Fig. 1. Inductorless driven PT-based H-bridge inverter.

Fig. 2. Switching waveforms of the inductorless driven PT-based H-bridge inverter.

output (load) voltage, respectively. The resonant current is assumed to be sinusoidal due to the high Q-factor of the PT and its peak value is shown as  $I_{L1}$ .  $f_s$  is the switching frequency. Output voltage regulation is afforded by adjusting the duration of the zero-voltage interval labelled as  $\Delta t_2$  in Fig. 2.

For the purpose of simplifying the analysis for ZVS operation it is assumed that the circuit exactly achieves ZVS and so can be described entirely by the mode sequence  $M1\rightarrow M2\rightarrow M3\rightarrow M4$  due to the half-cycle symmetry exhibited by the circuit operation. The first mode (M1) starts at time  $t=t_0$  and the transition from mode i to mode i+1 occurs at time  $t_i$ . The transition times are labelled above the  $v_{\text{Cin}}$  waveform in Fig. 2. The mode time durations,  $\Delta t_1$ ,  $\Delta t_2$ ,  $\Delta t_3$  and  $\Delta t_4$  (where  $\Delta t_i = t_i - t_{i-1}$ ) refer to the deadtime during M1; the conduction time

of  $S_1$  &  $S_2$  during M2 when  $v_{\text{Cin}}$ =0; the deadtime during M3; and the conduction time of  $S_1$  &  $S_4$  during M4 to maintain  $V_{\text{dc}}$  (or  $S_2$  &  $S_3$  conduction period in M4 to maintain  $-V_{\text{dc}}$  for the second half-cycle), respectively.  $t_{total}$  is the total deadtime period (i.e.  $t_{\text{total}} = \Delta t_1 + \Delta t_2 + \Delta t_3$ ). As can be seen, ZVS is achievable if  $v_{\text{Cin}}(t_3) \ge V_{\text{dc}}$ .

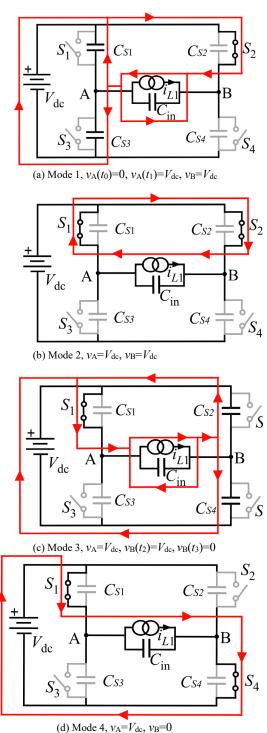

During a half-cycle period, the inverter exhibits one of the following four modes of operation, depending on the control of the switches.

M1:  $t \in [t_0, t_1]$ : Prior to time  $t_0$ , MOSFETs  $S_2$  and  $S_3$  are on so  $v_{Cin}(t_0) = -V_{dc}$ . At  $t = t_0$ , only  $S_2$  is turned on and so the resonant current,  $i_{L1}$ , circulates through  $C_{in}$ , thus  $v_{Cin}$  is being charged from  $-V_{dc}$  towards 0V.

M2:  $t \in [t_1, t_2]$ : At  $t=t_1$ ,  $S_1$  and  $S_2$  are turned on to set  $v_{Cin}=0$  and so  $i_{L1}$  flows through both  $S_1$  and  $S_2$ .

M3:  $t \in [t_2, t_3]$ : At  $t=t_2$ , only  $S_1$  is turned on and  $i_{L1}$  once again circulates through  $C_{in}$  charging it in a positive direction towards  $V_{dc}$ .

M4:  $t \in [t_3, t_4]$ : At  $t=t_3$ ,  $v_{Cin}(t_3) = V_{dc}$ .  $S_1$  and  $S_4$  are turned on thereby achieving zero-voltage switching (ZVS). Zero voltage derivative switching (ZVDS) can be achieved if  $v_{Cin}$  hits  $V_{dc}$  at the start of this mode thus  $dv_{Cin}/dt|_{t=t_3} \propto i_{L1}(t_3) = 0$ .

To ensure ZVS operation for an inductorless PT-based configuration, the critical criterion described in [11] is adapted. ZVS can be achieved for all load conditions if the input-to-output capacitance ratio meets  $C_{\rm in}/(N^2\,C_{\rm out}) \leq 2/\pi$  with  $\pi/2$  total deadtime  $t_{\rm total}$ . When the ZVS criterion is met, the resonant current  $i_{L1}$  must be in-phase with the gate signals, and thereby guaranteeing the total deadtime  $t_{\rm total}$  begins at the negative peak of  $i_{L1}$  since this is where the quickest charging of  $C_{\rm in}$  happens. This ensures the PT input voltage  $v_{C\rm in}$  is maximized by the end of the deadtime period. In this work, the output voltage is regulated by controlling  $\Delta t_2$ , and  $\Delta t_3$  is controlled to ensure the total deadtime  $t_{total} = \Delta t_1 + \Delta t_2 + \Delta t_3 = 1/(4f_s)$ .

For the load conditions, the matched load corresponds to the highest efficiency point since it provides lowest resonant current. Therefore, a longer charging time is required for  $C_{\rm in}$  during the deadtime. If ZVS is achievable at the matched load condition, ZVS can be achieved for all load conditions. The matched load is defined as

$$R_L = \frac{1}{2\pi f_0 C_{\text{out}}} \tag{1}$$

where  $f_0 = 1/(2\pi\sqrt{L_1C_1})$ .

It should be noted that, although ZVS is achievable for  $C_{in}$ , ZVS also needs to be achieved for MOSFETs capacitance [21]. As can be seen from Fig. 3, the PT's resonant tank  $(L_1, C_1, R_1)$  can be modelled by a sinusoidal resonant current  $i_{L1}$ . During the total deadtime period  $t_{total}$ , the resonant current circulates in the resonant tank and charges the MOSFET capacitors and the PT input capacitance. The voltage across  $C_{in}$  is in the range  $-V_{dc}$  to

Fig. 3. Proposed control sequence for the inductorless H-bridge PT-based inverter with equivalent circuit model. ( $\nu_A$  and  $\nu_B$  refer to the voltage on node A and B)

$V_{\rm dc}$  and, while it is charging, the voltage at the midpoint of each bridge is also increasing. At the start of M1,  $t_0$ , the left bridge  $v_A$  (i.e.  $C_{S1}$  and  $C_{S3}$ ) is at 0 and the right bridge  $v_B$  (i.e.  $C_{S3}$  and  $C_{S4}$ ) is at  $V_{\rm dc}$ . At the end of M3,  $t_3$ , the left bridge  $v_A$  is at  $V_{\rm dc}$  while right bridge  $v_B$  is at 0. When  $C_{\rm in}$  is at 0 during M2, the voltage across the left bridge is equivalent to the right bridge. Therefore, if  $v_A = v_B$  (while  $v_A \neq 0$ ), turning on two MOSFETs results in losses due to MOSFET output capacitor discharge. If  $v_A \neq v_B$ , losses always occurs when two MOSFETs turned on since  $v_A \neq 0$ , or  $v_B \neq 0$  or both.

A new control (switching sequence) is implemented in this work (as shown in Fig. 3), such that the right hand bridge leg is turned off and output voltage of the right hand bridge is allowed to discharge from  $V_{\rm dc}$  to 0 using the resonant current. Then the high-side MOSFET are turned on to obtain the 0V period (i.e. M2). The left-hand bridge leg is operated in a similar manner where it is turned off and its output voltage is charged to  $V_{\rm dc}$ . Therefore, the switching loss can be eliminated in the MOSFETs.

#### B. Controller description

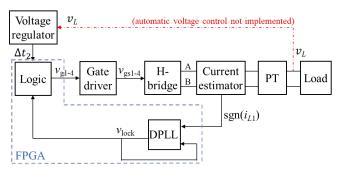

Fig. 4. Block diagram of the controller for a PT-based inverter.

TABLE I STATE MACHINE OF THE CONTROLLER

| Mode            | Gate signals |             |              |             | Condition for mode to                      |  |

|-----------------|--------------|-------------|--------------|-------------|--------------------------------------------|--|

| (state)         | $v_{ m gl}$  | $v_{ m g2}$ | $v_{\rm g3}$ | $v_{ m g4}$ | begin                                      |  |

| $M1^+$          | 0            | 1           | 0            | 0           | $\pi/2$ after M4 $^-$                      |  |

| M2 <sup>+</sup> | 1            | 1           | 0            | 0           | $v_{c_{\rm in}} = 0$                       |  |

| M3 <sup>+</sup> | 1            | 0           | 0            | 0           | $\Delta t_2$ after M2 $^+$                 |  |

| $M4^{+}$        | 1            | 0           | 0            | 1           | $v_{lock}: 0 \rightarrow 1$                |  |

| M1 <sup>-</sup> | 1            | 0           | 0            | 0           | $\pi/2$ after M4 $^{\scriptscriptstyle +}$ |  |

| M2 <sup>-</sup> | 1            | 1           | 0            | 0           | $v_{c_{\rm in}} = 0$                       |  |

| M3 <sup>-</sup> | 0            | 1           | 0            | 0           | $\Delta t_2$ after M2 <sup>-</sup>         |  |

| $M4^-$          | 0            | 1           | 1            | 0           | $v_{\text{lock}}: 1 \rightarrow 0$         |  |

+ and - represent the positive and negative half cycles

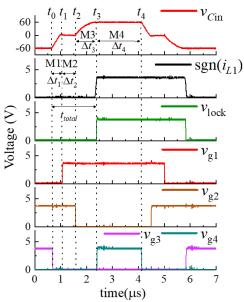

The block diagram of the proposed controller for H-bridge PT-based inverter is shown in Fig. 4. The control is performed dynamically by mix of digital and analogue techniques. The digital part is implemented by a field-programmable gate array (FPGA) together with a digital phase-locked loop (DPLL). The analogue part includes a current estimator.

Since the resonant current is internal to the PT and cannot be measured directly, we draw on our previous work where we developed a resonant current estimation circuit (using voltage sensing) [10]. As shown in Fig. 4, the resonant current is estimated and its direction  $sgn(i_{L1})$  is given as an input to the

DPLL which ensures synchronisation of the gate signals to the resonant current. The DPLL output,  $v_{lock}$ , is used to indicate a DPLL locked condition. Therefore,  $sgn(i_{L1})$  and  $v_{lock}$  are phase-and frequency-matched when the DPLL is locked on.

Programmable logic is used to generate the in-phase gate reference signals  $v_{g1}$  to  $v_{g4}$ . The logic implements a finite-state machine where the modes are the machine's states, as shown in Table I.

The modes progress in a single order from M1<sup>+</sup> to M4<sup>+</sup>, then M1<sup>-</sup> to M4<sup>-</sup> and then restart at M1<sup>+</sup>; the conditions for transition between modes are also shown. Under normal conditions,  $v_{lock}$  is in phase with  $sgn(i_{L1})$ . In our implementation,  $v_{Cin}$  is not measured, but the period of M1 ( $\Delta t_1$ ) is calculated by solving (28).

Energy is input to the converter during M4 which lasts for half of each half cycle and begins when the current changes sign. M1, M2 and M3 are the deadtime. The period of M2,  $\Delta t_2$ , is controlled by the voltage regulator and holds  $v_{Cin}$  at zero during M2, reducing average power output to the load.

# III. State-Variable Model Analysis

Since the operation of the circuit is divided into four modes (see the input capacitor voltage  $v_{Cin}$  in Fig. 2), then four piecewise state-variable models are required to describe the evolution of the state trajectories during a half-cycle period. Below, we use the technique described in [15] which models the cyclic behaviour of a converter using piecewise linear state-variable models. If the mode times are known, then the technique in [15] allows the cyclic mode initial condition  $x(t_0)$  to be determined and using (30).

In this section, a non-linear state-variable model is derived from the differential equations for the inductor current and capacitor voltages. This model is then decomposed into a piecewise linear model based on the operating modes previously described.

#### A. Stage I – Model Derivation

The inductor current is found from

$$\dot{l_{L1}} = \frac{v_{L1}}{L_1} = \frac{v_{Cin} - i_{L1}R_1 - v_{C1}}{L_1} - \frac{v_L}{NL_1}$$

(2)

The primary side capacitor voltage during M1-M4 is given by

$$v_{C1}^{\cdot} = \frac{i_{L1}}{C_{1}}$$

$$v_{Cin}^{\cdot} = \begin{cases} -\frac{i_{L1}}{C_{in}} & t_{0} \leq t < t_{1} \\ 0 & t_{1} \leq t < t_{2} \\ -\frac{i_{L1}}{C_{in}} & t_{2} \leq t < t_{3} \\ 0 & t_{3} \leq t < t_{4} \end{cases}$$

$$(3)$$

With the initial conditions:  $v_{Cin}(t_0) = -V_{dc}$ ,  $v_{Cin}(t_1) = 0$ ,  $v_{Cin}(t_2) = 0$ ,  $v_{Cin}(t_3) = V_{dc}$  and it is assumed that the circuit is

operated in an appropriate manner to guarantee these conditions can be achieved.

The output voltage  $v_L$  is given by

$$v_L^{\cdot} = v_{\text{Cout}}^{\cdot} = \frac{i_{L1}}{NC_{\text{out}}} - \frac{v_L}{R_L C_{\text{out}}}$$

(5)

Combining (2)-(5) provides the complete state-variable model and coupling equations

$$\begin{bmatrix} i_{L1} \\ v_{C1} \\ v_{Cin} \\ v_{L} \end{bmatrix} = \begin{bmatrix} -\frac{R_1}{L_1} & -\frac{1}{L_1} & \frac{R_2(t)}{L_1} & -\frac{1}{NL_1} \\ \frac{1}{C_1} & 0 & 0 & 0 \\ -\frac{h_2(t)}{C_{in}} & 0 & 0 & 0 \\ \frac{1}{NC_{out}} & 0 & 0 & -\frac{1}{R_LC_{out}} \end{bmatrix} \begin{bmatrix} i_{L1} \\ v_{C1} \\ v_{Cin} \\ v_{L} \end{bmatrix}$$

$$+ \begin{bmatrix} h_1(t) \frac{V_{dc}}{L_1} \\ 0 \\ 0 \end{bmatrix}$$

$$(6)$$

where  $h_1(t)$  and  $h_2(t)$  are switching functions defined as

$$h_{1}(t) = \begin{cases} 0 & t_{0} \leq t < t_{3} \\ 1 & t_{3} \leq t < t_{4} \end{cases}$$

$$h_{2}(t) = \begin{cases} 1 & t_{0} \leq t < t_{1} \\ 0 & t_{1} \leq t < t_{2} \\ 1 & t_{2} \leq t < t_{3} \\ 0 & t_{3} \leq t < t_{4} \end{cases}$$

$$(7)$$

# B. Stage II – Decomposition into piecewise linear models

The state-variable model can be obtained from equation (6) and (7). For M1, it is given by (8).

$$\dot{\mathbf{x}} = \mathbf{A}_1 \mathbf{x} + \mathbf{B}_1$$

where  $\mathbf{A}_1$  and  $\mathbf{B}_1$  are defined as

$$\mathbf{x} = \begin{bmatrix} i_{L1} \\ v_{C1} \\ v_{Cin} \\ v_L \end{bmatrix},$$

$$\mathbf{A}_1 = \begin{bmatrix} -\frac{R_1}{L_1} & -\frac{1}{L_1} & \frac{1}{L_1} & -\frac{1}{NL_1} \\ \frac{1}{C_1} & 0 & 0 & 0 \\ -\frac{1}{C_{in}} & 0 & 0 & 0 \\ \frac{1}{NC_{out}} & 0 & 0 & -\frac{1}{R_L C_{out}} \end{bmatrix}, \mathbf{B}_1 = \begin{bmatrix} 0 \\ 0 \\ 0 \\ 0 \end{bmatrix}$$

(9)

In M2,  $v_{Cin}$  is maintained at zero, thus  $v_{Cin} = 0$ . Hence, M2 can be described as

$$\mathbf{A}_{2} = \begin{bmatrix} \frac{\dot{\mathbf{x}} = \mathbf{A}_{2}\mathbf{x} + \mathbf{B}_{2}}{-\frac{L_{1}}{L_{1}}} & -\frac{1}{L_{1}} & 0 & -\frac{1}{NL_{1}} \\ \frac{1}{C_{1}} & 0 & 0 & 0 \\ \frac{0}{1} & 0 & 0 & 0 & 0 \\ \frac{1}{NC_{\text{out}}} & 0 & 0 & -\frac{1}{R_{L}C_{\text{out}}} \end{bmatrix}, \mathbf{B}_{2} = \begin{bmatrix} 0 \\ 0 \\ 0 \\ 0 \end{bmatrix}$$

(11)

Due to symmetric behaviour of the system, the model matrices for M3 are equivalent to M1, i.e.  $A_3=A_1$ ,  $B_3=B_1$ .

For M4,  $v_{Cin}$  is maintained at  $V_{dc}$ , hence  $v_{Cin} = 0$ . M4 is defined as

$$\mathbf{A_4} = \begin{bmatrix}

-\frac{R_1}{L_1} & -\frac{1}{L_1} & 0 & -\frac{1}{NL_1} \\

\frac{1}{C_1} & 0 & 0 & 0 \\

0 & 0 & 0 & 0 \\

\frac{1}{NC_{\text{out}}} & 0 & 0 & -\frac{1}{R_L C_{\text{out}}}

\end{bmatrix}, \mathbf{B_4} = \begin{bmatrix}

\frac{V_{\text{dc}}}{L_1} \\

0 \\ 0 \\

0

\end{bmatrix}$$

(12)

Finally, from the state-variable descriptions of each mode, and the time interval of each mode, the inverter operation in a cyclic mode can be determined.

#### IV. Modelling Cyclic Mode Behaviour

The proposed cyclic modelling is described as an extended Floquet-based method [22], by determining steady-state values of state-variables. It is an alternative to integration-based [11] methods and the state-space averaging technique [23] often used to model the periodically switching networks.

During a half cycle, the circuit operation is decomposed into four operating modes (M1 $\rightarrow$  M4, from  $t=t_0$  to  $t=t_4$ ), depending on the switch state, as shown by the waveforms given in Fig. 4. Therefore, the system in each mode can be described by the piecewise linear equation

$$\dot{\boldsymbol{x}}(t) = \boldsymbol{A}_i \boldsymbol{x}(t) + \boldsymbol{B}_i \tag{14}$$

where x(t) is the state vector, i is the mode index,  $A_i$  and  $B_i$  are the dynamical matrix and the input vector, respectively. Therefore, for  $t_{i-1} \le t \le t_i$ , the evolution of the state vector is given as

$$x(t) = \exp(A_i(t - t_{i-1}))x(t_{i-1}) + \int_{t_{i-1}}^{t} \exp(A_i(t - \tau))B_i d\tau$$

(15)

Assuming the input voltage is constant for the duration of a mode, the state vector  $\mathbf{x}(t)$  at  $t=t_i$  can be solved from the state vector value at  $t_{i-1}$  using,

$$x(t_{i}) = \exp(\boldsymbol{A}_{i}(t_{i} - t_{i-1}))\boldsymbol{x}(t_{i-1})$$

$$+ \int_{t_{i-1}}^{t_{i}} \exp(\boldsymbol{A}_{i}(t_{i} - \tau))\boldsymbol{B}_{i}d\tau$$

$$= \exp(\boldsymbol{A}_{i}d_{i}T_{s})\boldsymbol{x}(\boldsymbol{t}_{i-1}) + \boldsymbol{A}_{i}^{-1}(\exp(\boldsymbol{A}_{i}d_{i}T_{s})$$

$$- \boldsymbol{I})\boldsymbol{B}_{i}$$

$$= \Phi_{i}\boldsymbol{x}(\boldsymbol{t}_{i-1}) + \Gamma_{i}$$

$$(16)$$

where I is the identity matrix,  $\Phi_i = \Phi(t_i, t_{i-1}) = \exp(A_i d_i T_s)$ ,  $\Gamma_i = A_i^{-1} (\exp(A_i d_i T_s) - I) B_i$  and  $d_i$  is the duty cycle for the i<sup>th</sup> mode:  $d_i T_s = t_i - t_{i-1}$

Therefore, the complete cyclic-mode of the system can be determined from (16) once the initial circuit condition  $x(t_0)$  has been found, which has the form

$$\mathbf{x}(t_0) = [i_{L1}(t_0) \quad v_{C1}(t_0) \quad v_{Cin}(t_0) \quad v_L(t_0)]^{\mathrm{T}}$$

(17)

The values of the state-variables at the end of M1 are found from

$$\mathbf{x}(t_1) = \Phi_1 \mathbf{x}(t_0) + \mathbf{\Gamma}_1 \tag{18}$$

Similarly, at the end of mode 2, the state is given by

$$\mathbf{x}(t_2) = \Phi_2 \mathbf{x}(t_1^+) + \mathbf{\Gamma}_2 \tag{19}$$

where  $x(t_1^+)$  is the value of x immediately after the possible discontinuity in the state-variables at  $t=t_2$  caused by the turning-on of  $S_3 \& S_4$  to clamp  $v_{Cin}$  at 0,

$$\mathbf{x}(t_1^+) = [i_{L_1}(t_1) \quad v_{C_1}(t_1) \quad 0 \quad v_L(t_1)]^{\mathrm{T}}$$

(20)

From (19) and (20), a new matrix K can be introduced to reset the existing  $v_{Cin}$  to 0 at each switching instant. Where  $v_{Cin}$  takes a new value, an additional vector  $x_i$ , representing the discontinuity in  $v_{Cin}$  due to MOSFETs switching, sets the new value of  $v_{Cin}$ . Therefore, (16) can be modified as

discontinuity in

$$v_{Cin}$$

due to MOSFE1s switching, sets the new value of  $v_{Cin}$ . Therefore, (16) can be modified as

$$\mathbf{x}(t_i) = \Phi_i[\mathbf{K}\mathbf{x}(t_{i-1}) + \mathbf{x}_i] + \mathbf{\Gamma}_i \qquad (21)$$

where  $\mathbf{K} = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix}, \quad \mathbf{x}_1 = \mathbf{x}_2 = \mathbf{x}_3 = \begin{bmatrix} 0 \\ 0 \\ 0 \\ 0 \end{bmatrix}, \quad (22)$

$$\mathbf{x}_4 = \begin{bmatrix} 0 \\ 0 \\ V_{dc} \\ 0 \end{bmatrix}$$

These equations can be expanded to give the solutions of the state vector for M2, M3 and M4

$$\mathbf{x}(t_2) = \Phi_2 \mathbf{K} \Phi_1 \mathbf{x}(t_0) + \Phi_2 \mathbf{K} \mathbf{\Gamma}_1 + \mathbf{\Gamma}_2 \tag{23}$$

$$\mathbf{x}(t_3) = \Phi_3 \mathbf{K} \Phi_2 \mathbf{K} \Phi_1 \mathbf{x}(t_0) + \Phi_3 \mathbf{K} \Phi_2 \mathbf{K} \Gamma_1$$

$$+ \Phi_2 \mathbf{K} \Gamma_2 + \Gamma_2$$

(24)

$$\mathbf{x}(t_4) = \Phi_4 \mathbf{K} \Phi_3 \mathbf{K} \Phi_2 \mathbf{K} \Phi_1 \mathbf{x}(t_0) + \Phi_4 \mathbf{K} \Phi_3 \mathbf{K} \Phi_2 \mathbf{K} \Gamma_1 + \Phi_4 \mathbf{K} \Phi_3 \mathbf{K} \Gamma_2$$

(25)

$$+\Phi_4K\Gamma_3+\Phi_4x_4+\Gamma_4$$

By using the odd-symmetry behaviour of the inverter during a half-cycle  $x(t_4) = -x(t_0)$ , the initial condition of the cyclic mode  $x(t_0)$  can be given by

$$\mathbf{x}(t_0) \qquad (26)$$

$$= [-\mathbf{I} - \Phi_4 \mathbf{K} \Phi_3 \mathbf{K} \Phi_2 \mathbf{K} \Phi_1]^{-1} [\Phi_4 \mathbf{K} \Phi_3 \mathbf{K} \Phi_2 \mathbf{K} \Gamma_1 + \Phi_4 \mathbf{K} \Phi_3 \mathbf{K} \Gamma_2 + \Phi_4 \mathbf{K} \Gamma_3 + \Phi_4 \mathbf{x}_4 + \Gamma_4]$$

The value of the PTs input capacitor voltage  $v_{Cin}$  at  $t=t_3$  in M3 can be found by substituting equation (23) into equation (24) to give

$$v_{Cin}(t_3) = [0 \ 0 \ 1 \ 0][\Phi_3 K \Phi_2 K \Phi_1 x(t_0) + \Phi_3 K \Phi_2 K \Gamma_1 + \Phi_3 K \Gamma_2 + \Gamma_3]$$

(27)

The deadtime value  $\Delta t_1 = t_1 - t_0$  can be found from M1 in (18) when  $v_{Cin}$  is charged from  $-V_{dc}$  to 0, which is given by

$$v_{\text{Cin}}(t_1) = 0 = [0 \ 0 \ 1 \ 0][\Phi_1 \mathbf{x}(t_0) + \Gamma_1]$$

(28)

The output voltage  $v_L$  is found from

$$v_L(t) = [0 \ 0 \ 0 \ 1] \mathbf{x}(t) \tag{29}$$

Where x can be found, during the i<sup>th</sup> mode as

$$\mathbf{x}(t) = \exp(A_i(t - t_{i-1})) \mathbf{x}(t_{i-1}) + A_i^{-1} (\exp(A_i(t - t_{i-1})) - \mathbf{I}) \mathbf{B}_i$$

(30)

#### V. Model Verification

# A. Charge Equivalence for ZVS

For a given PT, ZVS performance can be evaluated by comparing the value of  $v_{Cin}(t_3)$  to  $V_{dc}$ . In general, ZVS is achieved if  $v_{Cin}$  is charged to (or above)  $V_{dc}$  during M3, that is  $v_{Cin}(t_3) \ge V_{dc}$ .

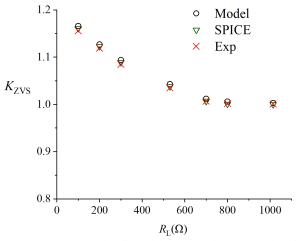

To evaluate the ZVS performance, we use a measure of the zero-voltage switching potential called  $K_{\rm ZVS}$ .  $K_{\rm ZVS}$  is the normalised input capacitor voltage at the point of switch turn-on that would result if the voltage were not clamped by the body diodes of the MOSFETs. In practice,  $v_{\rm Cin}$  is clamped and therefore we project the voltage by assuming that the same resonant current  $i_{L1}$  flows into an unclamped but otherwise identical circuit. This unclamped voltage is termed  $\tilde{v}_{\rm Cin}$  and defined with  $K_{\rm ZVS}$  as

$$\tilde{v}_{Cin} = \begin{cases} \frac{1}{C_{in}} \int_{t_2}^{t} i_{L1} dt, & t_2 \le t \le t_3 \\ \text{undefined,} & t_2 > t > t_3 \end{cases}$$

(31)

$$K_{\rm ZVS} = \frac{\tilde{v}_{\rm Cin}(t_3)}{V_{\rm dc}} \tag{32}$$

Fig. 5 shows the experimental waveform for  $v_{Cin}$  under the ZVS condition and illustrates the calculation method for  $K_{ZVS}$ .

A ring-dot radial-mode PT (shown in Fig. 7(b)) is used for validation. It has the measured equivalent circuit components values given in Table II. The resonant current  $i_{L1}$  is reconstructed experimentally using the current estimation method we developed in [10]. The reconstructed current,  $i_{L1,a}$ , is fitted to a sine wave,  $i_{L1,b}$ , whose amplitude and phase are used, together with  $C_{in}$ , to estimate  $K_{ZVS}$ .

| TABLE II      |        |       |      |                    |              |      |

|---------------|--------|-------|------|--------------------|--------------|------|

| PT parameters |        |       |      |                    |              |      |

| $C_1$         | $L_1$  | $R_1$ | Q    | $C_{\mathrm{out}}$ | $C_{\rm in}$ | N    |

| 77.8pF        | 17.2mH | 12.5Ω | 1190 | 1.14nF             | 0.43nF       | 0.94 |

The magenta trace in Fig. 5 is the measured input capacitor voltage,  $v_{Cin}$ . A black line presents the portion of  $\tilde{v}_{Cin}$  which extends above  $V_{dc}$ .  $v_{g2}$  and  $v_{g4}$  are the gate signals. The charge required to change  $v_{Cin}$  from 0 to  $V_{dc}$  and  $K_{ZVS}V_{dc}$  are given as  $Q_{t2ta}$  and  $Q_{t2t3}$ , shown as blue dashed box and orange region, respectively.

Fig. 5. Cyclic model and practical case of  $v_{Cin}$  under ZVS operation.

$Q_{12/3}$  can be found by integrating the resonant current during this deadtime period,

$$Q_{t2t3} = \int_{t2}^{t3} i_{L1} dt \tag{33}$$

Evaluating (31), (32) and (33) at  $t_3$  yields

$$K_{\text{ZVS}} = \frac{\frac{1}{C_{\text{in}}} \int_{t_2}^{t_3} i_{L1} dt}{V_{\text{dc}}} = \frac{Q_{t2t3}}{C_{\text{in}} V_{\text{dc}}}$$

(34)

This definition is valid both for zero-switching and non-zero-switching.

To validate the charge equivalence concept, Kzvs is evaluated by the cyclic model, SPICE simulation and practical measurements, respectively. For the cyclic model, the extrapolated final value  $\tilde{v}_{Cin}(t_3)$  is used to represent  $K_{ZVS}$  from (32). For the SPICE simulation, the PT is implemented as Mason equivalent circuit (as shown in Fig. 1), and the H-bridge operates with MOSFETs body diodes.  $K_{ZVS}$  in these cases is calculated by using (33) and (34). The gate signals are used to provide precise timing of  $t_2$  and  $t_3$  for integration limits.

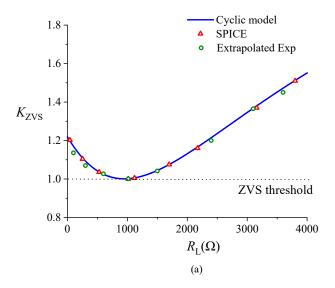

Fig. 6. K<sub>ZVS</sub> comparison of cyclic model, SPICE and experimental results.

Fig. 6 shows a comparison of  $K_{\rm ZVS}$  for the three methods. The cyclic model shows good agreement with the SPICE and experimental results, thereby providing evidence that the proposed cyclic mode is able to accurately predict ZVS ability of a PT-based inverter compared with practical case.

#### B. Experimental Result

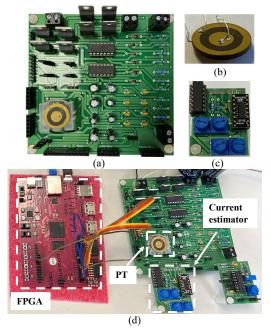

Fig. 7. (a) The prototype inductorless H-bridge PT-based inverter with (b) the ring-dot radial mode PT, (c) the resonant current estimation circuit and (d) the experimental platform.

Fig. 8. Experimental measurements of the proposed H-bridge inverter.

To verify the proposed cyclic modelling and to estimate the steady-state output voltage of a inverter, a prototype inverter based on the critical criterion [11] with a ring-dot radial-mode PT is employed, as shown in Fig. 7(a) and (b). A matched load (representing the worst case for achieving ZVS) of  $1k\Omega$  is used at the PT output. The current estimation technique developed in [10] was used (as shown in Fig. 7(c)) to estimate resonant current and indicate its direction  $sgn(i_{L1})$  for the FPGA control circuit (implemented by Xilinx Zyng-7000 PYNQ-Z1 as shown in Fig. 7(d)). The experimental setup is shown in Fig. 7(d) including the FPGA, the main board, the PT and the current estimation. The programmable logic generates the in-phase gate reference signals  $v_{g1}$  to  $v_{g4}$ . Fig. 8 shows the switching waveforms of the H-bridge inverter operating with the parameters listed in Table III. Signals  $sgn(i_{L1})$  and  $v_{lock}$  are the direction of the estimated resonant current and DPLL output signal, respectively. The duration of mode M1,  $\Delta t_1$ , where  $v_{Cin}$ increases from  $-V_{dc}$  to 0 in M1 can be found from (28) with initial condition of the cyclic mode  $x(t_0)$  from (26), while the duration of M3,  $\Delta t_3$ , can be found, for  $K_{\text{ZVS}} = 1$ , from (27) by setting  $v_{Cin}(t_3) = V_{dc}$ . Subsequently, the time interval for M2 can be evaluated accordingly since the total deadtime  $t_{\text{total}} =$  $1/4f_{\rm s}$  [11].

| CIRCUIT OPERATING CONDITIONS |             |              |              |              |       |                       |

|------------------------------|-------------|--------------|--------------|--------------|-------|-----------------------|

| $V_{ m dc}$                  | $f_{\rm s}$ | $\Delta t_1$ | $\Delta t_2$ | $\Delta t_3$ | $R_L$ | $v_{L, \mathrm{RMS}}$ |

| 60V                          | 145.3kHz    | 0.41µs       | 0.53µs       | 0.78µs       | 1kΩ   | 26.3V                 |

TARIFIII

As can be seen from Fig. 8, DPLL output signal  $v_{lock}$  is phase and frequency matched to the input signal  $sgn(i_{L1})$ , indicating a DPLL locked operating condition. The zero crossings of resonant current are clearly indicated by  $v_{zc,iL1}$ , and ZVS is achievable as  $v_{Cin}$  reaches  $V_{dc}$  during the deadtime, that is  $v_{Cin}(t_3) \ge V_{dc}$ . Zero voltage derivative switching (ZVDS) is also obtained since the estimated current  $i_{L1}(t_3) \propto dv_{Cin}/dt|_{t=t_2}$

0. This is to be expected since the radial-mode PT was design to meet the critical criterion described in [11].

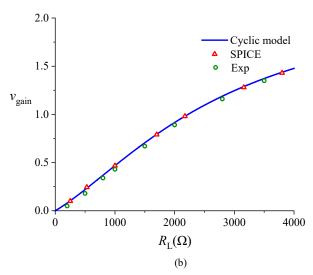

Fig. 9. Model validation: (a) ZVS and (b) voltage gain of the H-bridge inverter

In Fig. 9, the ZVS and output voltage are illustrated as a function of load resistor  $R_L$  with the same circuit conditions and time intervals as given in Table III. Equation (27) can be used to evaluate ZVS performance of a given PT, and this is demonstrated in Fig. 9(a), where the ZVS factor  $K_{ZVS}$  is compared with SPICE simulation and experimental results. Experimental measurements for  $K_{zvs}$  are given as extrapolated values of  $\tilde{v}_{cin}(t_3)$  calculated using equation (34). As can be seen from Fig. 9(a), the input capacitor voltage  $v_{Cin}$  is normalised and represented as  $K_{ZVS} = v_{Cin}(t_3)/(V_{dc})$ . It is shown that the proposed cyclic model correlates well with the SPICE and experimental results. For this particular PT, ZVS is clearly achievable for all load resistor values, while the worst case occurs at the matched load condition where  $K_{ZVS}=1$ , which corresponds to the  $v_{Cin}$  waveform shown in Fig. 8. The RMS value of output voltage  $v_{L,RMS}$  is normalised and given as the voltage gain  $v_{\text{gain}} = v_{L,\text{RMS}}/(NV_{\text{dc}})$ . As can be seen, the cyclic-mode model matches well with the simulation and experimental results.

#### VI. ZVS and Output Characteristics

# A. $\Delta t_1$ Sensitivity Analysis

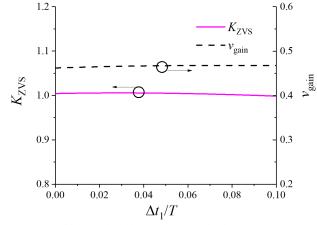

In general, the  $K_{\rm ZVS}$  can be assessed quantitatively with (27), and this is done by controlling  $\Delta t_2$ . Since the range of  $\Delta t_2$  variation is determined by  $\Delta t_1$ , the sensitivity of  $\Delta t_1$  in terms of key circuit parameters should be evaluated initially.

Fig. 10.  $\Delta t_1$  sensitivity analysis for ZVS factor and voltage gain.

In Fig. 10, the ZVS factor  $K_{\rm ZVS}$  and voltage gain  $v_{\rm gain}$  are plotted against  $\Delta t_1$  (deadtime in M1), and normalized to the switching period  $T_{\rm s}$  (i.e.  $1/f_{\rm s}$ ). The same circuit parameters are used as in previous section. As can be seen, both  $K_{\rm ZVS}$  and  $v_{\rm gain}$  exhibit negligible change with  $\Delta t_1$ . Therefore, it is indicated that sensitivity of  $K_{\rm ZVS}$  and  $v_{\rm gain}$  to  $\Delta t_1$  is low for modest changes in timing and the range of  $\Delta t_2$  variation is fixed.

# B. ZVS and Output Profile

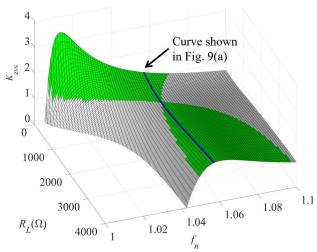

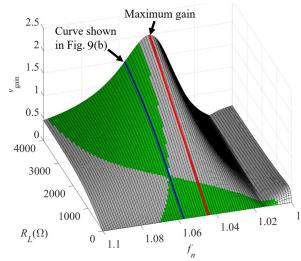

The 3D plot shown in Fig. 11 illustrates the  $K_{ZVS}$  dependence on both load  $R_L$  and normalised operating frequency  $(f_n = f_s / f_{0,n})$ where  $f_s$  and  $f_0$  are the switching frequency and resonant frequency) with the same fixed deadtime intervals employed to generate Fig. 8 (parameters are summarised in Table III). The  $K_{\rm ZVS}$  curve in Fig. 9(a) is also indicated by the blue line in Fig. 11 for the same parameter range. As can be seen, this ring-dot PT exhibits two distinct regions where ZVS is achievable for the inductorless H-bridge configuration as indicated by the shaded areas. These two regions are located at high and low loads respectively and are barely connected at the matched load. Careful design of the PT could ensure the ZVS region can be maintained without disconnection for large load variations, and it brings the opportunity for output regulation since it is possible to simultaneously control  $\Delta t_2$  (deadtime in M2), frequency and load to achieve ZVS continuously.

Fig. 11. ZVS characteristics for the radial-mode PT (shaded region is where  $K_{\text{ZVS}} \ge 1$ ).

Fig. 12. Contour plot of operating loci for the radial-model PT. (a) normalised frequency with load loci and (b) normalised frequency with time interval  $\Delta t_2$  loci.

Expanding on the ZVS characteristics shown in Fig. 11, Fig. 12 shows the relationship between (a) the load and normalized frequency and (b) the time interval  $\Delta t_2$  and normalised frequency for different  $K_{\rm ZVS}$  conditions. The contour of  $K_{\rm ZVS}$  =1 is equivalent to walking along the boundary of the shaded area in Fig. 11. The circuit operating condition listed in Table III is also indicated as a red circle in both Fig. 12 (a) and (b). In Fig.

12(a), ZVS is achievable at the matched load condition. To maintain ZVS, both switching frequency and  $\Delta t_2$  should be varied simultaneously and a maximum of 0.45 $\mu$ s variation for  $\Delta t_2$  is required (i.e.  $K_{\rm ZVS}$ =1), as shown in Fig. 12(b).

Fig. 13. Voltage gain profile of the radial-mode PT (shaded regions are where  $K_{\text{ZVS}} \ge 1$ ).

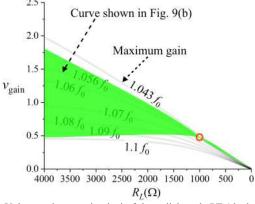

Fig. 13 shows the normalised output voltage gain characteristic with changes in both the operating frequency and the load for the same parameter range and circuit conditions with respect to Fig. 11. The voltage gain response corresponding to the conditions used to generate the Fig. 9(b) are indicated by the blue curve. As can be seen, the region of maximum achievable voltage gain is not completely covered by the ZVS region. The voltage gain increases with increasing load resistance, and for each load, the peak voltage gain occurs at  $f_n$ = 1.043 (shown as a red curve in Fig. 13). This can be further indicated in Fig. 14 (this is equivalent to the left-hand side view of Fig. 13), the matched load (red circle) and ZVS region (green area) are highlighted. As can be seen, 1.043f<sub>0</sub> clearly demonstrates the maximum gain condition among all the switching frequencies. This indeed indicates the optimal frequency for  $\Delta t_2$  variation in order to obtain the maximum voltage gain for regulation.

Fig. 14. Voltage gain operating loci of the radial-mode PT (shaded regions are where  $K_{ZVS} \ge 1$ ).

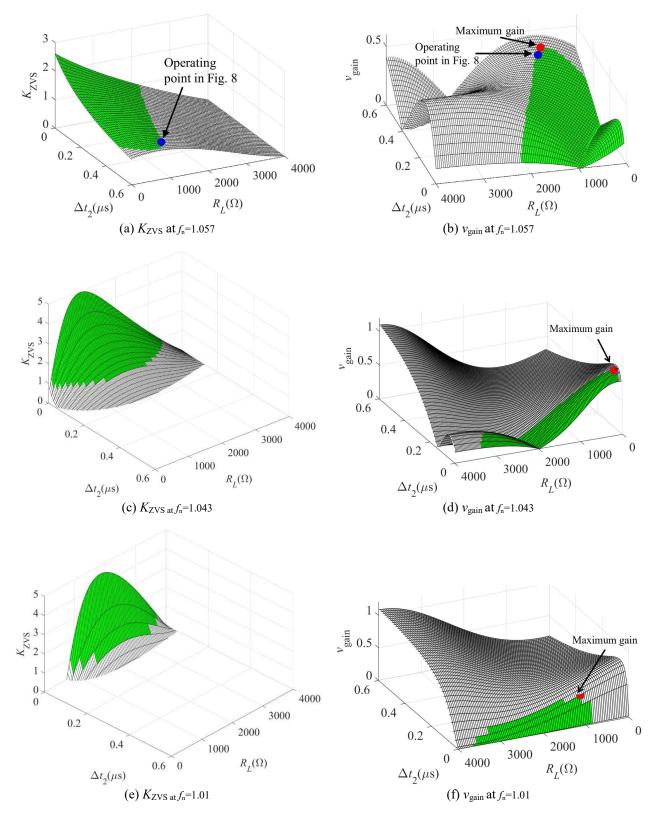

Fig. 15. ZVS profile and their corresponding normalised gain performance at (a)  $f_n$ =1.057, (b)  $f_n$ =1.043, (c)  $f_n$ =1.01(shaded region is where  $K_{ZVS} \ge 1$ ).

## VII. Simultaneous voltage regulation and ZVS

Although the highest efficiency can be achieved when the PT operates at the matched load condition, it is difficult to achieve ZVS for inductorless driven PTs under this condition in practice [24]. Moreover, it is difficult to regulate the output voltage while still achieving ZVS, since simultaneous parameter control should be employed and the ZVS region should be continuously connected during voltage regulation, as highlighted in [11][15][10]. Therefore, an analysis for achieving simultaneous ZVS and output voltage regulation is presented in this section based on the previous cyclic-mode analysis.

Fig. 15 highlights the  $K_{ZVS}$  and voltage-gain dependence on both the time interval  $\Delta t_2$  and the load for  $f_n=1.057$ ,  $f_n=1.043$ and  $f_n=1.01$ . To demonstrate the ZVS and output voltage regulation ability, the analysis is performed with the same PT as used in the section V. By way of example, the operating locus for the condition  $f_n=1.057$  is illustrated in Fig. 12. The duration required for  $\Delta t_1$  can be calculated from (28) as 0.41 µs, 0.406 µs and 0.4µs, for each frequency respectively. The blue dot shown in Fig. 15(a) is the operating point for Fig. 8 (as indicated in Table III) and the blue dot on Fig. 15(b) is the gain calculated using Table II and III. These points are located at the boundary of the ZVS region ( $K_{ZVS} = 1$  at the matched load). At the matched load condition, ZVS is no longer achievable when  $\Delta t_2$ increases. This is to be expected as interval  $\Delta t_3$  would be reduced accordingly to ensure total deadtime  $t_{\text{total}} = 1/(4f_s)$ based on the design criterion [11], and as a result the input capacitor voltage  $v_{Cin}$  cannot reach  $V_{dc}$  during the deadtime. For the  $f_n$ =1.057 case, although ZVS can be continuously obtained over a wide range of operating conditions (as shown in Fig. 15(b)), the normalised voltage gain under ZVS region is relatively low (i.e. 0.43 maximum).

To achieve the maximum voltage gain under ZVS, the  $f_n$ =1.043 case performs the best as shown in Fig. 15(d). Although the ZVS region is reduced at 1.043 $f_0$  compared with 1.057 $f_0$ , shown in Fig. 15(c), the corresponding voltage gain shown in Fig. 15(d) indicates a wide range of operation for output regulation with a maximum voltage gain of 0.9 at the 198  $\Omega$  load with 0.04  $\mu$ s  $\Delta t_2$ . By comparison, in Fig. 15(b) and Fig. 15(f), the maximum achievable voltage gains are reduced to 0.43 and 0.42, respectively.

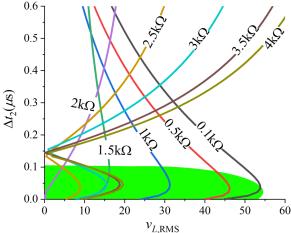

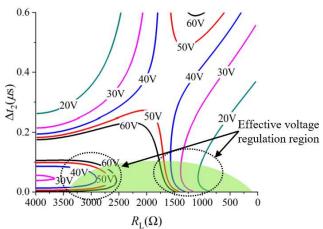

By way of example, Fig. 16 shows the practical load regulation performance of the proposed model at  $f_n$ =1.043 with 60V input voltage, ranging from 0.1 k $\Omega$  to 4 k $\Omega$ . As can be seen, by varying  $\Delta t_2$  with a maximum of around 0.1  $\mu$ s, the 4 k $\Omega$  case indicates the largest variation meanwhile still achieving ZVS. In addition, for this ring-dot radial mode PT, to ensure the voltage regulation is performed under ZVS, it is not recommended to operate at light load conditions since ZVS is no longer achieved. Fig. 17 shows the load regulation envelope at  $f_n$ =1.043 with input ranges from 20V-60V for the 5V output. The shaded green region is where ZVS is achieved. As can be seen, there are two distinctive regions (highlighted in dashed circle) where continuous voltage regulation can be achieved under ZVS. For example, to obtain a 5V output from a 60V

input, the load should vary from  $1.5k\Omega$  to  $1.8k\Omega$ , and from  $2.6k\Omega$  to  $3.3k\Omega$ , to maintain ZVS.

Fig. 16. Voltage regulation characteristics at  $1.043f_0$  under ZVS (shaded regions are where  $K_{ZVS} \ge 1$ ).

Fig. 17. Load regulation envelope at  $f_n$ =1.043 under ZVS for 5V output (shaded regions are where  $K_{\text{ZVS}} \ge 1$ ).

The circuit performance using the cyclic model is compared with previous art and given in Table IV. To ensure a fair comparison, a ring-dot radial mode PT with the same parameters listed in Table II is employed. The proposed model shows the best performance since circuit behaviour can be clearly estimated. In addition, by varying  $\Delta t_2$ , voltage regulation can be performed with continuously achievable ZVS. Moreover, the proposed switching sequence enables ZVS for both MOSFET capacitance and PT.

TABLE IV MODEL COMPARISON

| Ref  | ZVS region  | Output          | Simultaneous   | Regulation |        |

|------|-------------|-----------------|----------------|------------|--------|

|      |             | characteristics | ZVS & voltage  | ability    |        |

|      |             |                 | regulation     | Input      | Output |

| [11] | predictable | unpredictable   | not applicable | 20V        | 5V     |

| [15] | predictable | unpredictable   | not applicable | 20V        | 5V     |

| [21] | predictable | predictable     | not applicable | 30V        | 5V     |

| This | predictable | predictable     | applicable     | 15V-       | 5V     |

| work |             |                 |                | 60V        |        |

#### VIII. Practical design considerations and discussion

Although the cyclic model presented in this paper mainly focuses on resistive loads, other types of load and output configurations are also applicable. In general, maximum power can be delivered to the load when the voltage gain of a PT is maximised. From the circuit design perspective regarding an output rectifier, it has been reported that, for a given PT, the AC output configuration gives a larger maximum PT output power compared to the DC output configuration [25]. From a PT design perspective, since the optimum operating frequency is changed from achieving highest efficiency to obtaining maximum voltage gain, the PT is not necessarily designed to achieve ZVS at the matched load condition (see Fig. 13, the maximum voltage gain occurs at  $f_n=1.04$  while the lowest switching loss at matched load condition is at  $f_n$ =1.057). As a result, this would in turn reduce the PT dimension requirements (e.g. stacked disc-type Transoner PT), since the matched load indicates the highest efficiency point that requires smallest current (vibration velocity). If operating at matched load is no longer required, the critical criterion (i.e. the capacitor ratio,  $C_n$ ) can be relaxed. For example, for a ring-dot PT, this might translate to requiring less electrode area on the output section. Relaxing the criterion reduces the mechanical current and improves the voltage gain [24].

For practical circuit design, the thermal performance should be considered since the frequency response of a PT depends on its piezoelectric properties (e.g. dielectric, elastic and piezoelectric constants [26]), which are temperature dependent. Temperature variation can change the frequency response of a PT by shifting the resonant frequency and decreasing the voltage gain, thereby limiting the regulation ability. One possible solution is using a PLL-based controller since it operates irrespective of circuit conditions [10].

In terms of the PT design, the quality factor change should be considered since it can be significantly reduced when a PT operates at high power levels due to vibration velocity [27] and heating [28]. The reduction of quality factor is associated with an increase of the damping resistor  $R_1$ , which further decreases the voltage gain.

Therefore, to investigate the ZVS and output voltage performance of a PT-based inverter for a temperature-dependent parameter variation, extreme value analysis should be used, and both extreme (e.g. no load/full load condition, zero and maximum  $\Delta t_2$  time interval, extreme operating temperature) and expected circuit condition should be evaluated.

In general, with specified output voltage requirement, load and input range, the design process of achieving output voltage regulation under ZVS using the proposed model is summarised as follows: —

- 1) Generate  $K_{\text{ZVS}}$  and  $v_{\text{gain}}$  profiles using the cyclic model to find the optimum operating frequency which gives the maximum voltage gain.

- 2) After finding the optimum operating frequency, replot  $K_{\text{ZVS}}$  and  $v_{\text{gain}}$  with respect to the load and deadtime interval  $\Delta t_2$ .

- 3) Vary  $\Delta t_2$ , input voltage and load to see if this PT is able to meet voltage regulation requirement under ZVS using inductorless H-bridge configuration. If not, optimise the PT input-to-output capacitor ratio and repeat step 1, 2 and 3.

- 4) Build a prototype inverter and PT if both voltage regulation and ZVS can be achieved simultaneously.

To summarise, with the proposed switching sequence, ZVS can be obtained in both MOSFET capacitance and PT. By employing the proposed cyclic model, circuit behaviour can be estimated, the ZVS boundary and voltage gain as a function of circuit parameters (i.e. switching frequency and deadtime) are clearly demonstrated, and can be used to find the operating frequency for achieving maximum voltage gain. Subsequently, by controlling the time interval  $\Delta t_2$  and input voltage at the optimum frequency, the output voltage regulation can be realised with continuously achievable ZVS.

#### X. Conclusion

A methodology for estimating the ZVS and output voltage ability of an inductorless driven PT-based inverter is presented. A new control sequence is developed to ensure ZVS for both PT and MOSFET capacitance. A new concept for output voltage regulation by controlling deadtime interval is demonstrated. Through the application of cyclic-mode analysis, an analytical model of the PT under ZVS operation is derived. Measurements taken from a radial-mode PT is used to validate the proposed model. Subsequently, the model is employed to show the ZVS profile, ZVS boundary and the requirement for continuously achieving ZVS. By using an H-bridge configuration, the output can be controlled by varying the deadtime period. Furthermore, the optimum operating frequency for maximum voltage gain is demonstrated under continuous ZVS region. The output voltage characteristics of the radial-mode PT is generated at different frequencies, highlighting the importance of PT selection in order to obtain maximum achievable voltage gain meanwhile still achieving ZVS. Since the ZVS and output regulation ability is dependent on input capacitance, deadtime period, resonant current and operating frequency, the proposed model can be used to assess the appropriateness of the PT for a given application. Potential areas for the further development include developing a second control loop for the automatic voltage control.

#### REFERENCES

- [1] V. C. Alfredo, "50 years of piezoelectric transformers. Trends in the technology," in *Proc. Symp. D Mater. Devices Smart Syst.*, vol. 785, 2003, pp.33-44.

- [2] J. Díaz, F. Nuno, M. J. Prieto, J. A. Martín-Ramos, and P. J. Villegas Saiz, "Closing a second feedback loop in a DC-DC converter based on a piezoelectric transformer," *IEEE Trans. Power Electron.*, vol. 22, no. 6, pp. 2195-2201, 2007.

- [3] E. M. Baker, W. Huang, D. Y. Chen, and F. C. Lee, "Radial mode piezoelectric transformer design for fluorescent lamp ballast applications," *IEEE Trans. Power Electron.*, vol. 20, no. 5, pp. 1213-1220, 2005.

- [4] S. Ben-Yaakov and S. Lineykin, "Maximum power tracking of piezoelectric transformer HV converters under load variations," *IEEE Trans. Power Electron.*, vol. 21, no. 1, pp. 73-78, 2006.

- [5] E. L. Horsley, M. P. Foster and D. A. Stone, "State-of-the-art Piezoelectric Transformer technology," in *Proc. Eur. Conf. Power*

- Electron. Appl., Aalborg, Denmark, 2007.

- [6] M. S. Roedgaard, M. Weirich, and M. A. E. Andersen, "Forward conduction mode controlled piezoelectric transformer-based PFC LED drive," *IEEE Trans. Power Electron.*, vol. 28, no. 10, pp. 4841-4849, 2013.

- [7] K. S. Meyer, M. A. E. Andersen, and F. Jensen, "Parameterized analysis of zero voltage switching in resonant converters for optimal electrode layout of Piezoelectric Transformers," in *Proc. IEEE Power Electron. Spec. Conf.*, Rhodes, Greece, 2008, pp. 2543-2548.

- [8] M. Khanna, R. Burgos, Q. Wang, K. D. T. Ngo, and A. V. Carazo, "New Tunable Piezoelectric Transformers and Their Application in DC-DC Converters," *IEEE Trans. Power Electron.*, vol. 32, no. 12, pp. 8974–8978, 2017.

- [9] M. Ekhtiari, Z. Zhang and M. A. E. Andersen, "State-of-the-art piezoelectric transformer-based switch mode power supplies", *Proc.* 40th Annu. Conf. IEEE Ind. Electron. Soc., pp. 5072-5078, 2014.

- [10] Z. Yang, J. Forrester, J. N. Davidson, M. P. Foster and D. A. Stone, "Resonant current estimation and phase-locked loop feedback design for piezoelectric transformer-based power supplies", *IEEE Transactions on Power Electronics*, vol. 35, no. 10, pp. 10 466-10 476, 2020.

- [11] M. P. Foster, J. N. Davidson, E. L. Horsley, and D. A. Stone, "Critical Design Criterion for Achieving Zero Voltage Switching in Inductorless Half-Bridge-Driven Piezoelectric-Transformer-Based Power Supplies," *IEEE Trans. Power Electron.*, vol. 31, no. 7, pp. 5057–5066, 2016.

- [12] L. Bing, L. Wenduo, L. Yan, F. C. Lee and J. D. Van Wyk, "Optimal design methodology for LLC resonant converter", *Proc. 21st IEEE APEC Expo.*, pp. 533-538, 2006.

- [13] M. Rdgaard, T. Andersen and M. Andersen, "Empiric analysis of zero voltage switching in piezoelectric transformer-based resonant converters", *Proc. Int. conf.power electronics machines and drives*, pp. 1-6, 2012.

- [14] F. E. Bisogno, M. Radecker, A. Knoll, A. V. Carazo, A. Riedlhammer, G. Deboy, et al., "Comparison of resonant topologies for step-down applications using piezoelectric transformers", *Proc. IEEE Annu. Power Electronics Spec. Conf.*, pp. 2662-2667, 2004.

- [15] M. P. Foster, E. L. Horsley and D. A. Stone, "Predicting the zero-voltage switching profiles of half-bridge driven inductor-less piezoelectric transformer-based inverters", *IET Power Electron.*, vol. 5, no. 7, pp. 1068-1073, Aug. 2012.

- [16] M. Radecker, F. Bisogno and M. Herfurth, "Control circuit for a switch unit of a clocked power supply circuit and resonant converter", US Patent, 7969754B2, Jun. 2011.

- [17] J. D. Boles, E. Ng, J. H. Lang and D. J. Perreault, "High-Efficiency Operating Modes for Isolated Piezoelectric-Transformer-Based DC-DC Converters," 2020 IEEE 21st Workshop on Control and Modeling for Power Electronics (COMPEL), 2020, pp. 1-8.

- [18] L. Wang, Q. Wang, M. Khanna, R. P. Burgos, K. D. T. Ngo and A. V. Carazo, "Design and Control of Tunable Piezoelectric Transformer Based DC/DC Converter," 2018 IEEE Energy Conversion Congress and Exposition (ECCE), 2018, pp. 5987-5993.

- [19] L. Wang and R. P. Burgos, "Analysis of Impacts of Compensation Networks on Characteristics of Piezoelectric Transformers," 2020 IEEE 21st Workshop on Control and Modeling for Power Electronics (COMPEL), 2020, pp. 1-7.

- [20] H. I. Sewell, D. A. Stone, and C. M. Bingham, "A Describing Function for Resonantly Commutated H-Bridge Inverters," *IEEE Transactions on Power Electronics*, vol. 19, no. 4, pp. 1010–1021, 2004

- [21] Z. Yang, M. P. Foster, J. Forrester, and J. N. Davidson, "Critical design criterion for inductorless H-bridge driven piezoelectrictransformer-based power supplies." In 48th Annual Conference of the Industrial Electronics Society IECON 2022 Conference. IEEE, 2022.

- [22] H. R. Visser and P. P. J. van den Bosch, "Modelling of periodically switching networks", Proc. IEEE 22nd Annu. Power Electron. Specialists Conf., pp. 67-73, 1991.

- [23] M. P. Foster, H. I. Sewell, C. M. Bingham, D. A. Stone, D. Hente, and D. Howe, "Cyclic-averaging for high-speed analysis of resonant converters", *IEEE Trans. Power Electron.*, vol. 18, no. 4, pp. 985-993, Jul. 2003.

- [24] E. L. Horsley, "Modelling and analysis of radial mode piezoelectric

- transformers and inductor-less resonant power converters", Ph.D thesis, University of Sheffield, 2011.

- [25] E. L. Horsley, A. V. Carazo, N. Nguyen-Quang, M. P. Foster and D. A. Stone. "Analysis of inductorless zero-voltage-switching piezoelectric transformer-based converters." *IEEE Transactions on Power Electronics* 27, no. 5, pp. 2471-2483,2011.

- [26] Joo, Hyun-Woo, Chang-Hwun Lee, Jong-Seok Rho, and Hyun-Kyo Jung. "Analysis of temperature rise for piezoelectric transformer using finite-element method." *IEEE transactions on ultrasonics, ferroelectrics, and frequency control* 53, no. 8, pp. 1449-1457, 2006.

- [27] M. Umeda, K. Nakamura and S. Ueha. "Effects of vibration stress and temperature on the characteristics of piezoelectric ceramics under high vibration amplitude levels measured by electrical transient responses." *Japanese Journal of Applied Physics* 38, no. 9S, pp. 5581, 1999.

- [28] M. Umeda, S. Takahashi, Y. Sasaki, K. Nakamura, and S. Ueha. "Vibration stress and temperature dependence of piezoelectric resonators with lead–zirconate–titanate ceramics." *Electronics and Communications in Japan (Part II: Electronics)* 83, no. 9, pp. 1-7, 2000.