This is a repository copy of Optimization of normally-off  $\beta$ -Ga2O3 MOSFET with high Ion and BFOM: A TCAD study.

White Rose Research Online URL for this paper: <a href="https://eprints.whiterose.ac.uk/191265/">https://eprints.whiterose.ac.uk/191265/</a>

Version: Published Version

## Article:

Do, H.-B., Phan-Gia, A.-V., Nguyen, V.Q. et al. (1 more author) (2022) Optimization of normally-off  $\beta$ -Ga2O3 MOSFET with high Ion and BFOM: A TCAD study. AIP Advances, 12 (6). 065024. ISSN 2158-3226

https://doi.org/10.1063/5.0094418

# Reuse

This article is distributed under the terms of the Creative Commons Attribution (CC BY) licence. This licence allows you to distribute, remix, tweak, and build upon the work, even commercially, as long as you credit the authors for the original work. More information and the full terms of the licence here: https://creativecommons.org/licenses/

# Takedown

If you consider content in White Rose Research Online to be in breach of UK law, please notify us by emailing eprints@whiterose.ac.uk including the URL of the record and the reason for the withdrawal request.

# Optimization of normally-off $\beta$ -Ga $_2$ O $_3$ MOSFET with high I $_{on}$ and BFOM: A TCAD study

Cite as: AIP Advances 12, 065024 (2022); https://doi.org/10.1063/5.0094418 Submitted: 03 April 2022 • Accepted: 22 May 2022 • Published Online: 22 June 2022

#### ARTICLES YOU MAY BE INTERESTED IN

$\beta$ -Gallium oxide power electronics

APL Materials 10, 029201 (2022); https://doi.org/10.1063/5.0060327

A review of Ga<sub>2</sub>O<sub>3</sub> materials, processing, and devices

Applied Physics Reviews 5, 011301 (2018); https://doi.org/10.1063/1.5006941

Gallium oxide (Ga<sub>2</sub>O<sub>3</sub>) metal-semiconductor field-effect transistors on single-crystal  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (010) substrates

Applied Physics Letters 100, 013504 (2012); https://doi.org/10.1063/1.3674287

**ARTICLE** AIP Advances scitation.org/journal/adv

# Optimization of normally-off β-Ga<sub>2</sub>O<sub>3</sub> MOSFET with high Ion and BFOM: A TCAD study

Cite as: AIP Advances 12, 065024 (2022); doi: 10.1063/5.0094418

Submitted: 3 April 2022 • Accepted: 22 May 2022 •

Published Online: 22 June 2022

Huy-Binh Do, 1.41 D Anh-Vu Phan-Gia, 1 Van Quy Nguyen, 1 D and Maria Merlyne De Souza 2 D

# **AFFILIATIONS**

- <sup>1</sup> Faculty of Applied Science, Ho Chi Minh City University of Technology and Education, 01 Vo Van Ngan Street, Thu Duc City 700000, Vietnam

- <sup>2</sup>EEE Department, University of Sheffield, Sheffield, United Kingdom

a) Author to whom correspondence should be addressed: binhdh@hcmute.edu.vn

#### **ABSTRACT**

A combination of recessed-gate and gate-field plate in lateral β-Ga<sub>2</sub>O<sub>3</sub> metal-oxide-semiconductor field-effect transistor (MOSFET) is proposed in the Technology Computer Aided Design study to improve its ON resistance (RoN) and breakdown voltage. Enhancement-mode (E-mode) is achieved by controlling the thickness of the recessed-gate. Lateral E-mode  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET achieves a saturation current density near 120 mA/mm,  $I_{ON}/I_{OFF}$  ratio ~10 $^9$ ,  $R_{ON}$  ~91  $\Omega$  mm, and breakdown voltage of 1543 V. The optimized structure results in a prediction of a power figure-of-merit of 261 MW/cm<sup>2</sup> in a horizontal E-mode  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET.

© 2022 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution (CC BY) license  $(http://creative commons.org/licenses/by/4.0/).\ https://doi.org/10.1063/5.0094418$

# I. INTRODUCTION

Beta-gallium oxide ( $\beta$ -Ga<sub>2</sub>O<sub>3</sub>) is a promising wide bandgap semiconductor for power electronic devices, solar-blind UV photodetectors, photocatalysts, gas sensors, solar cells, phosphors, and transparent conducting films for electrodes in a variety of optoelectronic devices. <sup>1-5</sup> An ultrawide bandgap of 4.5–4.9 eV and a consequent high theoretical breakdown electric field strength (E<sub>C</sub>) of 6–9 MV/cm<sup>6</sup> lead  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> experimentally to surpass other materials, such as GaN and SiC.7 Baliga's figure of merit  $(BFOM = \varepsilon \mu E_C^3 = V_{br}^2/R_{on,sp})$  of 3444 for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is ~3 × GaN and ~8 × 4H-SiC, making Ga<sub>2</sub>O<sub>3</sub> a potential candidate in low-lost power switch applications.8 The possibility of high-quality low-cost wafers ranging from semi-insulating to moderate or highly n-doped via a melt growth method, such as Czochralski (CZ),9 or edge-defined film-fed growth (EFG), 10 is its other advantage. It is known that a challenge in improving Baliga's Figure of Merit (BFOM) of Ga<sub>2</sub>O<sub>3</sub> metal-oxide semiconductor devices is from the dielectric breakdown (E<sub>ox.br</sub>) governed by a practical maximum surface electric field,  $E_{SURF max} = \varepsilon_{ox} \times E_{ox,br}/\varepsilon_{s}$ . Using  $\varepsilon_{SiO2} = 3.9$ , a critical field of 40 MV/cm for SiO<sub>2</sub>, and  $\varepsilon_{HfO2}$  = 20, a critical field of 13 MV/cm for HfO<sub>2</sub>,<sup>12</sup> E<sub>SURF max</sub> is estimated to be 1.56 and 2.60 MV/cm for SiO<sub>2</sub> and HfO2, respectively. Recently, V<sub>br</sub> and R<sub>on,sp</sub> have been improved

to achieve high BFOM for a vertical  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> transistor. Jena *et al.* reported a vertical enhanced-mode Ga<sub>2</sub>O<sub>3</sub> transistor with a high V<sub>br</sub> of 0.96 kV and an output current of 1.0 kA/cm<sup>2</sup>. Higashiwaki et al. employed an (AlGa)<sub>2</sub>O<sub>3</sub> layer as a barrier to confine electrons in a channel layer, obtaining the threshold voltage (Vth) of +8 V with the subthreshold voltage (SS) of 129 mV/decade, three times smaller as compared to a non-back-barrier counterpart.<sup>13</sup> However, comparing the vertical and the lateral designs in terms of integrability into the CMOS processes, required in smart power devices, clearly favors the lateral field effect transistor. Depletion-mode β-Ga<sub>2</sub>O<sub>3</sub> metal-oxide-semiconductor field-effect transistors (MOSFETs) have been initially studied after the first demonstration of lateral  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs by Higashiwaki *et al.*, <sup>20</sup> which limits the enhancement-mode (E-mode) of operation. Several configurations, such as wrap-gate fin arrays,<sup>21</sup> unintentional doping (UID) channel,<sup>22</sup> back gate structure with p + -doped Si,<sup>16</sup> sourcefield plate,<sup>23</sup> gate-field plate,<sup>24</sup> a variation lateral-doping (VLD),<sup>25</sup> and recessed-gate (RG), 5,26 have been investigated to realize the normally off  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET. Although many attempts to improve BFOM via increasing V<sub>br</sub> and reducing R<sub>on</sub>, the values of BFOM of lateral devices remain much smaller as compared to vertical configuration. In detail, BFOM has been optimized to 11.4–276.7 MW/cm<sup>2</sup>, corresponding to a breakdown voltage of 0.7-3.0 kV.<sup>17,18,23</sup>

The main disadvantage in terms of increasing (BFOM =  $V_{hr}^2/R_{on,sp}$ ) is from their lateral structures, where  $V_{br}$  and  $R_{on,sp}$  are both proportional to the drain-source distance (LSD). This relationship explains why a low BFOM of 55.4 MW/cm<sup>2</sup> was obtained with high  $V_{br} \sim 3 \text{ kV.}^{24}$  To improve  $V_{br}$  of lateral  $Ga_2O_3$  MOSFETs, source-field plates<sup>28</sup> and gate-field-plate MOSFETs have also been employed<sup>18</sup> for D-mode Ga<sub>2</sub>O<sub>3</sub> MOSFETs, obtaining BFOM of 355 and 277 MW/cm<sup>2</sup>, respectively. However, E-mode operation is more preferred for integration. Recessed-gate MOSFETs<sup>26</sup> and ferroelectric charge storage gate MOSFETs (FMOSFETs)<sup>24</sup> have also been recently reported for E-mode operation with BFOM of 11.8 and 192.5 MW/cm<sup>2</sup>, respectively. The saturation current of recessed-gate Ga<sub>2</sub>O<sub>3</sub> MOSFET is twice that of FMOSFETs (at V<sub>D</sub> = 15 V, V<sub>DS</sub> = 7.5 V), so the recessed-gate Ga<sub>2</sub>O<sub>3</sub> MOSFET should be a potential candidate for the next E-mode power devices due to the lack of p-type Ga<sub>2</sub>O<sub>3</sub> for turning off the gate. However, systematic studies of a recessed-gate Ga<sub>2</sub>O<sub>3</sub> MOSFET have not been thoroughly conducted in terms of recessed-thickness, high-k dielectric layers.

This work contributes toward the challenge of developing normally off  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET. The simulated device is calibrated against experiment,  $^{26}$  considering the effects of interface traps, and the lateral recessed-gate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET is optimized to obtain an E-mode device. The breakdown voltage of recessed-gate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET is improved by combining the advantage of the recessed-gate structure by using high-k material and a gate-field plate structure. The best-in-class predicted to date of a power figure-of-merit (PFOM) is obtained for a horizontal E-mode  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET.

## II. METHODOLOGY AND SETTINGS

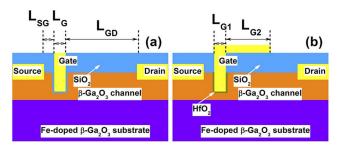

The  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs were simulated using the Silvaco Atlas 2-D device simulation tool. Two structures, namely, recessed-gate (without field plate) and field-plate recessed-gate (double gate), shown in Figs. 1(a) and 1(b), respectively, were simulated. Both devices consist of a channel layer of 200 nm Si-doped  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> on a semi-insulating Fe-doped Ga<sub>2</sub>O<sub>3</sub> substrate. The bandgap of 4.8 eV and electron affinity of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> of 4.0 eV is adopted. A typical recessed-gate Ga<sub>2</sub>O<sub>3</sub> MOSFET with gate oxide and passivation oxide SiO<sub>2</sub> is shown in Fig. 1(a) by following the typical dimensions in the previous report. The work-function of the gate-electrode

**FIG. 1.** Schematic cross section of (a) the recessed-gate  $Ga_2O_3$  MOSFET without field plate and (b) the recessed-gate  $Ga_2O_3$  MOSFET with field-plate.

is fixed at 4.33 eV, corresponding to the work function of Ti.<sup>30</sup> The metal/Ga<sub>2</sub>O<sub>3</sub> contact is assumed Ohmic with the resistance of 25 Ω mm.<sup>26</sup> Both a gate-length (L<sub>G</sub>) and a source-to-gate distance (L<sub>SG</sub>) are fixed at 1  $\mu$ m, while a source-to-drain distance (L<sub>SD</sub>) is varied from 3 to 10 µm. The field-plate recessed-gate Ga<sub>2</sub>O<sub>3</sub> MOSFET, shown in Fig. 1(b), is constructed based on the device in Fig. 1(a) where gate oxide SiO2 is replaced by HfO2, and a field-plate gate with the gate length L<sub>G2</sub> of 4 µm is added on the passivation oxide SiO<sub>2</sub> layer. To consider the effects of the high field on mobility and carrier concentration on carrier lifetime, a high field model and a concentration-dependent lifetime model were included. The Auger recombination model was utilized to count the effect of high electron concentration (N<sub>e</sub>), and a thermal model was employed to consider the self-heating effect. An impact ionization model was employed only for the breakdown voltage simulation using a transient method. TCAD parameters are calibrated against device structure in Fig. 1(a) through experimental I<sub>D</sub>V<sub>D</sub>, I<sub>D</sub>V<sub>G</sub>, breakdown voltage (V<sub>br</sub>), and density of interface traps (D<sub>it</sub>). <sup>26,31</sup> Electron low field mobility is set to be 106 cm<sup>2</sup>/Vs. Because of the damage of etching, the recessed-channel should have worse quality as compared to other regions, its low field mobility is kept at 31 cm<sup>2</sup>/Vs, which gives the best fit for experiment.<sup>26</sup> A channel carrier-concentration ( $N_D$ ) of 5.5  $\times$  10  $^{17}$  cm  $^{-3}$  and the acceptor traps of 5.0 × 10<sup>17</sup> cm<sup>-3</sup> in semi-insulating Ga<sub>2</sub>O<sub>3</sub> substrate are found to be the best fit for experiments.<sup>32</sup> The simulated V<sub>br</sub> of 504.91 V fits well with the experimental result,<sup>26</sup> connected with a peak of E<sub>C</sub> of ~21.8 MV/cm on the SiO<sub>2</sub> side, which is in agreement with the experimental E<sub>C</sub> of SiO<sub>2</sub>.<sup>33</sup> Multi-level interface traps are added to the model to fit  $I_DV_G$  and  $I_DV_D$ , where the peak of interface trap density (D<sub>it</sub>) of  $7.82 \times 10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup> at 0.3 eV from the conduction band is consistent with experimental reports.31

# **III. RESULTS AND DISCUSSIONS**

# A. Effect of recess-thickness on threshold voltage $(V_{th})$

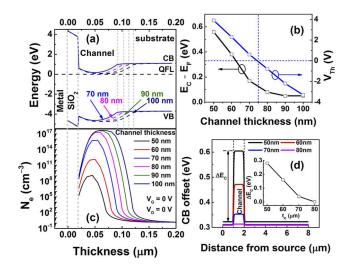

Because of a lack of a p-type channel,  $Ga_2O_3$  MOSFET is a junctionless device, controlled by depletion layer modulation under the gate bias. In this simulation, the effect of  $t_{rc}$  on  $V_{th}$  is investigated by simulating recessed-gate  $Ga_2O_3$  MOSFETs in Fig. 1(a) with  $t_{rc}$  varied from 50 to 100 nm. Figure 2(a) shows a band-diagram of RG  $Ga_2O_3$  MOSFETs at  $V_G=0$ , extracted from the cutline at the center of the gate. The device is found to operate in E-mode when the channel thickness is less than 70 nm, reaching  $E_C-E_F=0.38$  eV and  $V_{Th}=2.3$  eV at  $t_c=60$  nm, shown in Fig. 2(b). At  $t_{rc}$  larger than 75 nm, the effect of channel thickness on  $(E_C-E_F)$  is small; however, this effect is evident for  $t_{rc}$  less than 75 nm. The results agree well with a previous report<sup>21</sup> where the device operation in E-mode for  $t_{rc}$  of 60 nm. The position of the Fermi-level in Fig. 2(a) can be determined from following equation:<sup>34</sup>

$$E_C - E_F = -k_0 T ln \left(\frac{N_e}{N_C}\right), \tag{1}$$

where  $k_0$  is Boltzmann constant, T is temperature,  $N_e$  is an electron concentration in a recessed channel, and  $N_C$  is conduction band effective state density of  $3.72 \times 10^{18}$  cm<sup>-3</sup>.<sup>29</sup> Equation (1) also

**FIG. 2.** (a) Band-diagram of recessed-gate  $Ga_2O_3$  MOSFETs as a function of  $t_{rc}$  at  $V_G=0$  V. (b) The relationship between the position of Fermi-level, threshold voltage, and channel thicknesses. (c) Electron concentration ( $N_e$ ) from gate to the substrate of the structure of Fig. 1(a). (d) The relationship between conduction band offset and channel thickness from source to recessed channel to drain at 20 nm above the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/substrate interface.

explains well  $N_e$  in a recessed-channel shown in Fig. 2(c), where  $N_e$  decreases significantly when the  $t_{rc}$  decreases, from  $5.5 \times 10^{17}$  cm<sup>-3</sup> at  $t_{rc}$  of 100 nm to  $1.3 \times 10^9$  cm<sup>-3</sup> at  $t_{rc}$  of 50 nm. A strong reduction of  $N_e$  leads to a notable drop in output current (64%), which is attributed to the formation of a barrier ~0.3 eV between source and drain shown in Fig. 2(d), high enough to approach a normally off state. The results are in agreement with the report of Wong et al., where positive threshold voltage ( $V_{th}$ ) was obtained at  $t_{rc}$  less than 100 nm; however, a significant reduction of  $I_{ON}$  (~97%) was observed.<sup>35</sup>

To see the advantage of recessed gate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET, un-recessed gate β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs with different channel thicknesses are simulated in Fig. 3. Figures 3(a) and 3(b) show a shift of threshold voltage from negative to positive when channel thickness decreases from 100 to 60 nm. However, the current obtained is very small, as shown in Fig. 3(a), due to a depletion region formed at the channel/substrate interface, as shown in Fig. 3(c). At tc = 60 nm, electron concentration in the channel is less than  $1 \times 10^{15}$  cm<sup>-3</sup> although the  $N_D = 5.5 \times 10^{17} \text{ cm}^{-3}$ . This disadvantage can be eliminated with the recessed gate in Fig. 3(d), where a depletion region dominates only in the recessed region, below the gate, and charge concentration in other regions is un-changed due to the thick unrecessed region. Figure 3(e) indicates that the ON current of the recessed device is 4 orders larger than that of an un-recessed device. It means that a recessed structure keeps V<sub>th</sub> positive as well as prevents a collapse of the ON current when the channel thickness is reduced.

# B. Effect of field-plate and recessed-gate on device performance

To improve the performance of RG Ga<sub>2</sub>O<sub>3</sub> MOSFETs, a combination of gate-field plate and recessed-gate (double gate) is studied

**FIG. 3.** (a) IDVG characteristics of an un-recessed gate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET with a range of channel thicknesses from 60 to 100 nm. (b) The variation of threshold voltage as channel thickness increases from 70 to 100 nm, the threshold voltage of a device with 60 nm cannot be extracted because the maximum current is less than 0.1 mA/mm. Electron concentration in the channel of (c) an un-recessed gate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET with a channel thickness of 60 nm and (d) recessed gate  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET with a channel thickness of 200 nm and recessed-channel of 60 nm. (e) IDVG characteristics in the semi-log scale of structures (a) and (b) in Fig. 1.

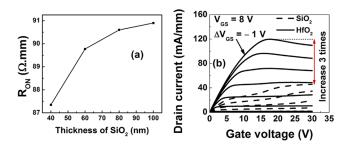

in Fig. 1(b). The parameters used in this simulation are the same as those used in Fig. 1(a), but HfO<sub>2</sub> with a thickness of 20 nm is utilized as a gate oxide. The D<sub>it</sub> profile is assumed to be the same as that used in Fig. 1(a). SiO<sub>2</sub> remains as oxide passivation on the Ga<sub>2</sub>O<sub>3</sub> surface. Power figure-of-merit ( $PFOM = V_{br}^2/R_{ON,sp}$ ) is extracted from the devices with the source-drain distance from 3 to 10  $\mu$ m, where  $R_{ON,sp}$  is a specific resistance ( $R_{ON,sp} = R_{ON} \times L_{SD}$ ) and compared with Ga<sub>2</sub>O<sub>3</sub> MOSFETs without gate-field plate (single gate). It is seen that both single and double gated devices have the same  $V_{th}$  (+1.43 V) and the  $I_{ON}/I_{OFF}$  ratio >10<sup>9</sup>.  $R_{ON}$  of gate field plate device, shown in Fig. 4(a), is smaller as compared to that of without

**FIG. 4.** (a) On resistance of gate field plate MOSFETs as a function of  $SiO_2$  passivation layer below the field plate;  $HfO_2$  is used as a dielectric material. (b) Comparison of IDVD characteristics of the single gate and gate-field plate devices using  $SiO_2$  and  $HfO_2$  as the gate oxides.

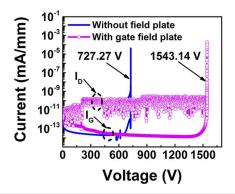

gate field plate device ( $R_{ON} = 92.1 \Omega$  mm) because of the redistribution of charge concentration of a channel below the field plate. Figure 4(a) indicates that ON resistance of gate field plate device is a function of the thickness of SiO<sub>2</sub> passivation layer, decreasing as t<sub>SiO2</sub> decreases, reaching 87.35  $\Omega$  mm at  $t_{SiO2}$  = 40 nm. Figure 4(b) shows the IDVD characteristics of gate field plate and without gate field plate devices. It is found that the saturation current density of the gate field plate device with HfO2 gate oxide increases three times as compared to that without field plate device with SiO2 gate oxide, due to a smaller capacitance oxide thickness (CET).<sup>12</sup> The low value of R<sub>ON</sub> of gate field plate device as compared to that without gate field plate device should be from the double effect of the recessed-gate and a high permittivity of HfO2, resulting in more flexible control of semiconductor Fermi-level. Figure 5 illustrates that the breakdown voltage of a double gate device is twofold larger as compared to that of a single gate device. The breakdown voltage of 1543 V, in this study, is the highest to date value predicted for E-mode RG  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs. For comparison, Feng et al. reported the V<sub>br</sub> of 670 V and low subthreshold voltage (SS) of 72 mV/dec by using ferroelectric oxide in the gate stack. Zhou et al. predicted a high breakdown voltage of 1832 V in a TCAD study of VLD β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs.<sup>25</sup> However, the lack of a clear physical picture of negative capacitance MOSFETs<sup>36</sup> and a complex fabrication-process of VLD devices leave a challenge in realizing these devices.

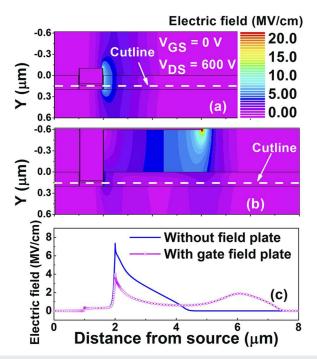

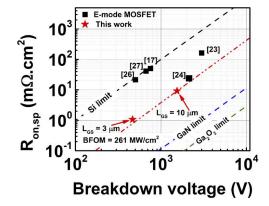

To explain the improvement of breakdown voltage in the double gate device, a simulation of electric field (E-field) distribution is conducted at  $V_{DS}=600~V$  and  $V_G=0~V$  shown in Fig. 6. The peak of E-field in a single gate device appears at the edge of the gate electrode shown in Fig. 6(a), while that in a double gate device was observed at the edge of the gate-field-plate/SiO2 interface shown in Fig. 6(b). The  $E_C\sim40~MV/cm$  of  $SiO_2^{37}$  and a re-distribution of E-field in Fig. 6(c), where  $E_C$  drops by 50% at the  $HfO_2/\beta$ -Ga<sub>2</sub>O<sub>3</sub> interface, explains the improvement of  $V_{br}$  of the double gate device. Figure 7 shows the benchmark plot of  $R_{ON}$  vs  $V_{br}$ , illustrating an increase of  $\sim\!20$  times of PFOM during a period of 5 years, from 11 MV/cm² (D-mode  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs) to 293 MV/cm² (VLD  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFETs).  $^{17,18,23-26,38}$  Despite having low  $R_{ON,sp}$  and fast switching speed, obtaining high  $V_{br}$  for E-mode RG  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET remains to be a challenge due to its

**FIG. 5.** Simulation results of breakdown voltage for without field plate device and with gate field plate devices.  $HfO_2$  is used as a high-k material for both devices.

**FIG. 6.** Electric field distribution at  $V_{GS}=0$  and  $V_{DS}=600\ V$  of (a) single gate device, (b) gate-field plate device, and (c) cutlines along  $HfO_2/Ga_2O_3$  interface from source to drain.

thin  $t_{rc}$ . The up-to-date PFOM of 193 MV/cm<sup>2</sup> was experimentally reported by Feng *et al.* for this configuration<sup>24</sup> by using ferroelectric dielectric Al<sub>2</sub>O<sub>3</sub>/Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> as a gate oxide. Recently, a record high PFOM of 0.65 GW/cm<sup>2</sup> was reported for the NiO/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> pn diode. The simulated PFOM of 261 MW/cm<sup>2</sup> obtained in this study is the highest value for E-mode RG  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET. A combination of recessed-gate structure (low R<sub>ON</sub>), high permittivity dielectric, and the re-distribution of E-field (high V<sub>br</sub>) increases PFOM by 21 times as compared to RG  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET with SiO<sub>2</sub> gate oxide.<sup>26</sup>

**FIG. 7.** Benchmark plot of specific resistance vs breakdown voltage compared to the relative theoretical limits of Si, GaN, and  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>.<sup>23,24,26,17,26</sup>

#### IV. CONCLUSION

In summary, we systematically study  $\beta\text{-}Ga_2O_3$  MOSFET using TCAD simulation. High performance normally off recessed gate-field plate  $\beta\text{-}Ga_2O_3$  MOSFET is predicted using TCAD simulation. All parameters are calibrated against published experimental data of recessed gate  $\beta\text{-}Ga_2O_3$  MOSFET. The impact of recessed-gate thickness is investigated. The output current of E-mode recessed gate-field plate  $\beta\text{-}Ga_2O_3$  MOSFET is obtained to be 120 mA/mm with  $I_{ON}/I_{OFF}$  ratio  $>10^9$  and  $R_{ON,sp}$  of 9.1 m $\Omega$  cm $^2$ . The simulations suggest a promise of a PFOM of 261 MW/cm $^2$  in recessed gate-field plate  $\beta\text{-}Ga_2O_3$  MOSFET with potential for advanced power electronics.

#### **ACKNOWLEDGMENTS**

This work was funded by the Ho Chi Minh City University of Technology and Education, Vietnam (Grant No. T2021-76T⊕).

#### **AUTHOR DECLARATIONS**

## **Conflict of Interest**

The authors have no conflicts to disclose.

#### **Author Contributions**

Huy-Binh Do: Conceptualization (lead); Formal analysis (lead); Investigation (lead); Methodology (lead); Project administration (lead); Writing – original draft (equal); Writing – review & editing (equal). Anh-Vu Phan-Gia: Data curation (equal); Investigation (equal). Van Quy Nguyen: Investigation (supporting). Maria Merlyne De Souza: Software (equal); Supervision (equal); Writing – review & editing (equal).

# DATA AVAILABILITY

The data that support the findings of this study are available from the corresponding author upon reasonable request.

## **REFERENCES**

- <sup>1</sup>H. von Wenckstern, Adv. Electron. Mater. **3**(9), 1600350 (2017).

- <sup>2</sup>S. J. Pearton, J. Yang, P. H. Cary IV, F. Ren, J. Kim, M. J. Tadjer, and M. A. Mastro, Appl. Phys. Rev. 5(1), 011301 (2018).

- <sup>3</sup>S. J. Pearton, F. Ren, M. Tadjer, and J. Kim, J. Appl. Phys. **124**(22), 220901 (2018).

- <sup>4</sup>M. Higashiwaki, K. Sasaki, H. Murakami, Y. Kumagai, A. Koukitu, A. Kuramata, T. Masui, and S. Yamakoshi, Semicond. Sci. Technol. **31**(3), 034001 (2016).

- <sup>5</sup>H. Dong, S. Long, H. Sun, X. Zhao, Q. He, Y. Qin, G. Jian, X. Zhou, Y. Yu, W. Guo, W. Xiong, W. Hao, Y. Zhang, H. Xue, X. Xiang, Z. Yu, H. Lv, Q. Liu, and M. Liu, IEEE Electron Device Lett. 40(9), 1385–1388 (2019).

- <sup>6</sup>J. Yang, M. Xian, P. Carey, C. Fares, J. Partain, F. Ren, M. Tadjer, E. Anber, D. Foley, A. Lang, J. Hart, J. Nathaniel, M. L. Taheri, S. J. Pearton, and A. Kuramata, Appl. Phys. Lett. **114**(23), 232106 (2019).

- <sup>7</sup>A. J. Green, K. D. Chabak, E. R. Heller, R. C. Fitch, M. Baldini, A. Fiedler, K. Irmscher, G. Wagner, Z. Galazka, S. E. Tetlak, A. Crespo, K. Leedy, and G. H. Jessen, IEEE Electron Device Lett. 37(7), 902–905 (2016).

- <sup>8</sup>B. J. Baliga, J. Appl. Phys. **53**(3), 1759–1764 (1982).

- <sup>9</sup>Z. Galazka, R. Uecker, D. Klimm, K. Irmscher, M. Naumann, M. Pietsch, A. Kwasniewski, R. Bertram, S. Ganschow, and M. Bickermann, ECS J. Solid State Sci. Technol. **6**(2), Q3007–Q3011 (2016).

- <sup>10</sup> A. Kuramata, K. Koshi, S. Watanabe, Y. Yamaoka, T. Masui, and S. Yamakoshi, Jpn. J. Appl. Phys. 55(12), 1202A2 (2016).

- <sup>11</sup>W. Li, D. Jena, and H. G. Xing, in *Semiconductors and Semimetals*, edited by Y. Zhao and Z. Mi (Elsevier, 2021), Vol. 107, pp. 23–47.

- <sup>12</sup>H. B. Do, Q. H. Luc, M. T. H. Ha, S. H. Huynh, T. A. Nguyen, C. Hu, Y. C. Lin, and E. Y. Chang, IEEE Electron Device Lett. 38(5), 552–555 (2017).

- <sup>13</sup>T. Kamimura, Y. Nakata, and M. Higashiwaki, Jpn. J. Appl. Phys. **60**(3), 030906 (2021)

- <sup>14</sup>M. Higashiwaki, K. Sasaki, T. Kamimura, M. Hoi Wong, D. Krishnamurthy, A. Kuramata, T. Masui, and S. Yamakoshi, Appl. Phys. Lett. **103**(12), 123511 (2013).

- <sup>15</sup>M. Higashiwaki, K. Sasaki, M. H. Wong, T. Kamimura, D. Krishnamurthy, A. Kuramata, T. Masui, and S. Yamakoshi, paper presented at the 2013 IEEE International Electron Devices Meeting, 2013.

- <sup>16</sup>H. Zhou, M. Si, S. Alghamdi, G. Qiu, L. Yang, and P. D. Ye, IEEE Electron Device Lett. 38(1), 103–106 (2017).

- <sup>17</sup>M. H. Wong, K. Sasaki, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, IEEE Electron Device Lett. 37(2), 212–215 (2016).

- <sup>18</sup>Y. Lv, H. Liu, X. Zhou, Y. Wang, X. Song, Y. Cai, Q. Yan, C. Wang, S. Liang, J. Zhang, Z. Feng, H. Zhou, S. Cai, and Y. Hao, IEEE Electron Device Lett. 41(4), 537–540 (2020).

- <sup>19</sup>J. Yoon, S. Doh, O. Gnawali, and H. Lee, IEEE Access 8, 36322–36336 (2020).

- <sup>20</sup> M. Higashiwaki, K. Sasaki, A. Kuramata, T. Masui, and S. Yamakoshi, Appl. Phys. Lett. **100**(1), 013504 (2012).

- <sup>21</sup> K. D. Chabak, N. Moser, A. J. Green, D. E. Walker, Jr., S. E. Tetlak, E. Heller, A. Crespo, R. Fitch, J. P. McCandless, K. Leedy, M. Baldini, G. Wagner, Z. Galazka, X. Li, and G. Jessen, Appl. Phys. Lett. 109(21), 213501 (2016).

- <sup>22</sup> M. H. Wong, Y. Nakata, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, Appl. Phys. Express 10(4), 041101 (2017).

- <sup>23</sup> Y. Lv, X. Zhou, S. Long, Y. Wang, X. Song, X. Zhou, G. Xu, S. Liang, Z. Feng, S. Cai, X. Fu, A. Pu, and M. Liu, Phys. Status Solidi RRL 14(3), 1900586 (2020).

- <sup>24</sup>Z. Feng, Y. Cai, Z. Li, Z. Hu, Y. Zhang, X. Lu, X. Kang, J. Ning, C. Zhang, Q. Feng, J. Zhang, H. Zhou, and Y. Hao, Appl. Phys. Lett. **116**(24), 243503 (2020).

- <sup>25</sup> X. Zhou, Q. Liu, G. Xu, K. Zhou, X. Xiang, Q. He, W. Hao, G. Jian, X. Zhao, and S. Long, IEEE Trans. Electron Devices 68(4), 1501–1506 (2021).

- <sup>26</sup> K. D. Chabak, J. P. McCandless, N. A. Moser, A. J. Green, K. Mahalingam, A. Crespo, N. Hendricks, B. M. Howe, S. E. Tetlak, K. Leedy, R. C. Fitch, D. Wakimoto, K. Sasaki, A. Kuramata, and G. H. Jessen, IEEE Electron Device Lett. 39(1), 67–70 (2018)

- <sup>27</sup> Z. Feng, X. Tian, Z. Li, Z. Hu, Y. Zhang, X. Kang, J. Ning, Y. Zhang, C. Zhang, Q. Feng, H. Zhou, J. Zhang, and Y. Hao, IEEE Electron Device Lett. 41(3), 333–336 (2020).

- <sup>28</sup> A. Bhattacharyya, P. Ranga, S. Roy, C. Peterson, F. Alema, G. Seryogin, A. Osinsky, and S. Krishnamoorthy, IEEE Electron Device Lett. **42**(9), 1272–1275 (2021).

- <sup>29</sup>Silvaco TCAD Atlas, Version V3.44.1R.

- <sup>30</sup>H. B. Do, Q. H. Luc, M. T. H. Ha, C. C. Hu, Y. C. Lin, and E. Y. Chang, IEEE Trans. Electron Devices **62**(12), 3987–3991 (2015).

- <sup>31</sup> K. Zeng, Y. Jia, and U. Singisetti, IEEE Electron Device Lett. **37**(7), 906-909 (2016).

- <sup>32</sup> A. Y. Polyakov, N. B. Smirnov, I. V. Shchemerov, S. J. Pearton, F. Ren, A. V. Chernykh, and A. I. Kochkova, Appl. Phys. Lett. 113(14), 142102 (2018).

- <sup>33</sup>D. Liu, Y. Huang, Z. Zhang, D. Chen, Q. Feng, H. You, J. Zhang, C. Zhang, and Y. Hao, ECS J. Solid State Sci. Technol. 10(12), 125001 (2021).

- <sup>34</sup>S. Sze and K. K. Ng, "Physics and properties of semiconductors-A review," in *Physics of Semiconductor Devices* (2006), pp. 5-75.

$^{\bf 35}{\rm H.~Y.~Wong,~N.~Braga,~R.~V.~Mickevicius,}$  and F. Ding, paper presented at the 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2018.

<sup>37</sup>C. Sire, S. Blonkowski, M. J. Gordon, and T. Baron, Appl. Phys. Lett. **91**(24),

242905 (2007).

38 W. Li, K. Nomoto, Z. Hu, T. Nakamura, D. Jena, and H. G. Xing, paper presented at the 2019 IEEE International Electron Devices Meeting (IEDM),

<sup>&</sup>lt;sup>36</sup>W. Cao and K. Banerjee, Nat. Commun. **11**(1), 196 (2020).