# Recovery of Photovoltaic Potential-Induced Degradation Utilizing Automatic Indirect Voltage Source

Mahmoud Dhimish, Member, IEEE, Ghadeer Badran, Member, IEEE

Abstract—Potential-induced degradation (PID) photovoltaic (PV) modules is one of the most severe types of degradation in modern modules. PID can affect crystalline silicon PV modules, and while extensive studies have already been conducted in this area, the understanding of how to recover PID is still incomplete, and it remains a significant problem in the PV industry. In this paper, an electronic circuit that can mitigate the impact of PID in PV modules is utilized. This was achieved by inducing the PV string of 1000 V when a threshold current of 100 mA is detected. A microcontroller was used to manage the current sensor data and actuate the whole circuit. The impact of the proposed circuit on PID affected PV modules are (i) improve the electroluminescence regeneration, (ii) increase the output power by up to 30% of newly PID affected modules, and up to 7.8% for old modules, (iii) reduce their temperature, known by hotspots, and (iv) despite the variations in the solar irradiance and temperature, the recovery of the PID can be obtained within 15 days or less.

Index Terms— Potential-Induced Degradation Photovoltaics; power electronics; hotspots.

#### I. INTRODUCTION

NE of the most valuable characteristics of photovoltaic (PV) technology is its high stability, with potential operational lifetimes of over 30 years. Continuous developments from academic and industrial researchers to improve PV efficiency and overcome manufacturing costs has contributed significantly to PV's success. In the wake of the accelerated growth of the PV industry, the durability and reliability of PV technologies have recently caught considerable attention from researchers, manufacturers, and investors. Although PV modules have long been considered reliable under field conditions with low degradation and failure rates, they can be affected by diverse degradation mechanisms, which collectively reduce the module crop power over time. One of the main degradation mechanisms is called potential-inducted-degradation (PID) [1-3]. For many PV systems, PID is one of the leading causes of module degradation caused by the high voltage between the encapsulants and the front glass surface, which is grounded via the substructure of the cell or the frame [4].

M. Dhimish\* and G. Badran are with the Department of Electronic Engineering, University of York, York YO10 5DD, UK. (\* corresponding author e-mail: <a href="mailto:mahmoud.dhimish@york.ac.uk">mahmoud.dhimish@york.ac.uk</a>).

PID becomes more prevailing as the module ages, and whilst it normally doesn't affect all the solar cells in the module, it does have a critical impact as it cannot be repaired [5]. For example, in recent studies [1, 6], PV modules with different types of structure (poly/monocrystalline silicon) were subjected to PID experiments under the IEC61215 standard [7]. They explain that there are 8-30% power losses under standard test conditions. However, they do not consider the impact of varying the solar irradiance, temperature or analyzing the thermal behaviour in the PID tested PV modules.

To mitigate PV modules affected by PID, it has been argued that a working electronics device cannot be permissible. In contrast, two solutions in this regard have been proposed in the literature. The first solution is to build a solar cell resistant to PID via adding another substance layer (i.e., Thin Ionomer Film [8]) or improve the glass protection of the modules [9]. The second mitigation strategy is to induce a positive voltage into the PV modules in the range between 100 to 1500 [10], and this would typically act as a reverse PID recovery. However, this has not been practically developed or at least experimented on a PV system; multiple PV modules rather than a standalone PV module.

Other algorithms are introduced to alleviate the PID through detecting PV faults such as partial shading, dust, arcing and hotspots [11, 12], yet these algorithms cannot overcome the PID problem, while they can only indicate whether the PV system has an early fault; in other words, ideally, they are classified as PV fault detection algorithms rather than PID mitigation.

To identify the consequence of PID on PV modules, electroluminescence (EL) imaging is usually performed [13-15]. In contrast, other researchers [16, 17] have suggested using photoluminescence (PL) imaging. PL imaging is more practical for inspecting large-scale PV modules. However, PL imaging cannot identify inactive areas in the cells, and the interconnection failure, whereas an EL imaging setup, can identify both failure modes [18].

This paper will discuss the construction and operation of our new electronic circuit that can mitigate the impact of PID electronically. The proposed circuit comprises a limited number of components, a current sensor, a microcontroller, MOSFET, relay, and a protection diode. Thus, marking it manageable to construct and utilize with new or old PV installations.

## II. PROPOSED CIRCUIT DESIGN AND EXPERIMENTAL PROCEDURE

### A. Proposed PID recovery circuit

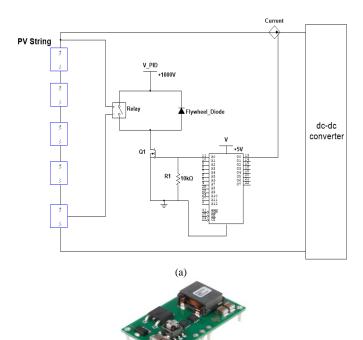

This section presents a detailed description of the proposed PID recovery circuit. The overall design of the circuit is shown in Fig. 1(a).

First, the circuit consist of a PV string that comprising five series-connected PV modules. The number of PV modules could be enlarged, depending on the voltage, current sensors and the dc-dc converter used in the system. Therefore, there is no limitation in expanding the PV capacity. Here, we used four PV modules compatible with the actual practical setup discussed in the next section. In addition, the PV string is connected in series with a current sensor before the dc-dc converter. This is a practical interpretation so that the circuit can effortlessly combine with older PV setups.

During the daytime, the PV string is generation power, hence current, and therefore, the circuit is on OFF state. Thus, a threshold current of  $I_{TH} < 100 \, mA$  was identified before actuating the circuit. The advantages to introducing this threshold are (i) to ensure that the PV string is operating under nighttime (or in some instances in a complete overcasting condition), and (ii) the circuit does not require any solar irradiance data, so that minimum number of inputs/variables are required.

A microcontroller (16f877a) is used to gather the data of the current sensor and determine its level. If  $I_{TH} < 100 \, mA$ , the circuit is shifted into ON mode. This implies that the microcontroller will provide enough voltage (>0.7 V). As a result, the N-channel's gate-source ( $V_{GS}$ ) voltage increases about its threshold ( $V_T$ ), the MOSFET channel will open, and

Fig. 1. (a) Proposed circuit design of the PID PV recovery, (b) Physical hardware implementation of the circuit.

a current flow into the relay. Here, the value of  $V_T$  must be taken from the MOSFET datasheet. Therefore, we can directly adjust the minimum voltage produced by the microcontroller to open the MOSFET's channel. The resistance value between the Drain and Source of the MOSFET,  $R_{DS(on)}$ , has also been considered. Because of the smaller  $R_{DS(on)}$ , the lower power loss it can cause. For our used MOSFET (IXFH10N100P), the value of  $R_{DS(on)}$  is equal to 1.4  $\Omega$ . Its continuous drain current ( $I_D$ ) of 10 A and the Drain Source voltage ( $V_{DSS}$ ) of 1000 V. These values are accurate under test temperature conditions is between 25°C to 150°C.

A current flow into the relay when the MOSFET's channel is open (the relay type: Relay RL 42-I). The relay coil is operated at this stage, and 1000 V is now passed to the (±) relay output terminals. According to the IEC62804 standard, the PID experiment applies -1000 V; hence, we used a reversed voltage of 1000 V to recover the PID. In addition, to prevent damage to the MOSFET, a flywheel diode (RGP10M) is connected across the relay coil. This diode clamps the reverse voltage across the coil to about 0.7 V, dissipating the stored energy and protecting the MOSFET. However, this diode can only work under dc voltage, which is the case in our application. Therefore, an alternative protection arrangement must be considered for an AC application, for example, if the circuit is applied with a dc-ac inverter.

The positive relay's output terminal is connected with the PV string positive terminal. However, the negative relay's output terminal is connected with the frame/panel of the last PV module in the string. This is typically the reverse construction of a PID experiment. In addition, it is worth noting that the actual circuit is always not on active mode. The PID recovery is only required when the circuit detects a massive increase in the voltage (usually hundreds of volts) during the nighttime. In this scenario, the circuit identifies a PID, and a reverse PID is applied. Another advantage of using the circuit is that it can be utilized with an already installed PV system with minimal construction effort. It can simply be arranged by installing the circuit before the dc-dc converter and connecting the relay's output terminals to the PV system. In Fig. 1(b), we show the physical hardware implementation of the circuit.

#### B. Experimental procedure

To verify the effectiveness of the proposed circuit, a PV string comprising five series-connected polycrystalline silicon PV modules was used (Figure 2(a)). This is a relatively new PV string that was installed back in 2016. The PV string main electrical parameters are summarized in Table I.

Table I Electrical parameters of the first examined PV string at STC conditions.

| Parameter                                  | Value    |

|--------------------------------------------|----------|

| Power at maximum power point $(P_{MPP})$   | 1100 W   |

| Current at maximum power point $(I_{MPP})$ | 7.68 A   |

| Voltage at maximum power point $(V_{MPP})$ | 143.25 V |

| Short circuit current ( $I_{SC}$ )         | 8.10 A   |

| Open circuit voltage $(V_{OC})$            | 183 V    |

Before connecting the proposed circuit into the PV string, we have first provoked a PID experiment following the IEC62804 standard by applying -1000 V for 96 hours. Note here that the temperature and humidity cannot be controlled as we have prepared this experiment on the PV system in outdoor conditions. Nevertheless, this experiment allows us to induce PID to the modules. Then we can connect the proposed circuit and investigate if it can regulate the modules to their standard working conditions.

This work also investigated the power measurements and examined the EL images before and after integrating the proposed circuit with the PV string. BrightSpot Automation EL imager was used to capture the EL images, as shown in Fig. 2(b). In addition, we have taken all the EL images under short circuit current conditions to capture the best image quality. And to obtain the power measurements, a maximum power point tracking unit (FLEXmax 80) was used; this device has a 98% tracking efficiency, and the current-voltage (I-V) [19, 20] curve can also be extracted from the collected measurements.

Fig. 2. (a) Tested PV string, (b) EL imaging camera.

#### III. RESULTS

#### A. PID effect on the PV string

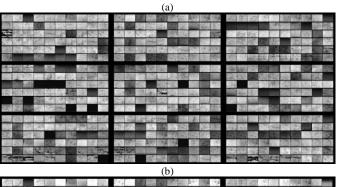

As we understand from former research that PID severely impacts the performance of PV modules [1, 7], we had experienced the same outcomes after employing the PID test on the PV string. Accordingly, we have taken the EL images before the PID test (Figure 3(a)). After the PID test was completed, 96 hours, another EL image was taken (Figure 3(b)). A critical PID condition impacts the modules, affecting the solar cells with breakdown regions, and some solar cells exhibit no electrons, known as blackout EL images [21].

In addition, the I-V curve measurements at 807 W/m<sup>2</sup> and PV cell temperature of 21°C were taken before and after the PID. There is 24.41% power loss due to PID, whereas  $I_{SC}$  and  $V_{OC}$  dropped by 7.43% and 0.89%, respectively.

Fig. 3. EL and I-V of the PV string. (a) Before PID experiment, (b) After PID experiment was completed, (c) Comparison of the I-V curves of the PV string operating under solar irradiance 807 W/m², and PV cell temperature 21°C.

#### B. PID recovery

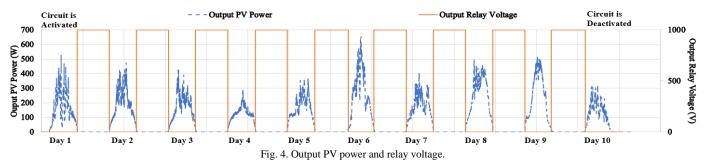

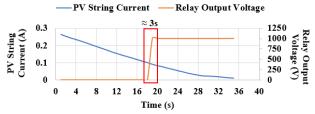

After the PID experiment was completed, the proposed circuit was connected with the PV string. As shown in Figure 4, at the end of the first day, 1000 V was induced by the relay to the PV string; of course, this happened when the PV string had limited output current ( $I_{TH} < 100 \ mA$ ). At the beginning of the second day, the relay switched again to OFF when the PV string generated a current of more than 100 mA.

The response time of the relay is shown in Fig. 5. It approximately took three seconds to apply 1000 V on the string. It is recognized that for the transition between 0 V to 1000 V, the circuit experienced a short spike/increase in the voltage, up to 1070 V. This has no impact on the PV modules, and according to the IEC62804 standard, applying up to 1500 V across the string could have no influence on the performance of the modules.

Fig. 5. Transient response of the relay.

The EL images during the PID recovery experiment are shown in Fig. 6. Every three days, we took the EL image to capture the transition of the electroluminescence (light intensity) of the individual solar cells. There is a significant difference between the image taken on the  $3^{rd}$  day (Fig. 6(a)) and the EL image taken on the  $6^{th}$  day (Fig. 6(b)).

However, we noticed a slight improvement in the EL image after 9-days, as presented in Fig. 6(c). This result suggests that the proposed circuit requires at least six successive days or more to complete the PID mitigation process. The results beyond the  $9^{th}$  day are equivalent to the circuit effects on the PV modules obtained on the  $8^{th}$  -  $9^{th}$  day.

The power loss presented in Fig. 7(a) is obtained using (1), while the MPPT unit determines the reference power  $(P_{Reference})$ , and the actual measured power of the PV string is expressed as  $P_{PV\_String}$ . Here we can reflect that the power losses of the PV string decreased as more PID recovery (1000 V) was injected into the PV string. The figure also includes the moving average curve labelled on the top of the measured samples. As a result, the power loss on the first day was estimated at  $25\pm9\%$ , and it stabilized after day 8, at  $8\pm3\%$ .

(c) Fig. 6. EL images of the PV string during the PID recovery test. (a)  $3^{rd}$  day, (b)  $6^{th}$  day, (c)  $9^{th}$  day.

Fig. 7. (a) Output power losses, including moving average, (b) Comparison of the I-V curves after the PID recovery test, the I-V curves were taken under solar irradiance  $807~\text{W/m}^2$ , and PV cell temperature  $21^\circ\text{C}$ .

Power Loss (%) =

$$\frac{P_{PV\_String} - P_{Reference}}{P_{Reference}} \times 100 \quad (1)$$

In contrast, according to Fig. 7(b), the I-V curves of the PV string during days 3, 6, and 9 were taken at solar irradiance 807 W/m<sup>2</sup> and PV cell temperature at 21~23°C. The results are summarized in Table II. The proposed circuit had significantly increased the PV string's output power by 32.2% after being activated for nine days.

Table II Electrical parameters of the examined PV string after the PID recovery.

|               |         | •             |                  |               |

|---------------|---------|---------------|------------------|---------------|

| Parameter     | PID     |               | After PID recove | ery           |

|               | Modules | 3-days        | 6-days           | 9-days        |

| $P_{MPP}$ (W) | 705.4   | 731.6         | 817.5            | 933.2         |

|               |         | $(\pm 3.7\%)$ | $(\pm 15.8\%)$   | (±32.2%)      |

| $I_{SC}$ (A)  | 7.48    | 7.603         | 7.88             | 7.90          |

|               |         | $(\pm 1.6\%)$ | (±5.3%)          | (±5.6%)       |

| $V_{oc}(V)$   | 178.1   | 179.1         | 179.4            | 179.4         |

|               |         | $(\pm 0.5\%)$ | $(\pm 0.7\%)$    | $(\pm 0.7\%)$ |

Finally, we have investigated the thermal impact of the PID on the examined PV string. Therefore, thermal images are captured (Fig. 8) using a FLIR E54 thermal imaging camera with thermal sensitivity of  $\pm 0.1$ °C, and these images were taken under solar irradiance at 790 W/m² and ambient temperature 23°C.

According to Fig. 8(a), it is realized that after the initial PID test on the PV string, the PV modules had an increase in their surface temperature, while the average solar cell temperature across the modules is 37°C. In contrast, Fig. 8(b) shows that after 9-days of PID recovery, the modules are operating at nearly 23°C. There are still several hotspots even after the PID recovery was applied; this is typically due to the severe impact of the PID, forming cracks, breakdown regions, and an increase in the solar cells shunt resistance [16, 22].

Fig. 8. Thermal image of the examined PV string. (a) After PID, (b) After PID recovery (day 9).

#### IV. EXPERIMENTAL VERIFICATION ON AGED PV SYSTEM

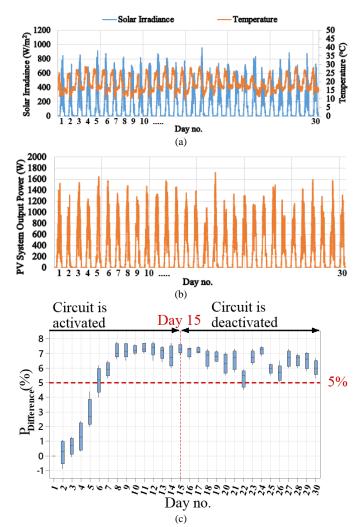

In the previous section, we have demonstrated the results of the proposed circuit on relatively new PV systems, where we have injected the modules with a PID (-1000 V) for 96 hours. Then we experiment with how our circuit can mitigate the PID effect on the modules. However, in this section, we show the results of employing the proposed circuit into an old PV system installed in 2013 (Fig. 9(a)). The PV string comprises nine series-connected polycrystalline silicon PV modules, and its main electrical parameters are summarized in Table III.

Table III Electrical parameters of the second examined PV string at STC conditions.

| Conditions.                                |         |

|--------------------------------------------|---------|

| Parameter                                  | Value   |

| Power at maximum power point $(P_{MPP})$   | 1950 W  |

| Current at maximum power point $(I_{MPP})$ | 7.55 A  |

| Voltage at maximum power point $(V_{MPP})$ | 258.3 V |

| Short circuit current $(I_{SC})$           | 8.05 A  |

| Open circuit voltage $(V_{OC})$            | 331.2 V |

We have discovered that the PV modules have already been subjected to PID for an unknown period through EL imaging detection (Fig. 9(b)). We also have noticed that several cells have been affected by major cracks. After utilizing the proposed circuit in the PV system, we have taken the EL image after nine days, presented in Fig. 9(c). After that, we carried out the EL process for 15 days and realized that there were no further increases in the light intensity of the EL images of the cells or the output power from day eight onwards.

To examine the impact of the proposed circuit on the output power of the PV system, we had to correlate the output power with reference irradiance and PV cell temperature, calculated using (2). Here the temperature can be within  $\pm 5^{\circ}$ C because it is impossible to capture the identical irradiance and temperature every day; adding this range allows us to add

Fig. 9. (a) Second examined PV system, (b) EL image of the modules before the PID test, (c) EL image of the modules after the PID recovery was deployed, this image has been taken after 9-days of the deployment of the proposed circuit.

extra data for the power difference identification.  $P_{Day(1)G(j)T(k)}$  represents all measurements taken on day one at selected irradiance (G(j)) and temperate (T(k)). This data is then subtracted by the subsequent days  $P_{Day(i)G(j)T(k)}$ . If the  $P_{Difference}$  is positive, it indicates an increase in the PV output power, it also confirms that our proposed circuit had partially recovered the PID affecting the PV modules.

$$P_{Difference}(\%) = \frac{P_{Day(i)G(j)T(k)} - P_{Day(1)G(j)T(k)}}{P_{Day(1)G(j)T(k)}} \times 100$$

(2)

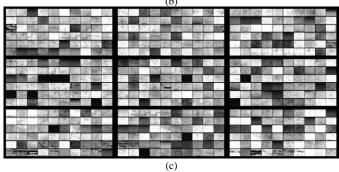

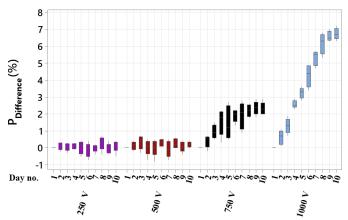

As stated earlier, the circuit was activated for 15 days. However, we have still taken the measurements and computed the  $P_{Difference}$  using (2) for continues 30-days. In contrast, the data log of the solar irradiance and the PV cell temperature is shown in Fig. 10(a), and Fig 10(b) presents the PV output power.

The results of the power difference are shown in Fig. 10(c). The power difference is zero on the first day as this day corresponds to  $P_{Day(1)G(j)T(k)}$  in equation (2). It is then recognized that the power difference is always below +5% up to the fifth day. We have seen an immeasurable increase in the power difference starting from day 6, where the peak increase

in the power, 7.8%, is discovered on days 8 and 11. In the subsequent days (16 to 30), where the circuit was deactivated, we have seen a slight drop in the power difference but still achieving more than +5%. Therefore, this result proves that our proposed circuit can increase the output power of the old/aged PV modules already affected by PID, and it is not necessary to activate the PID recovery circuit for longer than 15-days. Finally, we summarized some cases in Table IV to explain the cell EL image transformation.

Based on this experiment's results, we can further conclude that the device's activation and the PID's recovery have been accomplished despite the variations in the solar irradiance or temperature.

Fig. 10. Data taken from the second examined PV system. (a) Solar irradiance, (b) Output power measurements, (c) Power difference calculated using equation (2).

#### V. IMPACT OF VARYING PID RECOVERY VOLTAGE

Four different monocrystalline silicon PV modules were examined while varying the indirect voltage supplied by the PID recovery circuit. The PV modules' main electrical parameters are summarized in Table V. These modules were purchased in 2018 and were frequently used for indoor testing experiments.

Table IV Solar cell sample before and after the PID recovery.

| Table IV Solai cell sample before and after the I ib recovery. |                    |                                                                                                                                                                                    |  |

|----------------------------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PID cell                                                       | After PID recovery | comments                                                                                                                                                                           |  |

|                                                                | 1911               | Increase in the light intensity of the cell all around the surface.                                                                                                                |  |

|                                                                | 11/2               | The bottom side has been improved, yet the top side of the cell has a slight change in the light intensity.                                                                        |  |

|                                                                | A A                | A substantial recovery is observed in this case. The combination of the breakdown and cracks has severely affected the cell, but it only can be identified after the PID recovery. |  |

|                                                                |                    | In this case, no recovery was possible. This might be due to a significant breakdown or critical leakage in the current [23, 24].                                                  |  |

|                                                                |                    | The breakdown and cracks cannot be mitigated after the PID recovery. However, the cell has an increase in the light intensity across the non-cracked parts of the cell.            |  |

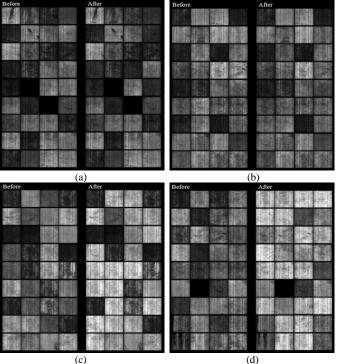

This experiment was accomplished by changing the voltage source of the relay. Four different voltage levels were analysed: 250 V, 500 V, 750 V, and 1000 V. The applied the PID test for ten continuous days. For example, in Fig. 11 we show the construction of the experiment, the positive high-voltage power supply is connected with the frame of the PV module, while the negative is connected with the junction box connectors.

Table V Electrical parameters of the PV modules at STC conditions.

| Parameter                                  | Value   |

|--------------------------------------------|---------|

| Power at maximum power point $(P_{MPP})$   | 136.3 W |

| Current at maximum power point $(I_{MPP})$ | 5.8 A   |

| Voltage at maximum power point $(V_{MPP})$ | 23.5 V  |

| Short circuit current $(I_{SC})$           | 6.10 A  |

| Open circuit voltage $(V_{OC})$            | 32.2 V  |

Fig. 11. Schematic of the actual connection of the PID recovery with a PV module.

The output EL images at each voltage level are shown in Fig. 12. At the first two voltage levels, 250 V and 500 V, we can conclude that there were no enhancements in the insanity of the solar cell EL images. However, a minor change in the intensity of the EL image taken for the module connected with 750 V. In contrast, the best EL image transformation is observed for the PV module connected with 1000 V.

Fig. 12. EL images before the PID recovery and after 10 days of the PID recovery under different voltage levels. (a) 250~V, (b) 500~V, (c) 750~V, and (d) 1000~V.

Similar to the previous section, we have calculated using (2) the power difference of each PV module, compared with its first-day output power. The results of the four tested PV modules are shown in Fig. 13. There is no increase in the  $P_{Difference}$  for the first and second PV modules (subjected to 250 V and 500 V). However, it is observed that there is a slight increase in the  $P_{Difference}$  for the third PV module, which was subjected to a PID recovery voltage of 750 V. The maximum power difference is equal to 2.9% observed on the

Fig. 13. Power difference calculated using equation (2).

9<sup>th</sup> day. The last PV module, connected with 1000 V, had the highest increase in the output power, peaking at 7% on days 9 and 10.

This section shows that careful consideration of the voltage level of any PID recovery circuit development must be considered. In our case, the optimum performance of the PID recovery was achieved using 1000 V; we assume here that we require to mitigate the PID in a short period.

#### VI. COMPARATIVE STUDY

Our work has been compared with recent studies on PID recovery designs, as shown in Table VI, [10] and [25-27]. All the PID recovery algorithms available in the literature require changing the actual solar cells' anti-reflection coating (APC), such as adapting Poly Olefin [10] or using T<sub>i</sub>/IrO<sub>2</sub>–C<sub>o</sub>O2 anode [26]. Also, different models propose changing the back sheet of the PV modules, such as [27]. These are non-practical solutions to mitigate PID for already made PV modules or those installed in the field. To the best of our knowledge, we have not come across any previous work on mitigating the PID genuinely using power electronic devices as we suggest in this work. Hence, our work shines in the direction of mitigating PID for new as well as aged PV modules with limited complexity in terms of the design and integration of the device.

The limitation of our proposed device is that it has to supply 1000 V into the PV string. Therefore, it is required to connect the device to the PV string with careful attention to the positive and negative pins of the relay. In addition, it is shown earlier in Fig. 1 that a flywheel diode is connected to protect the circuit when the relay is faulty. However, we still recommend controlling the device via a low-voltage microcontroller. If a reverse voltage develops, the microcontroller can immediately go faulty (open-circuit), protecting the dc-dc converter from receiving the reversed high voltage.

Table VI Comparative study of the results obtained in this paper vs [10] and

| [23-27].  |                                                                                                                            |                      |                                                        |

|-----------|----------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------------------|

| Paper     | Anti-PID method                                                                                                            | $P_{Difference}(\%)$ | Validation process                                     |

| Ref. [10] | Using Poly Olefin<br>materials with low<br>water vapor through<br>rate                                                     | 12%                  | EL imaging for<br>690 hours                            |

| Ref. [25] | Applying direct<br>plasma enhanced<br>chemical vapor<br>deposition                                                         | 2.79%                | EL imaging for<br>96 hours                             |

| Ref. [26] | Utilizing a liquid oxidation technique by utilizing T <sub>i</sub> /IrO <sub>2</sub> – C <sub>o</sub> O <sub>2</sub> anode | 10%                  | EL imaging for<br>96 hours                             |

| Ref. [27] | Using aluminum<br>backsheet<br>composed of<br>polyethylene<br>terephthalate<br>(PET)/aluminum/PET                          | 5%                   | $P_{Difference}(\%)$ ratio                             |

| This work | Using Anti-PID<br>indirect voltage of<br>+1000V                                                                            | 7%                   | EL imaging for 96 hours and $P_{Difference}(\%)$ ratio |

On the other hand, the previous anti-PID methods presented in Table VI depend on improving the solar cells' physical or chemical structure. However, our solution to the PID problem is combining an electronic device without crossing with the actual PV manufacturing. Therefore, the proposed device is expected to consume a small amount of energy, which is calculated using (3). The device has an applied voltage of 1000 V, and the current is limited to 20 mA. Therefore, the maximum power is equal to 20 W. On the activation of the device over 10-hours every day (time from sunset to sunrise), the total consumed energy is maximum equal to 0.2 kWh.

$$Energy = \frac{Power in Watts}{1000} \times Number of hours$$

(3)

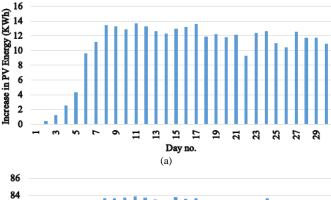

Suppose we consider the experiment previously explained in section IV. The actual measured vs theoretical energy difference is 47.99 kWh; this value is set as our threshold. Therefore, the increase in PV energy for the first day is equal to zero (47.99 kWh subtracted by 47.99 kWh), as shown in Fig. 14(a). For the subsequent days, an increase of 13 kWh in PV energy production started to peak on the eighth day. This result suggests that even though the device is consuming 0.2 kWh, there is an increase of about 13 kWh in total after using the proposed device.

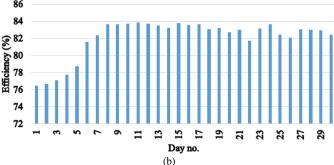

In addition, the efficiency (calculated using (4)) was estimated for the 30-days experiment. As a result, it is confirmed in Fig. 14(b) that the efficiency of the PV system increased from approximately 76% on the first day to above 80% on days six onwards.

$$\begin{array}{l} \textit{Efficiency} = \\ \frac{\textit{Measured Energy} - \textit{Energy Consumed by the Developed Device}}{\textit{Theoretical Energy}} \end{array} \tag{4}$$

Fig. 14. (a) Difference in the PV energy, (b) Overall Efficiency of the PV system.

#### VII. CONCLUSIONS

An electronic circuit that can mitigate the impact of PID in PV modules was presented in this study. This was achieved by inducing the PV string of 1000 V when a threshold current of 100 mA is detected. A microcontroller was used to manage the current sensor data and actuate the whole circuit. It was demonstrated that the impact of the proposed circuit on PID affected modules are (i) improve the electroluminescence regeneration, (ii) increase the output power by up to 30% of newly PID affected modules, and up to 7.8% for old modules, and (iii) reduce the temperature (hotspots) of the modules. Ultimately, our proposed circuit can benefit the PV industry to produce an appropriate PID-resistance design and materials and help understand PID modules' operation response under such events. Finally, the activation of the circuit and the full PID recovery can be obtained within 15-days despite the variations of solar irradiance and temperature.

#### REFERENCES

- [1] L. Ciani, M. Catelani, E. A. Carnevale, L. Donati and M. Bruzzi, "Evaluation of the Aging Process of Dye-Sensitized Solar Cells Under Different Stress Conditions," in *IEEE Transactions on Instrumentation* and Measurement, vol. 64, no. 5, pp. 1179-1187, May 2015, doi: 10.1109/TIM.2014.2381352.

- [2] M. K. Alam, F. Khan and A. M. Imtiaz, "Optimization of Subcell Interconnection for Multijunction Solar Cells Using Switching Power Converters," in *IEEE Transactions on Sustainable Energy*, vol. 4, no. 2, pp. 340-349, April 2013, doi: 10.1109/TSTE.2012.2223493.

- [3] K. Sporleder et al., "Potential-Induced Degradation of Bifacial PERC Solar Cells Under Illumination," in IEEE Journal of Photovoltaics, vol. 9, no. 6, pp. 1522-1525, Nov. 2019, doi: 10.1109/JPHOTOV.2019.2937231.

- [4] M. Florides, G. Makrides and G. E. Georghiou, "Electrical and Temperature Behavior of the Forward DC Resistance With Potential Induced Degradation of the Shunting Type in Crystalline Silicon Photovoltaic Cells and Modules," in *IEEE Journal of Photovoltaics*, vol. 11, no. 1, pp. 16-25, Jan. 2021, doi: 10.1109/JPHOTOV.2020.3030191.

- [5] P. Hacke *et al.*, "Accelerated Testing and Modeling of Potential-Induced Degradation as a Function of Temperature and Relative Humidity," in *IEEE Journal of Photovoltaics*, vol. 5, no. 6, pp. 1549-1553, Nov. 2015, doi: 10.1109/JPHOTOV.2015.2466463.

- [6] W. Luo et al., "Investigation of the Impact of Illumination on the Polarization-Type Potential-Induced Degradation of Crystalline Silicon Photovoltaic Modules," in *IEEE Journal of Photovoltaics*, vol. 8, no. 5, pp. 1168-1173, Sept. 2018, doi: 10.1109/JPHOTOV.2018.2843791.

- [7] C. B. Jones, B. Hamzavy, W. B. Hobbs, C. Libby and O. Lavrova, "IEC 61215 Qualification Tests vs Outdoor Performance using Module Level In Situ I-V Curve Tracing Devices," 2018 IEEE 7th World Conference on Photovoltaic Energy Conversion (WCPEC) (A Joint Conference of 45th IEEE PVSC, 28th PVSEC & 34th EU PVSEC), 2018, pp. 1286-1291, doi: 10.1109/PVSC.2018.8548222.

- [8] J. Kapur, K. M. Stika, C. S. Westphal, J. L. Norwood and B. Hamzavytehrany, "Prevention of Potential-Induced Degradation With Thin Ionomer Film," in *IEEE Journal of Photovoltaics*, vol. 5, no. 1, pp. 219-223, Jan. 2015, doi: 10.1109/JPHOTOV.2014.2365465.

- [9] A. P. Patel, A. Sinha and G. Tamizhmani, "Field-Aged Glass/Backsheet and Glass/Glass PV Modules: Encapsulant Degradation Comparison," in *IEEE Journal of Photovoltaics*, vol. 10, no. 2, pp. 607-615, March 2020, doi: 10.1109/JPHOTOV.2019.2958516.

- [10] Q. Wang, "Research on the effect of encapsulation material on anti-PID performance of 1500 V solar module," in *Optik*, vol. 202, pp. 163540, Feb. 2020, doi: 10.1016/j.ijleo.2019.163540.

- [11] B. Su, H. Chen, Y. Zhu, W. Liu and K. Liu, "Classification of Manufacturing Defects in Multicrystalline Solar Cells With Novel Feature Descriptor," in *IEEE Transactions on Instrumentation and Measurement*, vol. 68, no. 12, pp. 4675-4688, Dec. 2019, doi: 10.1109/TIM.2019.2900961.

- [12] R. Platon, J. Martel, N. Woodruff and T. Y. Chau, "Online Fault Detection in PV Systems," in *IEEE Transactions on Sustainable Energy*, vol. 6, no. 4, pp. 1200-1207, Oct. 2015, doi: 10.1109/TSTE.2015.2421447.

- [13] M. Dhimish, V. Holmes and P. Mather, "Novel Photovoltaic Micro Crack Detection Technique," in *IEEE Transactions on Device and Materials Reliability*, vol. 19, no. 2, pp. 304-312, June 2019, doi: 10.1109/TDMR.2019.2907019.

- [14] M. N. Akram and S. Lotfifard, "Modeling and Health Monitoring of DC Side of Photovoltaic Array," in *IEEE Transactions on Sustainable Energy*, vol. 6, no. 4, pp. 1245-1253, Oct. 2015, doi: 10.1109/TSTE.2015.2425791.

- [15] J. Xu, Y. Liu and Y. Wu, "Automatic Defect Inspection for Monocrystalline Solar Cell Interior by Electroluminescence Image Self-Comparison Method," in *IEEE Transactions on Instrumentation and Measurement*, vol. 70, pp. 1-11, 2021, Art no. 5016011, doi: 10.1109/TIM.2021.3096602.

- [16] B. Doll, J. Hepp, M. Hoffmann, R. Schüler, C. Buerhop-Lutz, I. M. Peters, J. A. Hauch, A. Maier and C. J. Brabec, "Photoluminescence for Defect Detection on Full-Sized Photovoltaic Modules," in *IEEE Journal of Photovoltaics*, vol. 11, no. 6, Nov. 2021, doi: 10.1109/JPHOTOV.2021.3099739.

- [17] C. Schuss et al., "Detecting Defects in Photovoltaic Panels With the Help of Synchronized Thermography," in *IEEE Transactions on Instrumentation and Measurement*, vol. 67, no. 5, pp. 1178-1186, May 2018, doi: 10.1109/TIM.2018.2809078.

- [18] M. Dhimish and P. Mather, "Development of Novel Solar Cell Micro Crack Detection Technique," in *IEEE Transactions on Semiconductor Manufacturing*, vol. 32, no. 3, pp. 277-285, Aug. 2019, doi: 10.1109/TSM.2019.2921951.

- [19] A. Arya, P. Kumar and S. Anand, "Methodology of an Accurate Static I–V Characterization of Power Semiconductor Devices," in *IEEE Transactions on Instrumentation and Measurement*, vol. 69, no. 10, pp. 7703-7715, Oct. 2020, doi: 10.1109/TIM.2020.2984099.

- [20] P. R. Ortega et al., "Low-Cost High-Sensitive Suns-\$V\_{\text{oc}}\$ Measurement Instrument to Characterize c-Si Solar Cells," in *IEEE Transactions on Instrumentation and Measurement*, vol. 69, no. 9, pp. 6429-6435, Sept. 2020, doi: 10.1109/TIM.2020.2967136.

- [21] M. Dhimish and P. Mather, "Ultrafast High-Resolution Solar Cell Cracks Detection Process," in *IEEE Transactions on Industrial Informatics*, vol. 16, no. 7, pp. 4769-4777, July 2020, doi: 10.1109/TII.2019.2946210.

- [22] A. Sachenko, V. Kostylyov, I. Sokolovskyi and M. Evstigneev, "Effect of Temperature on Limit Photoconversion Efficiency in Silicon Solar Cells," in *IEEE Journal of Photovoltaics*, vol. 10, no. 1, pp. 63-69, Jan. 2020, doi: 10.1109/JPHOTOV.2019.2949418.

- [23] M. Dhimish, V. d'Alessandro and S. Daliento, "Investigating the Impact of Cracks on Solar Cells Performance: Analysis based on Nonuniform and Uniform Crack Distributions," in *IEEE Transactions on Industrial Informatics*, early access, June 2021, doi: 10.1109/TII.2021.3088721.

- [24] C. E. Clement, J. P. Singh, E. Birgersson, Y. Wang and Y. S. Khoo, "Illumination Dependence of Reverse Leakage Current in Silicon Solar Cells," in *IEEE Journal of Photovoltaics*, vol. 11, no. 5, pp. 1285-1290, Sept. 2021, doi: 10.1109/JPHOTOV.2021.3088005.

- [25] T. C. Chen, T. W. Kuo, Y. L. Lin, C. H. Ku, Z. P. Yang and I. S. Yu, "Enhancement for potential-induced degradation resistance of crystalline silicon solar cells via anti-reflection coating by industrial PECVD methods," in *Coatings*, vol. 8, no. 12, pp. 418, Nov. 2018, doi: 10.3390/coatings8120418.

- [26] Y. Yang, Y. F. Zhao, C. S. Tang, S. Zou, Y. Q. Yu, X. P. Ma, Y. Zhou, X. D. Su, and Y. Xin, "Reducing potential induced degradation of silicon solar cells by using a liquid oxidation technique," in *Solar Energy Materials and Solar Cells*, vol. 183, pp. 101-106, April 2018, doi: 10.1016/j.solmat.2018.04.012.

- [27] S. Yamaguchi, C. Yamamoto, A. Masuda and K. Ohdaira. "Influence of backsheet materials on potential-induced degradation in n-type crystalline-silicon photovoltaic cell modules," in *Japanese Journal of Applied Physics*, vol 58, pp. 120901, Nov. 2019, doi: 10.7567/1347-4065/ab4fd2.