This is a repository copy of Semantics-preserving cosynthesis of cyber-physical systems.

White Rose Research Online URL for this paper: https://eprints.whiterose.ac.uk/164989/

Version: Accepted Version

#### Article:

Roy, Debayan, Zhang, Licong, Chang, Wanli orcid.org/0000-0002-4053-8898 et al. (2 more authors) (2018) Semantics-preserving cosynthesis of cyber-physical systems. Proceedings of the IEEE. pp. 171-200. ISSN 1558-2256

https://doi.org/10.1109/JPROC.2017.2779456

#### Reuse

Items deposited in White Rose Research Online are protected by copyright, with all rights reserved unless indicated otherwise. They may be downloaded and/or printed for private study, or other acts as permitted by national copyright laws. The publisher or other rights holders may allow further reproduction and re-use of the full text version. This is indicated by the licence information on the White Rose Research Online record for the item.

#### **Takedown**

If you consider content in White Rose Research Online to be in breach of UK law, please notify us by emailing eprints@whiterose.ac.uk including the URL of the record and the reason for the withdrawal request.

# Semantics-Preserving Cosynthesis of Cyber-Physical **Systems**

While control theory provides methods for designing provably correct controllers, there is a lack of available techniques to ensure that high-level controller models are transformed into implementations while preserving model-level semantics and safety properties. This paper reviews recent efforts to address this issue using cyber-physical system (CPS)-oriented controller/platform cosynthesis techniques.

By Debayan Roy<sup>®</sup>, Student Member IEEE, Licong Zhang, Student Member IEEE, WANLI CHANG, Member IEEE, SANJOY K. MITTER, Fellow IEEE, AND SAMARJIT CHAKRABORTY, Senior Member IEEE

ABSTRACT | Software-based control of physical systems is common in domains such as automotive, avionics, and industrial automation. Safety of such systems is determined by control-theoretic properties such as stability, settling time, and peak overshoot. These properties strongly depend on the software code generated from high-level controller models, and the implementation of such code on an embedded platform. To ensure safety, the semantics of the system model considered for controller design must be faithfully preserved in the platform implementation. However, traditionally, controller design and implementation platform design are carried out in isolation, followed by their integration, which often relies on simulations to estimate the behavior of the controllers. Thus, safety properties that were proven at the model level using control-theoretic tools can no longer be established in an actual implementation. This makes the design of embedded control systems costly, error prone, and hinders certification. In this paper, we review recent efforts in control-platform cosynthesis techniques toward addressing this problem. Here, the control and the embedded systems communities have come together to adopt a cyber-physical system (CPS)-oriented design paradigm. This cosynthesis paradigm integrates the design of control algorithms and platform parameters within a holistic optimization framework and accounts for relevant details from both sides. We survey the evolution of design approaches for such cosynthesis and show how-the originally disjoint-controller and the platform design methods are gradually converging.

**KEYWORDS** | Control systems; cosynthesis; cyber-physical systems; embedded control systems; embedded systems; platform aware; safety

Manuscript received March 25, 2017; revised August 4, 2017; accepted August 4, 2017. Date of current version December 20, 2017. This work was supported by Deutsche Forschungsgemeinschaft (DFG) through the Technical University of Munich (TUM) International Graduate School of Science and Engineering (IGSSE).

D. Roy, L. Zhang, and S. Chakraborty are with the Real-Time Computer Systems. Department of Electrical and Computer Engineering, Technical University of Munich, 80333 Munich, Germany (e-mail: debayan.roy@tum.de; licong.zhang@tum.de; samariit@tum.de).

W. Chang is with the Department of Computer Science, University of York, UK (e-mail: wanli.chang@york.ac.uk).

S. K. Mitter is with the Laboratory for Information and Decision Systems, Electrical Engineering and Computer Science, Massachusetts Institute of Technology, Cambridge, MA 02139 USA (e-mail: mitter@mit.edu).Digital Object Identifier: 10.1109/ JPROC.2017.2779456

#### I. INTRODUCTION

Over the last ten years the concept of cyber-physical systems (CPSs) has emphasized the integrated modeling and analysis of computational platforms and the physical processes that are controlled by such platforms. One typical class of CPSs is made up of embedded control systems. In such a system, physical processes are controlled by a piece of software running on an embedded platform. Such systems are commonly found in automotive, avionics, industrial automation, and medical devices.

These systems are often safety critical with strict requirements on stability and performance (characterized by settling time, peak overshoot, or similar metrics) [1] and must meet certain certification standards [2], [3]. Traditionally, the design of control algorithms and the embedded platforms on which such algorithms are to be implemented are designed by different groups of engineers with different expertise. Such separation of concerns while common in the general-purpose computing domain becomes problematic for embedded control systems. Here, a fundamental challenge in ensuring that safety properties at the model level (or controller design stage) hold true in an implementation requires that model-level semantics are faithfully preserved when generating implementations from the models. This is, however, not straightforward considering that current controller design methods are mostly based on idealistic assumptions on the implementation platform, such as: computing the control law takes negligible time; there are no sensor-to-controller and controller-to-actuator delays; control inputs can be computed with infinite precision; and when software code is generated from high-level models (such as those specified in Matlab/Simulink), the code generator does not introduce any side effects and accurately preserves the model level semantics. As implementation platforms become more complex, distributed, and heterogeneous, these assumptions are increasingly not true, thereby resulting in a large deviation in the behavior of an implementation from the designed controllers at the model level, and often violating safety properties that were true at the model level.

Here, the question is: How should platform configuration parameters—e.g., scheduling policies/parameters, arithmetic precision, code generation policies—be chosen so that model-level semantics are preserved in an implementation? Given an already designed (model-level) controller, the choice of such platform parameters may be restricted or in the worst case there might not be any feasible platform parameters. Since there might be multiple controllers that satisfy given stability and performance specifications (safety properties), a better approach is to determine the controller and platform configuration parameters together. In other words, by cosynthesizing the controller and platform configuration parameters—i.e., as a part of a common optimization framework—we can ensure that the two designs are compatible (or model-level semantics are preserved) and there is a larger set of parameters that may be explored [4].

In this paper, we survey such cosynthesis techniques for embedded control systems design and implementation. We first study the problems with separation of concerns, where controller design and platform implementation are carried out in isolated design spaces without sufficient knowledge of each other. Subsequently, we survey different works that follow a CPS-oriented approach and broadly classify them in terms of whether 1) the implementation platform is fixed and the control algorithm is adapted to fit the platform architecture [as in networked control systems (NCSs)

where the characteristics of the wireless network such as delay and packet loss probabilities are given and the control algorithms are designed taking them into account]; 2) the control algorithm and its assumptions are given and the platform is designed to meet these assumptions as closely as possible (e.g., by designing appropriate scheduling and resource allocation policies); or 3) it is a true cosynthesis where the parameters of the control algorithms and the implementation platform are jointly determined within an integrated optimization framework.

Recently, a lot of work in this area has been done, especially in the context of automotive embedded control systems. This is because automotive software systems implement a large number of safety-critical control loops. They have to be implemented on a resource-constrained, distributed, and heterogeneous platform architecture, and increasingly need to be certified. This combination of requirements makes it a challenging and a particularly suitable domain for studying design methods for embedded control systems. Hence, most of the examples we review in this paper are from this domain. However, the problems and the solutions that we discuss in this paper are also relevant to other CPS domains. In particular, we survey several works on NCSs that are commonly found in avionics, power grid, and industrial-automation-related CPSs. We believe that it is possible to leverage the progress made in NCSs and extend existing cosynthesis approaches from the automotive domain to other CPS domains as well.

#### A. Separation of Concerns

Automatic control is a well-studied subject with several decades of history and a large pool of design methods. Early works on design and analysis of a control system have focused on the mathematical model of the closed-loop system, including the plant and the controller. The controller is designed such that the system is stable and certain performance requirements, e.g., settling time, peak overshoot, and energy constraints are satisfied. However, these works do not consider implementation related details such as nonnegligible and variable times for software execution and data transmission, faulty networks, and finite precision arithmetic.

Embedded platform design is also well known and is composed of several stages: 1) task partitioning and mapping; 2) frame packing (for communication messages); and 3) task and frame scheduling. Platform design and analysis consider timing properties, e.g., application latencies, periods, relative deadlines, task execution times, and message frame transmission times. The main focus has been to synthesize implementations that are schedulable (i.e., all real-time software tasks meet their deadlines), and resource efficient (i.e., minimum usage of computation and communication resources). However, this theory is not directly applicable to control applications as control requirements such as stability and performance cannot always be

expressed as timing properties such as deadlines and periods (and when expressed in this form, the parameters can be overly pessimistic).

#### B. Safety Challenges for CPS Design: The Semantic Gap

In the context of CPSs, the separate design of controllers and platform parameters leads to a semantic gap between the system models considered in the controller design and the actual implementation. On one hand, the controller design is only influenced by the physical plant. Therefore, system stability and performance are derived without considering the cyber part, i.e., the implementation on the embedded platform. However, the implementation-related timing properties such as sampling period and sensing-to-actuation delay may degrade the performance and in the worst case may also cause system instability. Thus, the semantics of the control models may not be preserved in the implementation when the controller design is oblivious to the implementation details. On the other hand, the synthesis of platform parameters is based on the software-level timing details and does not consider control-theoretic metrics such as stability and performance. An incorrect timing characterization of control properties can result in an inconsistency between models and their implementation. For example, the performance requirement can enforce a strict constraint on application latency which if not correctly modeled may not be satisfied by the implementation.

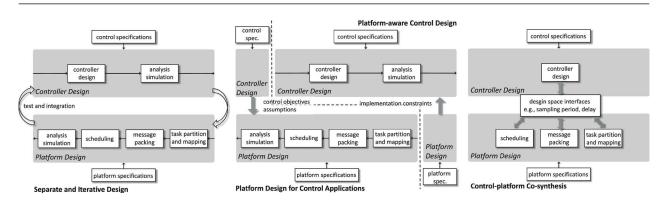

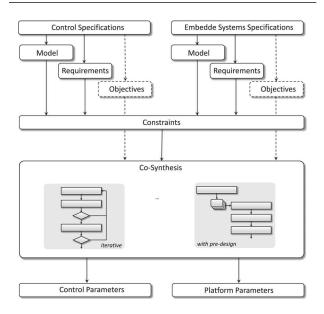

Hence, it is difficult to design a safe CPS with such separation of concerns due to the associated semantic gap. We define an embedded control system to be safe when the corresponding software implementation meets the control requirements on stability and performance even in the worst case. Now, to ensure safety with separation of concerns, the whole process is usually carried out in an iterative manner as shown in Fig. 1. Here, the controllers and platform parameters are separately designed followed by integration and testing. In case a test shows that the requirements are not met, the steps are reiterated, possibly without

any systematic feedback for improvement. This paradigm relies strongly on the prior experience of engineers and can be error prone. With the increasing size and complexity of modern embedded systems, this design paradigm is not sustainable. This leads to the need for new design approaches that can guarantee safety in a correct-by-design manner and do not depend on testing.

### C. Bridging the Semantic Gap: CPS-Oriented Approaches

Due to the strong dependency between controller and platform design, both the control and the embedded systems design methods are gradually moving toward a CPSoriented design paradigm. Control theorists have started accounting for implementation details and constraints of the underlying embedded platform and are integrating them in the mathematical models for controller design. For example, properties such as the sensing-to-actuation delay, input and output jitter, packet drops, deadline misses, and finite precision arithmetic are modeled and considered in the controller design phase, so that the designed controllers are platform aware. In the same vein, embedded systems engineers have also begun to study properties of control loops and are considering them in platform design methods. These properties include stability, performance, and robustness of control loops, and steady state and transient state characteristics. Consequently, the platform parameters such as task and message schedules can be tuned according to control objectives, rather than solely on intermediate objectives such as deadlines and latencies.

These CPS-oriented approaches, as shown in Fig. 1, consider realistic details of one side while designing parameters on the other side. In particular, they mathematically translate control properties into timing characteristics and *vice versa* to bridge the semantic gap. However, these methods consider the parameters on one side as given and design the parameters on the other side accordingly, and thus, it provides limited opportunity for optimization. They may result in a suboptimal design configuration with respect to

Fig. 1. Different design paradigms.

control performance, resource efficiency, or both. In order to achieve higher design efficiency, it is important to design the control and the platform parameters together from joint specifications in a holistic optimization framework.

### D. Ensuring Safety and Optimality: Cosynthesis of CPSs

In many cost-sensitive domains (such as automotive) it is not only necessary to ensure safety but it is equally desirable to achieve design optimality. In this survey, we emphasize on the importance of control-platform cosynthesis for CPSs toward ensuring safety and design optimality.

In recent years, a group of cosynthesis approaches have emerged that consider the design of control and platform parameters as a holistic optimization as shown in Fig. 1. Generally, the cosynthesis problem is formulated as a nonconvex optimization problem and is solved using a customized design space exploration (DSE) technique. The solutions provide both sets of parameters which are tuned according to certain objectives such as control performance and resource efficiency. Therefore, the synthesized parameters represent optimal design configurations. Moreover, the control model semantics are fully preserved in the implementation. This is because the controllers are designed according to the detailed constraints from the platform side and the platform parameters are synthesized considering stability and performance requirements from the control side. The synthesized parameters are, therefore, correct by design and ensure safety.

However, there exist considerable challenges that need to be addressed, if these approaches are to be applied to industrial scale applications. These challenges include handling complexity and scalability, developing closed-form optimization frameworks, inadequate toolchains, and certification issues. Moreover, existing approaches do not consider several aspects of platform architectures, e.g., memory hierarchy, heterogeneous networks, or multicore processors, all of which are common in modern embedded systems. Furthermore, they also do not take into account complex characteristics of control systems, e.g., time variance, nonlinearity, or input saturation. Hence, control-platform cosynthesis is a promising research direction with a number of open problems.

#### E. Paper Organization

We start with traditional problems and approaches that exist in both control theory and the embedded systems literature. In Section II, the basics of control theory are reviewed, particularly, system models, stability theorems, performance metrics, and common controller design methods. Subsequently, Section III provides the background on embedded systems design such as platform models, implementation constraints, and platform design and analysis

techniques. Section IV first states the safety challenges associated with the design and implementation of CPSs. Subsequently, it reviews works on 1) how control engineers can consider implementation details in controller design; and 2) how embedded systems engineer can take into account the control properties in platform design. This is followed by Section V, where recent works on control-platform cosynthesis are studied and the general design flow for such approaches is outlined. Finally, possible future research directions and challenges are discussed in Section VI, followed by some concluding remarks (Section VII).

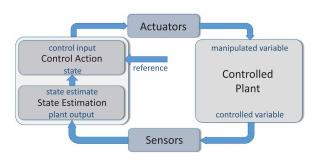

#### II. FEEDBACK CONTROL SYSTEMS

Control systems form an integral part of technological advancement in almost any field. They help in ensuring the intended functionality from machines and make processes run by adapting to the environment variables. More often than not, they are based on the theory of feedback as depicted in Fig. 2. In feedback control systems, a control action is decided based on the values of plant state variables and the reference that the plant must follow. In practice, some variables of the plant may not be measurable, and therefore, the corresponding values are estimated using an estimator. The basic idea is to mitigate the error between the plant output and the reference and therefore manipulate the plant to satisfy requirements on stability and performance. In this section, we will discuss how such a system can be mathematically modeled and the requirements can be mathematically expressed. Subsequently, we will also mention some techniques to design feedback controllers such that specified requirements are satisfied.

#### A. System Model

In this paper, we predominantly survey works which consider linear and time-invariant (LTI) systems with single-input-single-output (SISO). The mathematical model of the dynamic behavior of such a system in continuous time can be represented as

$$\dot{x}(t) = Ax(t) + Bu(t)$$

$$y(t) = Cx(t)$$

(1)

Fig. 2. Block diagram of feedback control systems.

where vector  $x(t) \in \mathbb{R}^{n \times 1}$  represents the states of the system, and y(t) and u(t) represent, respectively, the system output and the control input at instant t. Here, the constant matrices  $A \in \mathbb{R}^{n \times n}$ ,  $B \in \mathbb{R}^{n \times 1}$ , and  $C \in \mathbb{R}^{1 \times n}$  are, respectively, the state, input, and output matrices.

Considering that the controller is implemented on an embedded platform, the control input is applied to the plant only at discrete instants  $k \in \mathbb{Z}^*$ . Let us assume that the time interval between two consecutive instants is a constant h and the control input to the plant is held constant until the next input is generated and applied, i.e., u(t) = u(kh), where  $kh \le t < (k+1)h$ . This is equivalent to a system with a sample and hold device connected at the input, and correspondingly, h is the sampling period of the system. Consequently, the equivalent state—space model of the sampled data (discrete-time) system is given by

$$x[k+1] = \phi x[k] + \Gamma u[k]$$

$$y[k] = Cx[k]$$

(2)

where the discrete-time state and input matrices  $\phi$  and  $\Gamma$  can be derived from the continuous time matrices for a given sampling period h as follows:

$$\phi = e^{Ah}, \quad \Gamma = \int_0^h (e^{At} dt) \cdot B$$

(3)

#### **B.** Notions of Stability

For a given system model, the goal of a control engineer is to design a control law that computes the control input such that the closed-loop system satisfies specific requirements. One of the most important requirements is the stability of control loops. There are different notions of stability in control theory among which two important definitions are given here. To define stability, we must first introduce the equilibrium state  $x_e$  of a system as the state to which it converges in the absence of a control input (an unforced system), i.e., u[k] = 0.

1) Stability in the sense of Lyapunov: The equilibrium state  $x_e$  is stable in the sense of Lyapunov when the following holds:

$$\forall \underset{\epsilon \in \mathbb{R}^{+}}{\exists} (||x[0] - x_{e}|| \leq \delta) \Rightarrow (||x[k] - x_{e}|| < \epsilon). \quad (4)$$

$$\downarrow k \in \mathbb{Z}^{*}$$

$$\downarrow (0)$$

Moreover,  $x_e$  is uniformly stable in the sense of Lyapunov when (4) holds and  $\delta$  is independent of the initial state.

2) Asymptotic stability:  $x_e$  is said to be asymptotically stable when besides being stable in the sense of Lyapunov the following expression holds:

$$\forall \exists_{x[0]} \exists_{\delta \in \mathbb{R}^+} (||x[0] - x_e|| \le \delta) \Rightarrow \lim_{k \to \infty} ||x[k] - x_e|| = 0. \quad (5)$$

Moreover,  $x_e$  is uniformly asymptotically stable when  $\delta$  is independent of the initial state in (5).  $x_e$  is globally

asymptotically stable if, despite  $\delta$  being arbitrarily large, the states finally converge to  $x_e$ .

#### C. Stability Analysis

For an unforced LTI system given by  $x[k+1] = \phi x[k]$  with initial state x[0], we can write as follows:

$$x[k+1] = \phi^{k+1}x[0]. \tag{6}$$

Without loss of generality, we can assume  $x_e = 0$  from the definition of equilibrium state. Therefore, for a system to be asymptotically stable for a finite nonzero initial state, the following must hold:

$$\lim_{k \to \infty} ||\phi^k|| = 0. \tag{7}$$

This is only possible when the eigenvalues of  $\phi$ , i.e.,  $\lambda_i$  s,  $\forall i = 1, 2, ..., n$ , satisfy the following:

$$|\lambda_i| < 1. \tag{8}$$

Here,  $\lambda_i$ s also represent system poles. Thus, for a system to be asymptotically stable all the poles must lie within the unit circle in a complex *z*-plane.

However, this constraint is only valid for LTI systems and a more powerful technique for analyzing stability of both linear and nonlinear systems is the second method of Lyapunov. According to this theorem [5], for a discrete-time unforced system x[k+1] = f(x[k]), where f(0) = 0, if a scalar continuous function V(x[k]) exists such that

i)

$$V(0) = 0$$

ii)  $\bigvee_{x \neq 0} V(x) > 0$  iii)  $\lim_{\|x\| \to \infty} V(x) \to \infty$

iv)  $\bigvee_{x \neq 0} \Delta V(x[k]) = V(x[k+1]) - V(x[k]) < 0$  (9)

then  $x_e = 0$  is globally asymptotically stable and V(x) is a Lyapunov function.

This method can be simplified and applied for LTI systems  $x[k+1] = \phi x[k]$ , where  $x_e$  is asymptotically stable if and only if, for a given positive–definite real symmetric matrix Q, there exists a positive–definite real symmetric matrix P such that the following criterion is satisfied:

$$\phi' P \phi - P = -Q. \tag{10}$$

Here, V(x[k]) = x'[k]Qx[k] is a Lyapunov function for the system and  $\Delta V(x[k]) = -x'[k]Px[k]$  [5].

#### D. Quality of Control

Although stability is an essential requirement, different control applications may also need to satisfy different performance criteria. The performance of a controller is often measured by a metric that quantifies the quality of control (QoC). Thus, the goal of a control engineer is to design a

controller which not only meets the performance criteria but preferably has a higher QoC.

The performance measures of a control loop have evolved over the years from common metrics such as peak overshoot, rise time, settling time, and steady state error, to more complex cost functions and gains. Here, we will not discuss the common metrics, however, readers are encouraged to read [5] for more insights. We list some important performance measures as follows.

1) Integral cost function: System response to a given reference r[k] can be analyzed for QoC based on several cost functions [6]. These cost functions consider tracking error e[k] = r[k] - y[k] and are given as follows:

$$\sum_{0}^{\infty} e[k]^2 \quad \sum_{0}^{\infty} |e[k]| \quad \sum_{0}^{\infty} k|e[k]|. \tag{11}$$

Moreover, a more general quadratic cost which is a function of system states and control input can be considered. This is represented for finite and infinite horizon, respectively, as

$$J = \frac{1}{2} [x[N]' Sx[N] + \sum_{0}^{N-1} (x[k]' Qx[k] + 2x[k]' Mu[k] + u[k]' Ru[k])]$$

(12)

and

$$J = \frac{1}{2} \sum_{k=0}^{\infty} (x[k]'Qx[k] + 2x[k]'Mu[k] + u[k]'Ru[k]).$$

(13)

Here, *S* and *Q* are symmetric positive–semidefinite matrices while *R* is a symmetric positive–definite matrix. *S*, *Q*, *R*, and *M* are coefficient matrices used for weighing different terms according to their dimensions or importance.

2)  $\mathcal{L}_2$  gain: For a given input, let  $\eta_u$  be defined as the ratio of the output and the input energy of a system and can be represented as follows:

$$\gamma_u = \frac{||y||_2}{||u||_2} = \left(\frac{\int_0^\infty ||y(t)||^2 dt}{\int_0^\infty ||u(t)||^2 dt}\right)^{1/2}.$$

(14)

Now, the  $\mathcal{L}_2$  gain  $\gamma_{\mathcal{L}_2}$  of a system is defined as follows [7]:

$$\gamma_{\mathcal{L}_2} = \sup_{u \in \mathcal{L}_2} \gamma_u. \tag{15}$$

By the second method of Lyapunov, it can be stated that a system is asymptotically stable when  $\mathcal{L}_2$  is finite. Moreover, the  $\mathcal{L}_2$  gain gives an idea of the robustness of a system and, therefore, is used as a performance measure.

Given a performance measure, the task of a control engineer is to design a controller that optimizes the system performance. However, this is not trivial as the design parameters, e.g., control gains, affect the control performance in a nonlinear and complex manner. Therefore, engineers may often need to do extensive analysis. For example, using root locus diagram, an engineer can analyze how control gains affect the system poles which in turn influence the transient response of the system. However, with performance metrics,

such as gains and cost functions, control theorists have come up with novel design approaches for optimal control.

#### E. Control Design

Over the years, different techniques to design controllers that stabilize the system and also optimize QoC have been developed. A naive approach could use simulation where a controller is assumed to be given and then the closed-loop system is simulated for a certain given initial condition and reference. In case design requirements are not satisfied, then a different controller is assumed heuristically and the process is repeated until a suitable controller is found. However, this iterative approach is time consuming and cumbersome, and therefore, systematic mathematical approaches are more common. Here, we discuss three such approaches.

1) Pole placement technique: This design approach [8] exploits the fact that an LTI system is asymptotically stable when (8) holds. Now, for a state-feedback controller to reject impulse disturbance, control law can be written as

$$u[k] = -Kx[k] \tag{16}$$

where vector  $K \in \mathbb{R}^{1 \times n}$  represents feedback control gains. Therefore, (2) can be reformulated as

$$x[k+1] = (\phi - \Gamma K)x[k]. \tag{17}$$

Now, a system represented by (17) will be asymptotically stable when the eigenvalues of  $\phi_{cl} = \phi - \Gamma K$  satisfy (8). The pole placement approach exploits this, and therefore, the control gains can be calculated for single-input systems using the Ackermann's formula

$$K = [0 \quad 0 \quad \dots \quad 1] \gamma_c^{-1} H(\phi)$$

(18)

where  $\gamma_c$  is the controllability matrix

$$\gamma_c = \begin{bmatrix} \Gamma & \phi \Gamma & \phi^2 \Gamma & \cdots & \phi^{(n-1)} \Gamma \end{bmatrix}. \tag{19}$$

For the eigenvalues  $\lambda_i$ s,  $H(\phi)$  is given by the following:

$$H(\phi) = (\phi - \lambda_1 \mathbf{I})(\phi - \lambda_2 \mathbf{I}) \cdots (\phi - \lambda_n \mathbf{I}). \tag{20}$$

However, this approach is only applicable when the system is controllable, i.e.,  $\gamma_c$  has full rank. Otherwise, not all the eigenvalues or poles can be freely selected. This means that the system is stabilizable only when the closed-loop poles which cannot be manipulated are already stable.

2) Linear quadratic regulator (LQR): This design approach [5] not only designs an asymptotically stable system but also considers optimization of the quadratic cost given by (12) and (13). Now, the linear feedback control for the finite horizon case is given by

$$u[k] = -K[k]x[k] \tag{21}$$

where control gains  $K[\cdot]$  can be different for different samples. Here, the gains can be calculated from a dynamic Riccati equation by iterating backwards [8]. For an infinite horizon, the gain is constant for all samples and is obtained by solving the algebraic Riccati equation until a stationary solution is reached [8].

3) Linear quadratic Gaussian control (LQG): The limitation when using LQR is that all the states must be measurable to compute the control input. However, the measured states may not be accurate as there may be some noise in the measurement or noise inherent in the system. The noisy system model can be represented as

$$x[k+1] = \phi x[k] + \Gamma u[k] + w[k]$$

$$y[k] = Cx[k] + v[k]$$

(22)

where for the sake of simplicity w and v can be assumed to be white noise. Now, to design an optimum controller which minimizes the loss function given by (13), we can apply the separation theorem [8]. Here, we first estimate the states  $\hat{x}[k]$  and then apply the LQR technique to design the controller using the estimated states  $\hat{x}[k]$ . In this approach, the state estimation is realized using Kalman filtering [8], where the objective is to minimize the variance of the estimation error. This can be realized, for example, using a one-step-ahead predictor, where the next states are predicted based on the current state estimations, control input, and system output which can be expressed as follows:

$$\hat{x}[k+1|k] = \phi \hat{x}[k|k-1] + \Gamma u[k] + K[k](y[k] - C\hat{x}[k|k-1]). (23)$$

To minimize error variance, the Kalman gains  $K[\cdot]$  can be calculated by solving the parametric optimization problem based on the predictor model in (23) [8]. This can be represented as

$$\hat{x}[k|k] = \hat{x}[k|k-1] + K_f[k](y[k] - C\hat{x}[k|k-1])$$

$$\hat{v}[k|k] = K_v[k](y[k] - C\hat{x}[k|k-1])$$

$$\hat{x}[k+1|k] = \phi\hat{x}[k|k] + \Gamma u[k] + \hat{v}[k|k].$$

(24)

The Kalman filter gains, i.e.,  $K_f[\cdot]$  and  $K_v[\cdot]$ , can be obtained by solving a Ricatti equation [8].

These mathematical design approaches guarantee stability and, in particular cases, optimal performance. However, they do not consider the controller implementation on the embedded platform which may influence the system model and therefore nullify the safety guarantees. Moreover, for an embedded implementation, the resources needed by a control software must also be an important consideration in the controller design stage. Consequently, the aforementioned techniques must be extended to consider resource constraints and specific characteristics of the implementation platform.

#### F. Nonlinear Dynamical Systems

Although we do not consider it in this survey, an important research direction in the field of control theory is the stabilization and control of nonlinear dynamical systems. In the context of CPSs, most of the works consider linear models of the physical system as commonly found in electrical circuits, mechanical systems, and chemical processes. However, new models found in the domains of avionics, autonomous vehicles, and power grid are inherently nonlinear due to their complex interaction with the environment. Naturally, the problems of stability analysis and controller design for nonlinear systems considering the details of platform implementation have become relevant. Toward this, there have been works focusing on NCSs, where the control loop is closed over a communication network. Correspondingly, several network-specific characteristics such as time-varying network delays, packet drops, and quantization influence control properties.

Besides techniques derived from traditional nonlinear control theory, two important approaches toward solving problems of nonlinear NCS are: 1) fuzzy-model-based control; and 2) formal synthesis of hybrid control systems. There has been significant progress on these two approaches where several implementation aspects have also been considered. However, most of these works assume very abstract platform models. They do not really derive the abstraction from real platform parameters such as network schedules, communication protocols, size of gateway buffers, or switch latencies. Hence, an integrated approach that closely binds controller design with platform parameter estimation is still missing. We discuss this topic again in Section VI-B. However, for more detailed survey on fuzzy-model-based nonlinear control and formal synthesis of hybrid control systems the readers are referred to [9] and [10]-[12], respectively.

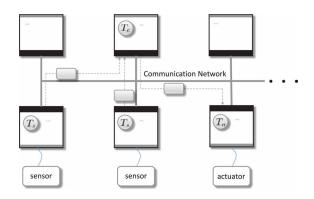

### III. EMBEDDED PLATFORMS: DESIGN AND ANALYSIS

Embedded systems are widely used in various domains such as automotive, consumer electronics, healthcare, avionics, and industrial automation. In each of these domains, an underlying electrical/electronic (E/E) platform is required, which provides computation and communication services to the functional software. A typical hardware architecture for such a platform consists of one or more processing units. Fig. 3 shows an example of a distributed embedded platform. Here, each processing unit has one or more processing cores, memory systems and input/output (I/O) ports. In the case of distributed architectures, multiple processing units are connected by one or more communication bus systems. Data can be transmitted between processing units as messages packed into frames over the bus. In a large-scale system, heterogeneous bus protocols are used where communication gateways can connect different bus clusters. Toward implementing software applications on

Fig. 3. A distributed embedded platform.

such platforms, in this section, we will first describe the implementation model and associated implementation constraints, followed by common implementation techniques.

#### A. Platform Implementation Model

A software application can be implemented as several pieces of software codes called tasks. These tasks can be data dependent in the sense that the output of one task is considered as an input to another task. Two data-dependent tasks can be mapped on different processors due to reasons such as spatial distribution of sensors and actuators. In such a case, the data between them are transmitted over a communication bus via messages packed into frames. Thus, an application can be modeled as a directed task graph. Here, each vertex is a task and directed connecting lines represent data transmitted from source to target tasks. Subsequently, we will explain the timing models of tasks and data frames.

1) Task Model: Typically, in an embedded application, a task is executed multiple times triggered either a) periodically via time interrupts, i.e., in a time-triggered fashion; or b) aperiodically via events, i.e., in an event-triggered fashion. Moreover, when multiple tasks are mapped on a common processor, certain arbitration mechanisms are necessary. This is achieved by the operating system (OS), which is a software that schedules the tasks and allocates resources. Depending on the requirements of the applications, different scheduling schemes can be employed by the OS. Common scheduling schemes include time-triggered (TT) scheme (e.g., eCos), fixed-priority preemptive (FPP) scheme (e.g., OSEK), and dynamic scheduling schemes such as earliest deadline first (EDF).

In TT static scheduling, processor time allocation is preconfigured, i.e., it is known when a task will be executed by the processor. In this scheme, a periodic task is characterized by a tuple  $T_i \sim \{p_i, o_i, e_i\}$ , where  $p_i, o_i$ , and  $e_i$  represent, respectively, the period, the schedule offset, and the execution time. Since the execution time of a task is usually not deterministic, the worst case execution time (WCET) is used to represent the task schedule.

In contrast, in an FPP scheme, it is not known when a task will allocate a processing resource. Instead, it is decided at runtime by the OS according to the preset priority of the task. Without loss of generality, a periodic task can be characterized by the tuple  $T_i \sim \{p_i, a_i, \pi_i, e_i\}$ , which represent, respectively, the period, release time, priority, and execution time. The release time determines when a task instance is dispatched to be scheduled by the OS. Here, tasks are executed according to their priorities. If a task is currently running and a higher priority task arrives, the current task will be preempted. It will be resumed again when all task instances with higher priority are processed completely.

In the case of EDF scheduling scheme, the priorities of the tasks are not assigned offline, but are determined online according to remaining time to the deadline. Here, a task is represented as  $T_i \sim \{d_i, e_i\}$ .  $d_i$  is the relative deadline which is the time that the processor has to finish executing the task after the task release.

Each of these scheduling schemes has its own advantage such as timing predictability, resource efficiency, and implementation overhead, and the appropriate scheme can be chosen depending on requirements.

2) Frame Model: Each message frame may be packed with one or more data items and is transmitted over the bus according to different communication protocols. For example, message transmission may be achieved through a wireless medium (e.g., Zigbee, Bluetooth, and WLAN) or a wired medium (e.g., CAN, FlexRay, and Ethernet). Typical bus protocols include a) CAN, FlexRay, LIN, Ethernet, and MOST in the automotive domain; b) ProfiNet, Profibus, and EtherCAT in industrial automation; and c) AFDX in the avionics domain. Different communication protocols implement different scheduling schemes, which is determined by the media-access control (MAC) layer. For example, the CAN bus employs a fixed-priority nonpreemptive (FPNP) scheme, Ethernet implements collision sense multiple access/collision detection (CSMA/CD), EtherCAT implements polling, while FlexRay implements a hybrid scheme composed of a time-division multiple-access (TDMA)based static segment and a flexible TDMA (FTDMA)-based dynamic segment.

For different protocols, frame timing models can be represented differently. For example, a CAN frame schedule can be represented as  $fr_i \sim \{p_i, a_i, \pi_i, c_i\}$  where  $c_i$  represents the frame transmission time over the bus. However, a static FlexRay or TDMA frame timing is expressed as a tuple  $fr_i \sim \{s_i, b_i, r_i\}$  where  $s_i$  is the slot id in which the frame is transmitted,  $b_i$  is the TDMA cycle when the frame is sent for the first time, and  $r_i$  represents the number of bus cycles after which the frame is sent again.

#### **B.** Implementation Constraints

The platform implementation often consists of determining various parameters associated with the processors and

the communication network. In processors, these parameters include task partition and mapping, and scheduling parameters such as the static task schedule or priorities. On the communication side, various parameters of the network need to be determined. The exact parameters depend on the protocol and the implementation. For example, the design parameters for CAN are the priorities of the messages. For FlexRay, this would include the whole configuration of the FlexRay communication cycle, i.e., the frame packing and frame-to-slot assignment.

Different constraints need to be considered when determining the platform parameters. These constraints may be enforced by the platform or are derived from application requirements. We discuss some important constraints as follows.

1) Processor Utilization: This is defined as the fraction of computation time for which the processor may be busy in the worst case for a given task mapping. Let us denote the WCET and the period of a task  $T_i$  as  $e_i$  and  $p_i$ , respectively. Now, for a set of tasks  $\mathcal{T}(P_i)$  mapped onto a processor  $P_i$ , the processor utilization  $U(P_i)$  is given by the following expression:

$$U(P_i) = \sum_{T_i \in \mathcal{T}(P_i)} \frac{e_i}{p_i}.$$

(25)

The processor utilization usually must be lower than a certain value, beyond which, the tasks are no longer schedulable (in practical cases, the value is much smaller the 100% for reliability reasons).

2) Bus Load: Bus load depends on the communication protocol used by the bus. For example, let us consider the FlexRay static segment. It is partitioned into N slots of equal length. In FlexRay, time is organized as an infinite repetition of 64 bus cycles. Here, the total number of slots in 64 cycles is 64N. If  $\Theta$  is the set of frames mapped onto a FlexRay bus, then the constraint on bus load  $U_{FR}$  is derived as follows:

$$U_{FR} = \sum_{fr \in \Theta} \frac{64}{r_i} \le 64N.$$

(26)

However, for bus systems, besides the reliability, the extensibility (i.e., provision for mapping future messages) of the design also needs to be considered [13]. This is because industrial systems often follow an iterative design paradigm where the previous version is first inherited and then extended with new features. Now, if a bus is too highly loaded, it reduces the possibility of adding future messages.

3) Application-Level Constraints: In addition to the constraints imposed by limited platform resources, application requirements must also be considered in the design. Consider an application represented by a chain of tasks and messages as  $a_i \sim T_1 \rightarrow fr_1 \rightarrow T_2 \rightarrow fr_2 \rightarrow \cdots \rightarrow T_n$ . In such an application, the tasks and messages must be scheduled in a way such that the task dependency constraints are satisfied. For example,  $T_1$  must finish before  $fr_1$  is sent and  $T_2$  must

start only when  $fr_1$  has arrived. Furthermore, there may be constraints on application latency, i.e., the time between the start of  $T_1$  and the completion of  $T_n$ . This constraint is imposed on hard real-time distributed applications and correspondingly they must satisfy strict deadlines. Even the sensing-to-actuation delay of a control application can be expressed as a latency requirement.

4) Task- and Frame-Level Constraints: Application-level requirements are typically translated to deadlines of tasks and messages. Deadline constraints specify when the execution of a task (or transmission of a message) needs to be finished after its release. In this regard, the response time of a task (or a frame) is defined as the time elapsed between the release of the task (or frame) and the completion of task execution (or frame transmission). Response time not only depends on the code size in a task or the data size in a frame but also on the scheduling scheme on the processor and the bus. Denoting the response time of a task or a frame as  $R_i$ , and the deadline it must satisfy as  $d_i$ , then the deadline constraint is given as follows:

$$R_i \le d_i. \tag{27}$$

In addition, for shared resources, tasks and messages must also satisfy constraints related to resource conflicts. Such a constraint typically states that no two tasks or messages must be allocated to the same resource at the same time.

#### C. Platform Analysis

Platform analysis verifies if the system design meets the specified constraints and timing requirements. The analysis techniques depend on the implemented scheduling strategy on a platform. Considering the wide spectrum of scheduling algorithms available in different domains, we would not go into the details of any specific analysis.

Early works on this topic have focused on providing schedulability tests and worst case response time (WCRT) analysis. For example, Liu and Layland [14] and Xu and Parnas [15] address the problem of schedulability tests for rate-monotonic, deadline-monotonic, and EDF scheduling schemes. Bril [16] and Bril  $et\ al.$  [17] propose the response time analysis for tasks. For example, in FPP scheduling, the WCRT of a task  $t_i$  can be computed using an iterative algorithm based on the following recurrence relation [16]

$$R_i = e_i + \sum_{\prod_{i > \prod_i} \prod_j \left[ \frac{R_i}{p_j} \right]} e_j. \tag{28}$$

In the case of communication networks, Davis *et al.* [18] address the problem of timing analysis of the CAN bus and Pop *et al.* [19] and Zeng *et al.* [20] consider the FlexRay bus.

Much effort has also been spent in deriving formal methods for compositional timing analysis. In this context, network calculus [21], real-time calculus [22], [23], and

SymTA/S approach [24] have been developed. These methods have been applied to processor scheduling [23] and to analyze communication networks such as FlexRay [25] and switched Ethernet topologies [26]–[28]. In addition, the problem of combined task and message timing analysis has also been addressed [29]–[31]. In this case, timing properties are considered at the application level.

#### D. Platform Design

Another important research focus in embedded systems is the design of platform parameters according to the constraints and timing requirements. Here, the design is mostly aimed at task mapping, frame packing, and task and message scheduling [32]-[35]. Several works also consider the combined synthesis of task and message schedules from the application-level timing requirements such as latencies and response times [36]-[39]. In these approaches, usually a constraint programming (CP) problem is formulated and solved with integer linear programming (ILP) or satisfiability modulo theories (SMTs) solvers, heuristics or metaheuristics methods. These approaches can usually guarantee that the requirements are met and further tune the parameters according to certain optimization objective(s). When multiple conflicting objectives are considered, a Pareto front can be generated or a DSE algorithm [40] can be applied to help the designer analyze different tradeoffs.

#### E. Hardware/Software Codesign

One additional direction of embedded systems design that has received attention in the past decade is hardware/ software (HW/SW) codesign. Traditionally for electronic systems, the hardware is designed first, followed by the design of the software. HW/SW codesign approaches design both hardware and software components concurrently, thus enabling faster time to market and achieving more efficient design. However, these approaches only consider cost, performance, reliability, and power consumption as design objectives. They do not consider high-level control requirements such as stability and performance, when the software in question implements a feedback control loop. This survey focuses on the design of embedded control system from a CPS perspective and we refer the reader to [41] for a survey on HW/SW codesign. It may be noted that many optimization techniques used in HW/SW codesign, when appropriately adapted, can be utilized in the design of embedded control systems.

## IV. CPS-ORIENTED APPROACHES TO EMBEDDED CONTROL SYSTEMS DESIGN

Our setup consists of a group of physical plants controlled by software running on a single processor or on a network of processors. In this section, we first study the interplay between the control system and the embedded platform using a motivational example. In doing so we point out the associated safety challenges. We will also discuss how the control and the embedded systems communities have attempted to address these challenges from their own perspectives.

A motivational example: As an example, we have considered a second-order system with the following system matrices:

$$A = \begin{bmatrix} -0.2 & 0.667 \\ -10 & -100 \end{bmatrix} \quad B = \begin{bmatrix} 0 \\ 100 \end{bmatrix} \quad C = \begin{bmatrix} 1 & 0 \end{bmatrix}.$$

(29)

For a sampling period of h = 0.02 s, the discrete-time matrices can be calculated using (3) as follows:

$$\phi = \begin{bmatrix} 0.9953 & 0.0057 \\ -0.0862 & 0.1349 \end{bmatrix} \quad \Gamma = \begin{bmatrix} 0.0076 \\ 0.8643 \end{bmatrix}. \tag{30}$$

Let us consider the control law as u[k] = -Kx[k] + Fr where K and F are the feedback and the feedforward gains and r is the reference. Without loss of generality, we can assume r=0 and use the pole placement technique described in Section II-E to calculate the feedback gain. Feedforward gain can be calculated using the final value theorem, i.e.,  $\lim_{t\to\infty} y(t) = r$ , and is given by the following relation:

$$F = \frac{1}{C(\mathbf{I} - \varphi + \Gamma K)^{-1} \Gamma}.$$

(31)

For both the closed-loop poles at 0.9, *K* and *F* can be calculated as follows:

$$K = [0.7032 -0.7811]$$

$F = 0.8689.$  (32)

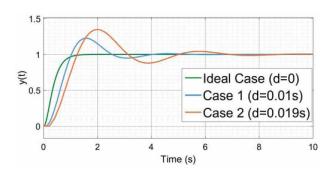

Using these values, we have simulated the closed-loop system for unit step reference and plotted the output in Fig. 4.

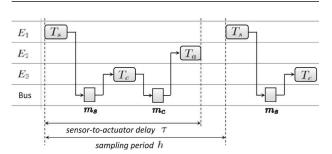

Next, let us assume that the control code is implemented as three tasks  $T_s$ ,  $T_c$ , and  $T_a$  in temporal order where the WCETs of the tasks are 1ms, 3ms, and 1ms, respectively. These tasks are mapped on different ECUs, each with a TT scheduler. The data between  $T_s$  and  $T_c$  are transmitted as a message  $m_s$  and the data between  $T_c$  and  $T_a$  are transmitted

Fig. 4. Closed-loop simulation curves with delay.

as another message  $m_c$ . The messages are transmitted over CAN. Now, let us consider two scenarios where the WCRTs of  $m_s$  and  $m_c$  are, respectively, calculated as follows: Case 1) 2ms and 3ms; and Case 2) 6ms and 8ms. We can schedule the tasks in a way such that all task dependency constraints are satisfied and the end-to-end delay is minimum. Now, for both cases, we have simulated the closed-loop system for a unit step reference signal. We have modeled the tasks  $T_s$  and  $T_g$  and the messages  $m_s$  and  $m_g$ as delay blocks of appropriate values, while  $T_c$  executes the control law followed by a delay of 3ms. The response curves for both the cases are shown in Fig. 4. It may be noted that the overshoot and the settling time have increased from the ideal case with no delay. Thus, we may say that the performance has deteriorated, and more importantly, it does not match the expected values that were obtained at the model level. This performance degradation can be attributed to the delays introduced in the loop which will be studied later in this section. Fig. 5 shows the interplay between the control models and the platform implementation, i.e., how the task and message schedules affect the sampling period and the closed-loop delay of the control loop. Thus, controller design without considering the timing properties of the platform implementation is unreliable and in the worst case may even result in an unstable system in spite of the modellevel controller being stable.

As mentioned earlier, safety properties of embedded control systems is usually captured in terms of stability and performance guarantees. We can observe in the above example that when the controller is designed separately from the embedded platform and is oblivious to the implementation details, no such guarantees at the implementation level are possible. In practice, costly testing and integration efforts are necessary to obtain an acceptable implementation by iteratively changing the controller model and the platform parameters.

To address this issue, new controller design techniques that account for platform characteristics and resource constraints are discussed in Section IV-A. These techniques analyze properties of the platform architecture and incorporate them into the controller model, and then determine the appropriate parameters corresponding to this augmented model in order to ensure stability and performance.

Fig. 5. Task/message schedules in a controller implementation.

Similarly, on the embedded systems side, new techniques for platform design have been proposed that take into account the particular requirements of embedded control systems; we discuss them in Section IV-B. Here, a given control system is first analyzed to determine timing constraints that satisfy stability and performance requirements. Subsequently, platform parameters are synthesized taking these timing constraints into account. Both the aforementioned design paradigms have made significant progress in bridging the semantic gap between controller design and its implementation that is illustrated in the results shown in Fig. 4.

#### A. Platform-Aware Controller Design

The control theory community has looked into new controller design methods that take into account the implementation platform characteristics. Here we review some of the important work in this direction.

1) Sensing-to-Actuation Delay: The discrete-time control system model described in Section II-A assumes that there is a negligible time delay between sensing and actuation. This implies that the computation of control input takes negligible time. This is an idealistic assumption as embedded processors often have limited computation bandwidth and take nonnegligible time for computation. Moreover, sensors and actuators are often spatially distributed and the control loop may involve some communication over a shared network, which may introduce additional delays. Assuming a sensing-to-actuation delay (or closed-loop delay) of  $\tau$  where  $0 < \tau \le h$ , u(t) = u[k-1] for  $kh \le t < kh + \tau$ , and u(t) = u[k]for  $kh + \tau \le t < (k+1)h$ . Consequently, the discrete-time state-space model for the delayed system [8] becomes the following:

$$x[k+1] = \phi x[k] + \Gamma_0 u[k] + \Gamma_1 u[k-1]$$

$$y[k] = Cx[k].$$

(33)

Here,  $\Gamma_0$  and  $\Gamma_1$  for a sampling period h and a delay  $\tau$  are given as follows:

$$\Gamma_0 = \int_0^{h-\tau} (e^{At} dt) \cdot B \qquad \Gamma_1 = \int_{h-\tau}^h (e^{At} dt) \cdot B. \qquad (34)$$

Consequently, we can consider an augmented state vector as  $z[k] = [x[k] \quad u[k-1]]'$ , for which the state–space model can be written as

$$z[k+1] = \phi_z z[k] + \Gamma_z u[k]$$

$$y[k] = C_z z[k]$$

(35)

where  $\phi_z$ ,  $\Gamma_z$ , and  $C_z$  are as follows:

$$\phi_z = \begin{bmatrix} \phi & \Gamma_1 \\ 0 & 0 \end{bmatrix} \quad \Gamma_z = \begin{bmatrix} \Gamma_0 \\ \mathbf{I} \end{bmatrix} \quad C_z = [C \quad 0].$$

(36)

This model is identical to the ideal discrete time model given by (2). Therefore, now the standard controller design methodology that was explained in Section II can be applied. This system model has been used in [42] and [43].

2) Input and Output Jitter: The closed-loop delay introduced in a controller implementation may not be a constant value and instead be time varying, resulting in output jitter. Similarly, a control task may not be sampled at regular intervals, thereby resulting in input jitter. This nondeterminism in timing may be induced by event-triggered preemptive scheduling of shared resources, or by asynchronous clocks in a distributed system, among other reasons. Moreover, this nondeterministic behavior may cause system instability or inadequate QoC. Thus, it is important to analyze the influence of input and output jitter on stability and performance of a control loop.

Toward this, there have been some work in NCSs that considers stochastic or approximate analysis of system stability [44]-[48]. However, Cervin [49] has proposed an analysis of system stability and worst case performance considering both input and output jitter. In [49], the assumption is that only the worst case delay, i.e., input and output jitter, is given without any information on the statistical distribution. Cervin introduces a novel technique to transform the closed-loop system model by adding two error paths corresponding to input and output jitter. In one error path, the influence of output jitter is modeled as an error in the actuation signal. In the second error path, the influence of input jitter is modeled as an error in the measurement. Subsequently, the stability and the performance of the transformed closed-loop system are analyzed in the frequency domain. This analysis can be very useful in practice to ensure safety of an implementation in the presence of jitter without extensive simulations or testing.

3) Processor Architecture and Operating Systems: Design of embedded systems often starts with the selection of architectural components, e.g., processors, buses, and the OS along with its scheduling policy and parameters. However, at this stage, the designer only has a very rough idea of the applications. Therefore, the choice of processor architecture and OS is almost oblivious of the applications that will run on the processor. However, there are certain OS features that invalidate the assumptions made in the controller design if not taken into account. For example, an OS such as ERCOSek, running on a processor may offer only a preconfigured set of sampling periods. Controllers implemented on such a processor must be implemented according to a sampling period selected from this set. The straightforward scheme is to find the largest sampling period  $H_i$  from the preconfigured set  $\mathcal{H} = \{H_1, H_2, \dots, H_k\}$  for which a controller can be designed satisfying the requirements. However, this might result in

using an unnecessarily high sampling rate, and thereby overloading the processor.

To address this issue, Goswami *et al.* [50] have proposed to design controllers with nonuniform sampling. The idea is to choose a sampling order  $\prod h_i = h_1 \rightarrow h_2 \rightarrow \cdots \rightarrow h_n \rightarrow repeat$ . Here,  $h_i \in \mathcal{H}$  and  $h_{avg} = \frac{1}{n} \sum_{i=1}^n h_i$ . Then, the controller is designed such that the obtained performance  $J(\prod h_i)$  for the assumed sampling order satisfies the requirement  $\overline{J}$  while  $h_{avg} > H_j$ . Higher  $h_{avg}$  implies savings in computation resource. Goswami *et al.* [50] also suggest a design technique for such a multirate controller. The controller is designed for the average sampling period  $h_{avg}$  using the pole placement technique described in Section II-E. The closed-loop system  $\phi_{cl}(\prod h_i) = \phi_{cl}(h_1) \phi_{cl}(h_2) \cdots \phi_{cl}(h_n)$  can be analyzed for stability and performance using standard techniques.

A similar approach is also valid for multicore architectures where a TDMA-based execution policy is employed to eliminate interapplication interference or to offer compositionality. In such an architecture [51], processor time is partitioned into slots where each slot is dedicated to an application. Correspondingly, several instances of a controller may run in its TDMA slot thus resulting in a shorter sampling period. However, the last instance may either have to wait for the next dedicated slot to finish or the time gap between the last instance of the current slot and the first instance on the next slot is much larger. In both cases, the controller implementation naturally resembles a multirate case with only two sampling periods. Valencia et al. [42] have studied such an implementation of controllers in multicore architectures. The sampling order for a given TDMA policy is derived. Subsequently, a linear matrix inequality (LMI)-based approach is proposed to design the controller. Here, the two sampling periods result in two different subsystems and the overall system switches between the two. Therefore, it is suggested to design the controller corresponding to the shorter sampling period (the dominant one) using pole-placement technique. The stability of the overall switching system can be ensured by finding a common P such that (10) holds for both subsystems.

4) Deadline Misses, Packet Drops, and Fault Tolerance: A controller can be designed assuming a closed-loop delay and sampling period as discussed in Section IV-A1. Subsequently, in the schedulability analysis, the controller is treated as a hard real-time application where the delay is considered as a deadline and the sampling period as the dispatch period. A system is schedulable if all the WCRTs satisfy the deadline constraints. This schedulability test is conservative in nature because it relies on a critical instant (i.e., all the controllers are contending to run at the same time,) and on WCET estimates of the controller tasks (which are pessimistic in nature). Since the worst

case occurs rarely, this results in a poor resource utilization. Similarly, in NCSs, there is a hard constraint on in-time packet delivery. However, there may be momentary faults in the network which can corrupt the data. In highly constrained networks, there may be some packet losses as well.

In domains such as automotive, efficient utilization of resources is of utmost importance in order to minimize cost. Hence, the goal is to map as many applications as possible on a given embedded platform (single processor or network of processors). Moreover, for control applications, deadline or in-time packet delivery is not an accurate reflection of stability and QoC and designs driven by them might be overly conservative. This is because of the inherent robustness of control loops, which allows for certain deadline misses. However, quantifying such deadline miss patterns is not straightforward.

Recently, a number of works have addressed this issue [52]–[59]. Most of them consider a switched system model to represent a control-loop with deadline misses or packet drops [52]–[54], [58], [59]. There can be several ways in which deadline misses or packet drops can be modeled, i.e., 1) as an open-loop system, i.e., u[k] = 0; 2) as the last control input being used, i.e., u[k] = u[k-1]; or 3) as two consecutive misses, i.e., u[k] = u[k-2]. The probability of a deadline miss can either be stochastic or guided by the (m, k)-firm rule (i.e., only m out of k times deadlines can be missed).

It is natural to study the impact of deadline misses on the performance of control loops. Towards this, Geelen et al. [53] and Antunes and Heemels [54] have considered stochastic systems with packet drops or deadline misses. For a given ideal input signal (i.e., without any misses), mean and variance of the output signal are calculated in time domain and in frequency domain. Furthermore, van Horssen et al. [52] have studied performance degradation for switched systems with (m, k)-firm data losses, where a system switches between closed-loop and open-loop subsystems. Here, van Horssen et al. have represented the system with deadline misses as an automaton for which a stable controller can be designed using an LMI-based approach. Correspondingly, the loss in performance can be calculated by comparing the quadratic costs corresponding to the stable controller and the ideal (without misses) LQR controller. Van Horssen et al. [52] have further proposed that the performance can be improved at the cost of online computation by deadline-miss-aware controller updates.

In the same vein, Majumdar et al. [59] have considered  $\mathcal{L}_{\infty}$ -to-RMS gain as the performance measure, and, for a given successful packet transmission rate, an upper bound on  $\mathcal{L}_{\infty}$ -to-RMS gain is derived. This gain measure of a discrete-time LTI system with input disturbance  $\omega$  and

$||\omega||_{\infty} = \sup_{k \ge 0} ||\omega[k]||_2$  is given by the following expression and indicates how a system reacts to disturbance:

$$\sup_{\substack{\|\omega\|_{\infty}\neq0,x[0]=0}} \frac{\left(\lim\sup_{N\to\infty}\frac{1}{N}\sum_{j=0}^{N}y'[j]y[j]\right)^{\frac{1}{2}}}{\|\omega\|_{\infty}}.$$

(37)

The lower the gain value is, the smaller is the effect of disturbance and the better is the robustness. Considering this, an expression for the minimum successful transmission rate  $r_{\min}$  is derived for which the system is stable. Later, Saha et al. [58] have derived that the successful transmission rate at which the performance is optimal is either the minimum possible rate  $r_{\min}$  (constrained by stability) or the maximum possible rate  $r_{\max}$  (constrained by network availability).

In addition, Goswami *et al.* [57] have studied a restriction on deadline misses over a finite horizon (k samples) and proposed an exponential stability criterion in terms of allowable deadline misses. This criterion forces a bound on the rate at which the system must approach the equilibrium state from a given initial state which is mathematically given by [60]

$$||x[k] - x_e|| \le c_1 + c_2 \beta^k ||x[0]|| \tag{38}$$

where  $c_1 \ge 0$ ,  $c_2 > 0$ , and  $0 < \beta < 1$ . Furthermore, Goswami *et al.* [57] have considered a performance measure tuple  $\{S, \chi\}$  as follows:

$$S \ge \frac{||x[k+\chi] - x_e||}{||x[k]||} \times 100\%. \tag{39}$$

This implies that  $\chi$  samples after the disturbance has arrived, at least (100-S)% of the disturbance is rejected. Subsequently, the number of samples  $\kappa_s$  that can be missed out of  $\chi$  samples can be calculated to meet the performance requirement given by S.

5) Finite Precision Arithmetic: Traditionally, controllers are designed by solving a set of differential equations in a way that stability and performance requirements are met. At the model level, no assumptions on the arithmetic precision of computations are made. However, for an embedded implementation, the control law is calculated by a processor that allows only fixed precision arithmetic operations. As a result, safety and performance guarantees are no longer valid due to quantization errors. Moreover, it may so happen that the system constantly oscillates around the equilibrium state.

To address this, there has been work on quantizationerror-aware verification of control software [61]–[64]. The goal is to verify that the final implementation results in a practically stable system, i.e., the final state of the system is within a bounded region of the equilibrium state.

Furthermore, Majumdar et al. [65] have proposed to synthesize controllers by cooptimizing the LQR cost

function and the quantization error, thereby constructing a Pareto front of the two objectives. The proposed approach can be partitioned into two stages. In the first stage, an upper bound on the quantization error in the computation of control law is calculated. For a given implementation and the bounds on plant states, the range of each controller variable is analyzed and the bitwidths allocated accordingly. For given bitwidth allocations, the maximum quantization error in an arithmetic operations is calculated. Subsequently, since the computation of the control law involves multiple arithmetic operations, the quantization error accumulates accordingly. In addition to the quantization error in the computation, the approach also considers quantization error in measurement, for which the bound will simply depend on the allocated bitwidths. The errors are modeled as disturbance in the observer dynamics and the feedback gain codes. Subsequently, in the second stage, a multiobjective optimization problem is formulated and solved using particle swarm optimization (PSO) [66]. The objectives considered are LQR-LQG quadratic cost function [see (13)] and  $\mathcal{L}_2$  induced gains from input disturbance to output [see (14) and (15)], where the input disturbances are the two quantization errors. Finally, the PSO algorithm generates several Pareto points that depict the tradeoff between performance and quantization error.

#### B. Controller-Aware Platform Design

As discussed in Section III, traditional approaches of platform design are based on timing requirements, which might be overly conservative. In the context of CPS, a more appropriate approach is to consider the control properties of the system at the platform design stage. These control properties include stability, QoC, and robustness, among others. This design approach will ensure either 1) optimal QoC of the overall system for a given platform resource; or 2) minimize resource usage while satisfying all performance and stability constraints. Toward this, in this section, we will discuss some of the platform design approaches that have been proposed in the literature.

1) Stability- and Performance-Aware Platform Design: In Section IV-A, we have discussed several platform characteristics that may influence the stability and performance of control systems if not considered at the controller design stage. Most of these platform characteristics are configurable, subject to certain constraints. For example, the sensing-to-actuation delay and jitter can be manipulated by changing the schedule parameters to the extent that the overall system still remains feasible. Now, given a set of controllers, how to determine platform parameters considering their influence on stability and performance is an important research problem.

Toward this, Mancuso *et al.* [67] have addressed the problem of calculating the priorities and periods of the control tasks. It is assumed that several control loops run on a

given platform with FPP scheduling. An optimization problem is also formulated with the objective of maximizing the overall QoC. Here, the control performance of each loop is measured by the LQR cost function approximated as a linear function of sampling period and delay. Solving the optimization problem is difficult due to the nonlinear dependency of the WCRT of a task on priority assignment. Consequently, a branch and bound technique is proposed to solve the problem. Furthermore, Aminifar et al. [68] have proposed a scalable algorithm to determine the priorities and periods of control tasks taking into account both worst-case delay and jitter. However, only the stability of control loops is considered instead of optimizing the overall QoC. The impact of delay and jitter on stability of a control loop is studied using the Jitter Margin Toolbox [69]. Finally, a stability condition in terms of delay and jitter is derived as a linear inequality.

In the same vein, Aminifar et al. [70], [71] have studied server-based scheduling of control tasks. The server-based scheduling of real-time tasks is introduced to achieve isolation, i.e., misbehavior in one task will not effect the others. In [70] and [71], Aminifar et al. have defined periodic server as a tuple of budget Q, period P, and deadline D. It is assumed that each server is assigned to only one control task. The server ensures that Q amount of processor time is allocated to the assigned task in each period *P* before the deadline *D*. Here, the constraint is that the resource reserved by a server must be greater than or equal to the resource requirement of the assigned task. A task runs only when its dedicated server allocate processor time to it. Now, given the period and the best and the worst case execution times of a control task, it is possible to derive the best and worst case response time of the task. Corresponding to these values, nominal delay and jitter can be calculated which can be subsequently analyzed to determine the stability of the system. It may be noted here that in this server-based approach, each task can be analyzed independent of other tasks running on the same processor. The idea is to calculate the parameters of each server taking into consideration the stability and the worst case performance of the assigned control loop. Although, the server-based approach is pessimistic in nature, it offers compositionality and isolation, which are important aspects to guarantee safety in control systems (i.e., model-level guarantees are preserved in an implementation).

2) Robust-Control-Aware Platform Design and Verification: In Section IV-A4, we have mentioned that any control-loop has some inherent robustness. Hence, occasional deadline misses or packet drops may not make the system unstable or violate its performance requirements. We have also mentioned previous work that derived the minimum rate of ideal closed-loop action [(m,k)-firmness] necessary to ensure stability and performance of the system. Given these rates for multiple control loops, the task of an embedded systems engineer is to implement the corresponding controllers on an embedded platform such that these constraints/rates are satisfied.

In this context, Majumdar  $et\ al.\ [59]$  have proposed a static scheduling algorithm that satisfies the (m,k)-firmness of all the controllers and at the same time tries to maximize the overall QoC of the system. The algorithm solves a multiobjective optimization problem where (m,k)-firmness is treated as one of the constraints. The optimization objectives are the QoCs of all the control systems. Next, the multiobjective optimization problem is transformed into a single-objective problem by a weighted combination of the QoCs. Here, the weights are assigned in a way such that the control loop, which is the most sensitive to the rate of packet drops, has maximum influence on the objective. Consequently, the solution to the problem will be an undominated one in the multiobjective space.

Another body of research that studies the impact of missed control action on stability and performance is platform-aware formal verification of control software [55], [56], [72], [73]. Here, an embedded platform architecture is represented as a network of time-stamped event count automata (TS-ECA) where each message is stamped with a time as it moves from one buffer to another. Moreover, the (m,k)-firm rule can be formulated as a linear temporal logic (LTL) formula where all possible combinations of allowed misses can be represented. Subsequently, the network of TS-ECAs are model checked to verify satisfiability of the LTL formula. Thus, a control software can be formally verified using model checking to ensure that all the control applications satisfy the constraints on their deadline misses.

Furthermore, Behrouzian [73] has proposed an analytical technique to verify (m, k)-firmness. The authors assume that the control tasks are running on a processor according to a TDMA scheme where each application is assigned a dedicated slot to execute. For such an architecture, given a sampling period between the best and worst case response time, the proposed technique can calculate an upper bound on the percentage of dropped samples. The estimation is based on an analysis of a finite regular window with the assumption that tasks arrive periodically. This technique is faster than timed-automata-based approaches that were proposed earlier.

3) Application-Criticality-Aware Platform Design: Mixed criticality systems are becoming increasingly more common; here, applications of different criticality share the same resource. These applications have different requirements, e.g., hard real-time applications have strict timing requirements, while control applications have stability and performance requirements. Thus, techniques discussed in Section IV-B1 are not applicable in a straightforward manner for platform design in such cases.

Toward this, Wu *et al*. [74] have considered control and noncontrol tasks running on a processor with EDF scheduling strategy. Upper and lower bounds are assumed on sampling periods and relative deadlines of all applications. Here, the bounds for control applications are derived from stability

and performance requirements. Subsequently, an optimization problem is formulated and solved where the variables are the periods and deadlines of all tasks. The objective is to maximize the overall QoC of the system while satisfying the deadline constraints of noncontrol tasks. The QoC metric of each control loop is the loss in LQR cost due to sampling period and output jitter.