This is a repository copy of *Field plate designs in all-GaN cascode heterojunction field-effect transistors*.

White Rose Research Online URL for this paper: https://eprints.whiterose.ac.uk/143101/

Version: Accepted Version

# Article:

Jiang, S. orcid.org/0000-0002-3687-1882, Lee, K.B. orcid.org/0000-0002-5374-2767, Zaidi, Z.H. et al. (3 more authors) (2019) Field plate designs in all-GaN cascode heterojunction field-effect transistors. IEEE Transactions on Electron Devices, 66 (4). pp. 1688-1693. ISSN 0018-9383

https://doi.org/10.1109/ted.2019.2897602

© 2019 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other users, including reprinting/ republishing this material for advertising or promotional purposes, creating new collective works for resale or redistribution to servers or lists, or reuse of any copyrighted components of this work in other works. Reproduced in accordance with the publisher's self-archiving policy.

# Reuse

Items deposited in White Rose Research Online are protected by copyright, with all rights reserved unless indicated otherwise. They may be downloaded and/or printed for private study, or other acts as permitted by national copyright laws. The publisher or other rights holders may allow further reproduction and re-use of the full text version. This is indicated by the licence information on the White Rose Research Online record for the item.

# Takedown

If you consider content in White Rose Research Online to be in breach of UK law, please notify us by emailing eprints@whiterose.ac.uk including the URL of the record and the reason for the withdrawal request.

# Field Plate Designs in All-GaN Cascode Heterojunction Field Effect Transistors

Sheng Jiang, Kean Boon Lee, Zaffar H. Zaidi, Michael J. Uren, Martin Kuball and Peter A. Houston

Abstract— Different source field plate connections are compared for the all-GaN integrated cascode device to address the capacitance matching and turn-off controllability issues reported in the conventional GaN plus Si cascode. Experimental results suggest that the cascode device with a field plate connected to the source terminal can significantly suppress the off-state internode voltage, leading to minimized capacitive energy loss and reduced overvoltage stress at the internode. This is attributed to the reduced ratio of the drain-source capacitance of the depletion mode cascode part to the total capacitance at the cascode internode. An additional field plate on the E-mode cascode part is proposed to further suppress the off-state internode voltage and benefit the device. Cascode devices with the source field plate connecting to the enhancement mode gate have an improved switching controllability via gate resistance during turn-off and hence enhanced dv/dt immunity in the drain loop.

*Index Terms*—Power electronics, Semiconductor devices, Semiconductor switches, Semiconductor heterojunctions.

#### I. INTRODUCTION

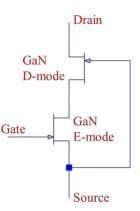

Cascode devices, with the advantage of a reduced Miller effect, are strong candidates for high voltage, high frequency applications [1-3]. An all-GaN integrated cascode configuration, shown in Fig. 1, was demonstrated with a superior hard switching performance at 200 V compared to the equivalent standalone GaN heterojunction field effect transistor (HFET) [1]. However, further optimization of the integrated cascode is still required to address several known issues from experience in the GaN plus Si hybrid cascode device [4-6], which also apply to the integrated cascode structure. First, the mismatch in intrinsic capacitances between the depletion mode (D-mode) and the enhancement mode (E-mode) devices can lead to an increased off-state voltage at the internode of the cascode configuration [4-5]. This overstress can drive the E-mode Si device into avalanche during the turn-off transient, causing additional losses for the hybrid cascode [4-5]. Although the avalanche effect does not apply to the all-GaN integrated cascode device, a large off-state internode voltage can increase both the breakdown voltage requirement of the E-mode part and capacitive energy loss at the internode. Second, the turn-off speed of the cascode devices is reported to be uncontrollable via the gate resistance  $(R_g)$  as a result of the reduced Miller effect, which can cause an issue when control over the

Fig. 1. Circuit diagram of an all-GaN integrated cascode configuration.

switching speed is required to suppress the ringing effect [8-9].

Adding an external capacitor between the drain and source of the Si device was proposed in [4] and [5] to match the capacitance in the hybrid cascode device and prevent the Si device from being driven into avalanche during turn-off. Likewise, external capacitors and resistors were proposed to improve the turn-off controllability issue for the cascode devices [8-9]. However, the use of external components has several drawbacks which includes additional parasitic inductance, and presents challenges in the device packaging [8-9].

Field plates (FPs) are commonly employed in GaN HFETs to moderate the surface electric field and hence lead to an increase in breakdown voltage and suppression of surface-related dynamic Ron [10-11]. In addition, FP incorporation may also lead to a change in intrinsic capacitances of the transistor depending on the connection method of the field plates [12-13]. Compared to standalone GaN HFETs, the FP of the D-mode part in the cascode device has the flexibility to connect to different locations without the worry of the Miller-effect, as the effective Miller capacitance is shifted to the gate-drain capacitance of the E-mode part  $(C_{GD-E})$  [1]. In addition, different connections redistribute the FP induced capacitances and thus affect the switching behaviour of the cascode device. The connection of the FP is hence important to realize the full optimization of the integrated cascode device [1] but has not previously been discussed. In this study, we examine five different FP connections and compare their influence on the switching performance of the integrated cascode device. We shed new light on the effect of the different FP configurations and demonstrate how both capacitance matching and switching controllability issues can be addressed without increasing the parasitics.

S. Jiang, K. B. Lee, Z. H. Zaidi, and P. A. Houston are with the Department of Electronic and Electrical Engineering, University of Sheffield, Mappin Street, S1 3JD Sheffield, United Kingdom (e-mail: sheng.jiang@sheffield.ac.uk; kboon.lee@sheffield.ac.uk; zaffar.zaidi@sheffield.ac.uk; p.a.houston@sheffield.ac.uk).

M. Uren and M. Kuball are with the University of Bristol, H H Wills Physics Department, Tyndall Avenue, Bristol, BS8 1TL, United Kingdom (e-mail: michael.uren@bristol.ac.uk; Martin.Kuball@bristol.ac.uk)

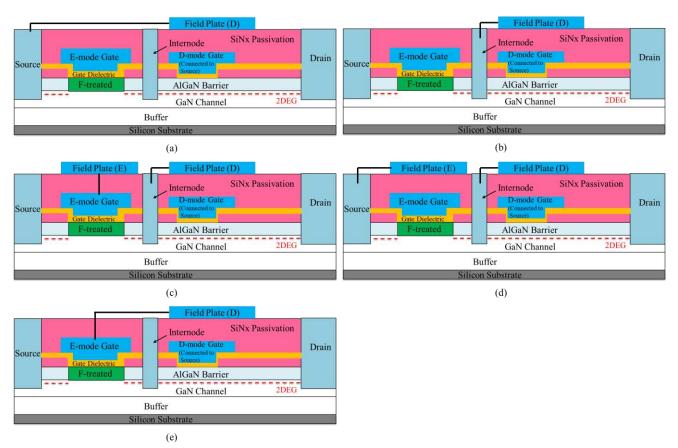

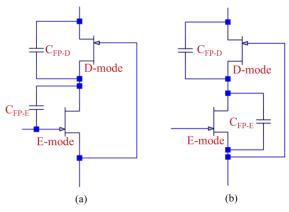

Fig. 2. A schematic diagram of all-GaN integrated cascode devices with five different field plate structures. (a) Device A with D-mode FP connected to the source of the cascode (b) Device B with D-mode FP connected to the internode pad (c) Device C with D-mode FP connected to the internode pad and E-mode FP connected to the E-mode gate (d) Device D with D-mode FP connected to the internode pad and E-mode FP connected to the E-mode gate.

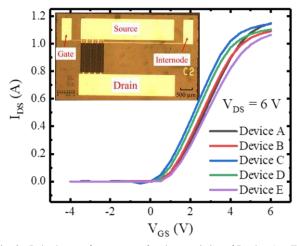

Fig. 3. Pulsed on-wafer gate transfer characteristics of Device A – E at  $V_{DS} = 6$  V, quiescent  $V_{DS} / V_{GS} = 0 / 0$  V, pulse width of 10 ms and pulse period of 100 ms. An optical image of the monolithically integrated AlGaN/GaN HFET cascode configuration with an additional internode contact pad (inset).

#### II. FP DESIGN AND DC CHARACTERISTICS

Fig. 2 shows the all-GaN integrated cascode device with five different FP structures (Device A - E) All devices were fabricated on a GaN-on-Si substrate with the standard GaN HFET fabrication procedure described in [1]. The E-mode operation was achieved by CHF<sub>3</sub> plasma-treatment in a reactive ion etch (RIE) system plus a nominally 20 nm thick  $SiN_x$  gate dielectric. The D-mode gate also features a

| TABLE I                             |  |  |  |  |

|-------------------------------------|--|--|--|--|

| SUMMARY OF DIFFERENT FP CONNECTIONS |  |  |  |  |

| SUMMARY OF DIFFERENT FP CONNECTIONS |                                                                                                     |  |  |  |  |

|-------------------------------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|

| E-mode FP                           | D-mode FP                                                                                           |  |  |  |  |

| connection                          | connection                                                                                          |  |  |  |  |

| No FP                               | Source of cascode                                                                                   |  |  |  |  |

| No FP                               | Internode                                                                                           |  |  |  |  |

| Gate of E-mode part                 | Internode                                                                                           |  |  |  |  |

| Source of cascode                   | Internode                                                                                           |  |  |  |  |

| No FP                               | Gate of E-mode part                                                                                 |  |  |  |  |

|                                     | <i>E-mode FP</i><br><i>connection</i><br>No FP<br>No FP<br>Gate of E-mode part<br>Source of cascode |  |  |  |  |

metal-insulator-semiconductor (MIS) structure with 20 nm thick SiN<sub>x</sub> to improve the current handling of the integrated cascode device [1]. 70 nm SiN<sub>x</sub> was deposited using plasma enhanced chemical vapour deposition as the first passivation to support the T-shape gate wings and 200 nm SiN<sub>x</sub> was used as the second passivation for the FPs. The E-mode parts for all devices have a gate width of 8 mm, gate length of 1.5  $\mu$ m, source-drain separation of 6.5  $\mu$ m and gate wing of 1  $\mu$ m. While the D-mode parts have the same dimensions, except for a larger source-drain separation of 16  $\mu$ m to withstand the high voltage. The device parts are separated by an internode ohmic contact of 10 $\mu$ m length. All devices have a FP extension (*L<sub>FP</sub>*) of 2  $\mu$ m on the D-mode part.

Device A (Fig. 2(a)) and B (Fig. 2(b)) have a D-mode FP only connected to the source of the cascode and the internode pad, respectively. Device C (Fig. 2(c)) and D (Fig. 2(d)) are based on Device B with the same D-mode FP connection, except for an additional FP with extension of 1  $\mu$ m on their E-mode parts connected to the E-mode gate and to the source of cascode, respectively. Device E (Fig. 2(e)) only has a FP on its D-mode part which is connected to the E-mode gate. Table. 1 shows the summary of different FP connections for

(b)

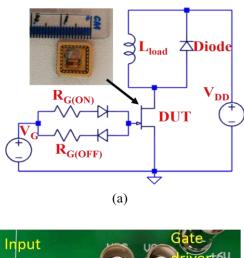

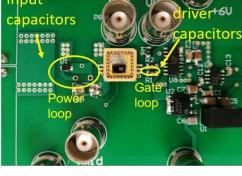

Fig. 4. (a) Circuit diagram of double pulse tester for switching speed measurement. (b) Circuit implementation.

all fabricated devices.

An additional pad to access the internode of the cascode was added to all multi-finger cascode devices, enabling the potential at the internode to be monitored during the switching measurements (inset in Fig. 3). Devices exhibit similar DC characteristic as shown in the on-wafer gate transfer measurement results in Fig. 3. Output currents > 1 A and threshold voltages of the E-mode part ( $V_{th-E}$ ) > 0 V were

achieved for all 8 mm cascode devices. Devices are capable of 200 V operation with drain leakage current below 10  $\mu$ A/mm.

## III. EXPERIMENTAL SETUP

The switching performance was measured by an inductive load double pulse tester (DPT) as described in [1]. Fig 4(a) illustrates the circuit diagram of the DPT. Device under test (DUT) was wire-bonded onto commercial air cavity quad flat no lead (QFN) packages (shown in the inset of Fig. 4(a)) to minimize the parasitics [14]. A commercial gate driver IX2204 was used to drive the devices from  $V_{GS} = -2$  V to +6 V. A Coilcraft 470 µH shielded power inductor was used as load inductor and an Onsemi 200 V Schottky diode MBR2H200SF was used as the freewheeling diode. Fig. 4(b) shows the picture of the assembled DPT. The input and gate driver capacitors are placed close to the DUT to minimize the loop distance and thus the parasitic inductance, as highlighted in Fig. 4(b). To prevent the noise from the load coupling into the gate loop, the power and gate loop were also separated, achieved by a source-sense connection in the device packaging. The gate voltage  $(V_{GS})$ , internode voltage  $(V_{INT})$ and drain voltage  $(V_{DS})$  were measured using a digital oscilloscope. The drain current  $(I_{DS})$  was monitored by a high bandwidth current sensing resistor T&M SDN-414-10 connected to the source of the DUT.

## IV. RESULTS

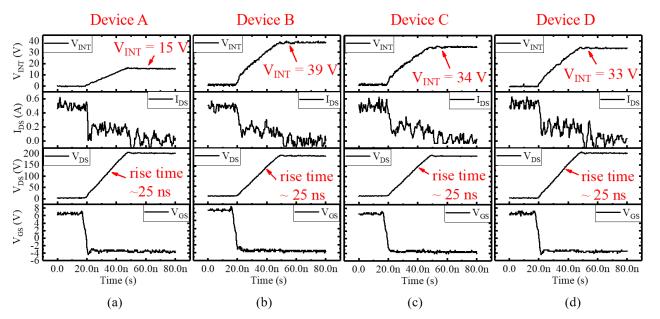

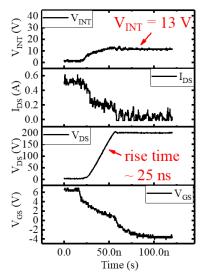

Fig. 5 shows the turn-off switching waveforms of  $V_{GS}$ ,  $V_{DS}$ ,  $I_{DS}$  and  $V_{INT}$  for Device A, B, C and D at a drain voltage of 200 V, load current of 0.5 A and gate resistance of 10 ohm. Voltage rise times around 25 ns are observed for all devices, extracted from 10 % to 90 % of the operating voltage ( $V_{DD}$ ).  $I_{DS}$  was measured from the voltage across a 0.1 ohm current sensing resistor resulting in less than 50 mV output. While the roughness of  $I_{DS}$  is in tens of mV and is consistent with that of  $V_{GS}$ ,  $V_{DS}$ , and  $V_{INT}$ , the waveforms of  $I_{DS}$  appear to be noisier. This is due to the waveforms of  $I_{DS}$  being displayed at 50 mV/div, compared to 10 V/div, 50 V/div and 20 V/div used for  $V_{GS}$ ,  $V_{DS}$ , and  $V_{INT}$ . In addition, the step down in  $I_{DS}$  is due to the charging of the parallel capacitance in the

Fig. 5. Switching waveforms of V<sub>GS</sub>, V<sub>DS</sub>, I<sub>DS</sub> and V<sub>INT</sub> for (a) Device A (b) Device B (c) Device C and (d) Device D, captured at 10 V/div, 50 V/div, 50 mV/div and 20 V/div, respectively.

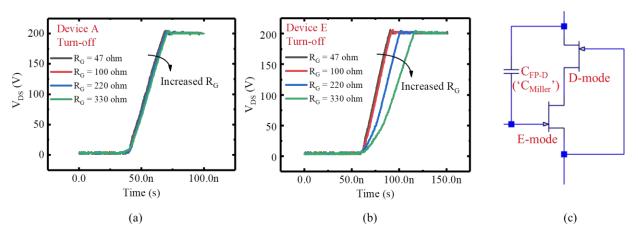

Fig. 6. Turn-off switching waveforms of  $V_{DS}$  for (a) Device A and (b) Device E. (c) The equivalent circuit diagram of  $C_{FP-D}$  for Device E.

Fig. 7. Equivalent circuit diagrams showing FP induced capacitance in (a) Device A and (b) Device B.

freewheeling diode in the DPT circuit, which will not influence the comparison. On the other hand,  $V_{INT}$  varies in the devices with different FP connections. Device A exhibits  $V_{INT}$  of 15 V which is the lowest among all devices, while Device B shows the highest (39 V), as shown in Fig. 5(a) and (b), respectively. Device C and D with an additional FP on the E-mode part compared to Device B, exhibit similar  $V_{INT}$ close to 33 V, as shown in Fig. 5(c) and (d).

The turn-off controllability via  $R_G$  was compared between Device A and Device E with the same switching conditions of  $V_{DS} = 200$  V and  $I_{DS} = 0.5$  A.  $R_G$  was varied from 47 ohm to 330 ohm, in order to observe the change in the voltage rise time between the two devices. Fig. 6 (a) and (b) shows the switching waveform of  $V_{DS}$  during turn-off for the Device A and Device E, respectively. Device A, as a typical cascode device, shows little control over the voltage rise time with different  $R_G$ , consistent with other reported literature on hybrid cascode devices [8-9]. On the other hand, Device E exhibits 100 % increase (25 ns) in the switching time when  $R_G$  is varied from 47 ohm to 330 ohm. This is due to the additional 'Miller capacitance'  $(C_{Miller})$  induced by the FP connected to the gate of the E-mode part in Device E, as shown in the equivalent circuit in Fig. 6 (c). As a result, the turn-off switching controllability is improved and can be further enhanced by increasing the FP induced capacitance  $(C_{FP-D}).$

## V. DISCUSSION

Despite the different FP connections, Device A - D exhibit similar drain voltage rise times, which is expected as the

TABLE II

COMPARISON OF CALCULATED AND MEASURED OFF-STATE  $V_{INT}$  FOR

| DEVICES A - D |          |                  |               |            |  |

|---------------|----------|------------------|---------------|------------|--|

|               |          | V <sub>INT</sub> | $V_{INT}$     | $V_{INT}$  |  |

|               |          | (Calculated      | (Calculated   | (Measured) |  |

|               |          | based on device  | based on CV   |            |  |

|               |          | geometries)      | measurements) |            |  |

|               | Device A | 17 V             | 16 V          | 15 V       |  |

|               | Device B | 45 V             | 39 V          | 39 V       |  |

|               | Device C | 42 V             | 33 V          | 34 V       |  |

|               | Device D | 42 V             | 33 V          | 33 V       |  |

drain voltage transition during turn-off for the cascode device is mainly determined by the load current and the output capacitance ( $C_{GD-D} + C_{DS-D}$ ) of the D-mode part [1]. The capacitances at the internode ( $C_{INT}$ ), which are dependent on FP connection, include the gate-source capacitance of the D-mode part ( $C_{GS-D}$ ), the gate-drain capacitance of the E-mode ( $C_{GD-E}$ ) and the drain-source capacitance of the E-mode part ( $C_{DS-E}$ ). They have little effect on the drain voltage rise time and can be ignored, provided  $C_{INT}$  is significantly larger than  $C_{DS-D}$  [15]. Meanwhile, the connection difference in the D-mode FP of Device A and Device B (C and D) does not change the geometric capacitance induced by the FP and thus is expected to yield similar switching speed as observed.

FP connections in Device A and B lead to a different ratio of  $C_{GD-D}$  and  $C_{DS-D}$  and hence affect the off-state  $V_{INT}$  as observed. To explore the reason for this, the principle of the increase in  $V_{INT}$  in the turn-off transition is now explained. During turn-off, assuming the gate resistance is small enough to prevent the Miller effect from controlling the switching speed of the E-mode part, the E-mode channel is pinched off first, after the gate-source voltage of the E-mode part ( $V_{GS-E}$ ) drops below  $V_{th-E}$ .  $V_{INT}$  then starts to increase and pinches off the D-mode channel when it reaches the D-mode threshold voltage  $(V_{th-D})$ . After both D-mode and E-mode channels are pinched off, the entire load current shifts into  $C_{GD-D}$  and  $C_{DS-D}$ to drive the drain voltage rise. The displacement current in  $C_{DS-D}$  flows into the internode and charges up  $C_{INT}$  [7]. The charging of C<sub>INT</sub> completes at the same time as the drain voltage transition and is assisted by the displacement current in  $C_{DS-D}$ .

Assuming negligible off-state leakage in both D-mode and E-mode parts [6-7] and the gate drive current is sufficiently high that the Miller effect does not control the switching speed, the off-state  $V_{INT}$  can be approximated by the voltage division of  $C_{DS-D}$  and  $C_{INT}$ , and is given by

Fig. 8. Switching waveforms of  $V_{GS}$ ,  $V_{DS}$ ,  $I_{DS}$  and  $V_{INT}$  for for Device B with  $R_{G(OFF)} = 330$  ohm, captured at 10 V/div, 50 V/div, 50 mV/div and 20 V/div, respectively.

$$V_{INT} \approx \frac{C_{DS-D} * V_{DD}}{C_{DS-D} + C_{INT}} - V_{th-D}$$

This approximate expression shows that the capacitance matching in a cascode device depends on the ratio of  $C_{DS-D}$  to  $(C_{DS-D} + C_{INT})$ . By estimating the capacitance based on the device geometries and capacitance-voltage (CV) measurements on standalone devices with equivalent FP geometries,  $V_{INT}$  can be calculated using (1) and shows reasonable agreement with the experimental results for all devices (Table. 2).

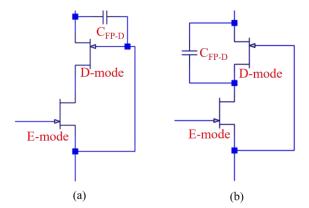

Device B with the FP connected to the internode pad, increases  $C_{DS-D}$ , as illustrated in the equivalent circuit diagram in Fig. 7(a). In contrast, Device A has a reduced  $C_{DS-D}$  but larger  $C_{GD-D}$  due to the connection of the FP to the source of the cascode, as shown in Fig. 7(b). According to (1), a larger  $C_{DS-D}$  can result in an increased ratio of  $C_{DS-D}$  to  $(C_{DS-D} + C_{INT})$ , and thus an increased  $V_{INT}$  and capacitive energy loss  $(1/2 * C_{INT} * V_{INT}^2)$ , as observed from Device B. Note that  $C_{GD-D}$  is connected to ground and does not contribute to the Miller effect in the cascode. Therefore, there is no penalty to increase  $C_{GD-D}$  for a reduced  $C_{DS-D}$ , as observed in Device A.

Note that both Device A and B show off-state  $V_{INT}$  larger than  $-V_{th-D}$  (-6 V), and it will become larger at higher voltage operation (ie >200 V) as indicated in (1). One route to reduce the internode voltage during turn-off, is to increase the turn-off gate resistance  $(R_{G(OFF)})$  as shown in Fig. 8, which shows the switching waveforms of device B under the same conditions except for a larger gate resistance of 330 ohm. Similar drain voltage rise time (25 ns) is observed compared to the results with  $R_{G(OFF)} = 10$  ohm. This is also observed for Device A as shown in Fig. 6(a), and is because  $R_{G(OFF)}$  mainly controls the switching speed of the E-mode part in the cascode [8-9]. On the other hand,  $V_{INT}$  was reduced to 13 V. Note that (1) is no longer valid for the estimation of  $V_{INT}$ , since the equivalent circuit cannot be regarded as a voltage divider consisting of two series connected capacitors ( $C_{DS-D}$ and  $C_{INT}$ ). When  $R_{G(OFF)}$  is large enough to cause the Miller-effect to control the switching speed of the E-mode part, the displacement current cannot be fully consumed by charging C<sub>INT</sub>, which is limited by the insufficient gate

Fig. 9. Equivalent circuit diagrams showing FP induced capacitance in (a) Device C and (b) Device D.

driving current through  $C_{GD-E}$ . As a result, part of the displacement current flows through the E-mode channel instead, leaving less current to charge  $C_{INT}$ , and therefore,  $V_{INT}$  is reduced. However, the use of a large  $R_{G(OFF)}$  is not desirable to reduce  $V_{INT}$ , because it does not lead to a reduction in the total capacitive energy loss at the interropte [7]. Part of the energy which is supposed to charge  $C_{INT}$  to the voltage determined by the capacitance ratio ( $C_{DS-D}/C_{INT}$ ), is dissipated earlier due to the Miller effect (turn-on of the E-mode channel during turn-off) [7]. In addition, a large  $R_{G(OFF)}$  can cause a slow switching speed of the E-mode part and limit the overall operating frequency of the cascode device.

Alternatively, we added a FP to the low voltage E-mode part to further reduce the ratio between  $C_{DS-D}$  and  $(C_{DS-D} +$  $C_{INT}$ ), as shown in the equivalent circuit for Device C and D in Fig. 9. The E-mode FP in Device C is connected to the gate of the E-mode part and the FP induced capacitance  $(C_{FP-E})$  is added to  $C_{GD-E}$ . On the other hand, the E-mode FP in Device D acts as a source-connected FP in the E-mode part and  $C_{FP-E}$ is added to  $C_{DS-E}$ . As a result, the off-state  $V_{INT}$  is reduced to ~33 V for both devices, 12 % less compared to Device B, as shown in the switching results in Fig. 5.  $V_{INT}$  of Devices C and D are still relatively large compared to that of Device A, mostly due to the small value of  $C_{FP-E}$ . This could be optimized by varying the thickness of the SiN<sub>x</sub> underneath the E-mode FP. However, the minimum value of  $V_{INT}$  during turn-off is  $-V_{th-D}$ , and an over-engineered  $C_{INT}$  can cause delay in the turn-off of the D-mode part and should be carefully designed.

Overall, an FP connected to the source of the cascode (Device A) is preferable as it results in the lowest off-state  $V_{INT}$  and thus the smallest capacitive energy loss at the internode. To further suppress  $V_{INT}$  for higher voltage operation (>200 V), an additional FP on the E-mode part of Device A can be implemented by connecting to the source of the cascode (Device D) to increase  $C_{INT}$  and hence reduce the ratio of  $C_{DS-D}$  to ( $C_{DS-D} + C_{INT}$ ). Here, the E-mode FP structure of Device D is preferable to Device C because the  $C_{FP-E}$  in Device C increases the effective Miller capacitance ( $C_{GD-E}$ ) of the cascode and can limit the switching performance [1].

### VI. CONCLUSION

Different FP connections in all-GaN integrated cascode transistors were compared in order to match the capacitance and improve the turn-off controllability internally without the worry of additional parasitics. Experimental results showed

that a D-mode FP and an additional E-mode FP both connected to the source terminal of the cascode device was optimum for the minimization of the off-state internode voltage leading to reduced overvoltage stress and capacitive energy loss at the internode. Alternatively, connecting the D-mode FP to the gate of the cascode provides additional 'Miller capacitance' and enables the device to be slowed down via gate resistance when necessary.

# VII. ACKNOWLEDGMENT

The authors acknowledge financial support from the UK Engineering and Physics Sciences Research Council (EPSRC) under projects EP/K014471/1 and EP/N015878/1.

#### REFERENCES

- [1] S. Jiang, K. B. Lee, I. Guiney, P. F. Miaja, Z. H. Zaidi, H. Qian, D. J. Wallis, A. J. Forsyth, C. J. Humphreys and P. A. Houston, "All-GaN-Integrated Cascode Heterojunction Field Effect Transistors," *IEEE Transactions on Power Electronics*, vol. 32, no. 11, pp. 8743-8750, Nov. 2017.

- [2] X. Huang, Z. Liu, Q. Li, and F. C. Lee, "Evaluation and application of 600 V GaN HEMT in cascode structure," *IEEE Transactions on Power Electronics*, vol. 29, no. 5, pp. 2453-2461, 2014

- [3] T. Hirose, M. Imai, K. Joshin, K. Watanabe, T. Ogino, Y. Miyazaki, K. Shono, T. Hosoda, and Y. Asai, "Dynamic performances of GaN-HEMT on Si in cascode configuration," *In Applied Power Electronics Conference and Exposition (APEC), 2014 Twenty-Ninth Annual IEEE*, pp. 174-181, 2014.

- [4] X. Huang, W. Du, F. C. Lee, Q. Li, and Z. Liu, "Avoiding Si MOSFET avalanche and achieving zero-voltage switching for cascode GaN devices," *IEEE Trans. Power Electronics*, vol. 31, no. 2, pp. 593-600, Jan. 2016.

- [5] W. Du, X. Huang, F. C. Lee, Q. Li, and W. Zhang, "Avoiding divergent oscillation of cascode GaN device under high current turn-off condition," *In Applied Power Electronics Conference and Exposition* (APEC), pp. 1002-1009, 2016.

- [6] J. Roig, F. Bauwens, A. Banerjee, W. Jeon, A. Young, J. McDonald, B. Padmanabhan, and C. Liu, "Unified theory of reverse blocking dynamics in high-voltage cascode devices," In *Applied Power Electronics Conference and Exposition (APEC)*, pp. 1256-1261, 2015.

- [7] S. R. Bahl, and M. D. Seeman, "New electrical overstress and energy loss mechanisms in GaN cascodes," In *Applied Power Electronics Conference and Exposition (APEC)*, pp. 1262-1265, 2015.

- [8] W. Saito et al., "Switching controllability of high voltage GaN-HEMTs and the cascode connection," *In 24th International Symposium on IEEE Power Semiconductor Devices and ICs (ISPSD)*, 2012.

- [9] D. Aggeler et al., "Dv/Dt-Control Methods for the SiC JFET/Si MOSFET Cascode," *IEEE Trans. on Power Electronics*, vol. 28, no. 8, pp. 4074-4082, 2013.

- [10] R. Chu, A. Corrion, M. Chen, R. Li, D. Wong, D. Zehnder, B. Hughes, and K. Boutros, "1200-V normally off GaN-on-Si field-effect transistors with low dynamic on-resistance." *IEEE Electron Device Letters*, vol. 32, no. 5, pp. 632-634, 2011.

- [11] W. Saito, T. Nitta, Y. Kakiuchi, Y. Saito, K. Tsuda, I. Omura, and M. Yamaguchi, "Suppression of dynamic on-resistance increase and gate charge measurements in high-voltage GaN-HEMTs with optimized field-plate structure," *IEEE transactions on electron devices*, vol. 54, no. 8, pp. 1825-1830, 2007.

- [12] H. Jung, P. Abele, J. Grünenpütt, M. Hosch, B. Schauwecker, H. Blanck, T. Rödle, and M. Schäfer, "Output capacitance on GaN HEMTs in correlation to its transistor geometry and sheet resistance," *Physica status solidi* (c), vol. 11, no. 3-4, pp. 940-944, 2014.

- [13] D. Čučak, M. Vasić, O. García, J. A. Oliver, P. Alou, J. A. Cobos, A. Wang, S. Martín-Horcajo, M. F. Romero, and F. Calle, "Physics-Based Analytical Model for Input, Output, and Reverse Capacitance of a GaN HEMT with the Field-Plate Structure," *IEEE Transactions on Power Electronics*, vol. 32, no. 3, pp. 2189-2202, 2017.

- [14] M. Rodríguez, Y. Zhang, and D. Maksimović, "High-frequency PWM buck converters using GaN-on-SiC HEMTs," *IEEE transactions on Power Electronics*, vol. 29, no. 5, pp. 2462-2473, 2014

- [15] H. Y. Wu et al, "GaN cascode performance optimization for high efficient power applications," In 2016 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), pp. 255-258, 2016.