This is a repository copy of Response-time analysis for fixed-priority systems with a write-back cache.

White Rose Research Online URL for this paper: <a href="https://eprints.whiterose.ac.uk/id/eprint/129693/">https://eprints.whiterose.ac.uk/id/eprint/129693/</a>

Version: Published Version

## Article:

Davis, Robert Ian orcid.org/0000-0002-5772-0928, Altmeyer, Sebastian and Reineke, Jan (2018) Response-time analysis for fixed-priority systems with a write-back cache. Real-Time Systems. ISSN: 1573-1383

https://doi.org/10.1007/s11241-018-9305-z

# Reuse

This article is distributed under the terms of the Creative Commons Attribution (CC BY) licence. This licence allows you to distribute, remix, tweak, and build upon the work, even commercially, as long as you credit the authors for the original work. More information and the full terms of the licence here: https://creativecommons.org/licenses/

## Takedown

If you consider content in White Rose Research Online to be in breach of UK law, please notify us by emailing eprints@whiterose.ac.uk including the URL of the record and the reason for the withdrawal request.

# Response-time analysis for fixed-priority systems with a write-back cache

Robert I. Davis<sup>1,2</sup> · Sebastian Altmeyer<sup>3</sup> · Jan Reineke<sup>4</sup>

© The Author(s) 2018

Abstract This paper introduces analyses of write-back caches integrated into response-time analysis for fixed-priority preemptive and non-preemptive scheduling. For each scheduling paradigm, we derive four different approaches to computing the additional costs incurred due to write backs. We show the dominance relationships between these different approaches and note how they can be combined to form a single state-of-the-art approach in each case. The evaluation explores the relative performance of the different methods using a set of benchmarks, as well as making comparisons with no cache and a write-through cache. We also explore the effect of write buffers used to hide the latency of write-through caches. We show that depending upon the depth of the buffer used and the policies employed, such buffers can result in domino effects. Our evaluation shows that even ignoring domino effects, a substantial write buffer is needed to match the guaranteed performance of write-back caches.

**Keywords** Write-back cache · Cache-related preemption delays (CRPD) · Schedulability analysis · Fixed priority scheduling · Real-time

⊠ Robert I. Davis rob.davis@york.ac.uk

Sebastian Altmeyer altmeyer@uva.nl

Jan Reineke reineke@cs.uni-saarland.de

University of York, York, UK

Published online: 11 April 2018

- 2 INRIA, Paris, France

- <sup>3</sup> University of Amsterdam, Amsterdam, Netherlands

- Saarland University, Saarland Informatics Campus, Saarbrücken, Germany

### Extended version

This paper builds upon and extends the RTNS 2016 paper *Analysis of Write-Back Caches under Fixed-Priority Preemptive and Non-preemptive Scheduling* (Davis et al. 2016) as follows:

- Worked examples have been added, in Sects. 4.3 and 5.4, illustrating the incomparability and dominance relationships between the different analysis methods.

- A brief discussion of the sustainability of the analysis is given in Sect. 6.

- Additional experiments have been added, in Sect. 7.1, exploring how the performance of the various analysis methods is impacted by changes in the number of tasks and by the memory delay.

- A discussion and evaluation of the impact of write buffers on the performance of write-through caches has been added in Sect. 8. Here we show that depending on the precise policies employed, write buffers may result in domino effects, severely affecting guaranteed performance.

- Finally, while data-cache analysis is not the main focus of the paper, we review related work in this area in the Appendix.

## 1 Introduction

During the last two decades, applications in aerospace and automotive electronics have progressed from deploying embedded microprocessors clocked in the 10's of MHz range to higher performance devices operating in the 100's of MHz to GHz range. The use of high-performance embedded microprocessors has meant that access times to main memory have become a significant bottleneck, necessitating the use of caches to tackle the increasing gap between processor and memory speeds.

Caches may be classified according to the type of information that they store, thus we have *data caches*, *instruction caches*, and *unified caches* which store both instructions and data. In this paper, we are interested in the behaviour of single-level data and unified caches. The behaviour of these caches is crucially dependent on the *write policy* used. Two policies are commonly employed: *write back* and *write through*. In caches using a write-through policy, writes immediately go to memory, thus multiple writes to the same location incur an unnecessarily high overhead. In caches using the write-back policy, writes are not immediately written back to memory. Instead, writes are performed in the cache and the affected cache lines are marked as *dirty*. Only upon eviction of a dirty cache line are its contents written back to main memory. This has the potential to greatly reduce the overall number of writes to main memory compared to a write-through policy, as multiple writes to the same location and multiple writes to different locations in the same cache line can be consolidated.

Evictions of dirty cache lines are a source of interference between different tasks sharing a cache. The execution of a task may leave dirty cache lines in the cache that will have to be written back during the execution of another task, delaying that task's execution. A read which is a cache miss and evicts a dirty cache line may incur approximately twice the delay compared to evicting a non-dirty line, since the former requires both a read from memory and an additional write back of the dirty line. This

may occur with non-preemptive as well as with preemptive scheduling, and dirty cache lines left by low priority tasks may impact the response time of higher priority tasks and vice-versa. This is in contrast to the impact of evictions with a write-through cache, which only affect other tasks under preemptive scheduling, and then only tasks of lower priority. In this paper, we discuss different ways of soundly accounting for write backs, and show how to integrate these costs into response-time analysis for both fixed-priority preemptive and non-preemptive scheduling. We also consider the use of write buffers as a way of hiding the write latency inherent in a write-through cache. We show that the use of such buffers can potentially lead to domino effects.

#### 1.1 Related work

# 1.1.1 Accounting for overheads in schedulability analysis

Early work on accounting for scheduling overheads in fixed-priority preemptive systems by Katcher et al. (1993) and Burns (1994) focused on scheduler overheads and context switch costs. Subsequent work on the analysis of Cache Related Preemption Delays (CRPD) and their integration into schedulability analyses used the concepts of Useful Cache Blocks (UCBs) and Evicting Cache Blocks (ECBs), see Sect. 2.1 of (Altmeyer and Maiza 2011) for a detailed description. A number of methods have been developed for computing CRPD under fixed-priority preemptive scheduling. Busquets-Mataix et al. (1996) introduced the ECB-Only approach, which considers just the preempting task; while Lee (1998) developed the UCB-Only approach, which considers just the preempted task (s). Both the UCB-Union approach (Tan and Mooney 2007), and the ECB-Union approach (Altmeyer et al. 2011) consider both the preempted and preempting tasks. As does an alternative approach developed by Staschulat et al. (2005). These approaches were later superseded by multiset based methods (ECB-Union Multiset and UCB-Union Multiset) which dominate them (Altmeyer et al. 2012). These methods have been adapted by Lunniss et al. (2013, 2014a) to EDF scheduling and to hierarchical scheduling with local fixed-priority (Lunniss et al. 2014b) and EDF (Lunniss et al. 2016) schedulers. They have also been integrated into a response time analysis framework for multicore systems (Altmeyer et al. 2015).

Cache partitioning is one way of eliminating CRPD; however, this results in inflated worst-case execution times due to the reduced cache partition size available to each task. Altmeyer et al. (2014, 2016) derived an optimal cache partitioning algorithm for the case where each task has its own partition. They compared cache partitioning and cache sharing accounting for CRPD, concluding that the trade off between longer worst-case execution times and CRPD often favours sharing the cache rather than partitioning it.

Preemption thresholds (Wang and Saksena 1999; Saksena and Wang 2000) provide an alternative means of reducing CRPD by making certain groups of tasks non-preemptable with respect to each other. Bril et al. (2014) integrated CRPD into analysis for fixed-priority scheduling with preemption thresholds. Further work in this area by Wang et al. (2015) showed that by using preemption thresholds, groups of tasks

can share a partition while still avoiding CRPD. This results in a hybrid approach that can outperform the approach of Altmeyer et al. (2014).

As far as we are aware, all of the prior work on integrating CRPD into schedulability analysis assumes write-through caches. In this paper, we explore the impact of using write-back caches instead.

With write-through caches, non-preemptive scheduling provides a simple means of eliminating CRPD without increasing worst-case execution times, since each task can still utilise the entire cache. However, with write-back caches, non-preemptive scheduling is insufficient to eliminate all cache-related interference effects. In this paper, we therefore consider the effects of write-back caches under both fixed-priority preemptive scheduling and fixed-priority non-preemptive scheduling. As this is the *first* such study of the impact of write backs, we restrict our attention to direct-mapped caches (examples of microprocessors that implement such caches are given in Sect. 2). In future, we aim to extend the techniques to set-associative caches and replacement policies such as LRU using the methodology given by Altmeyer et al. (2011).

#### 1.1.2 Write-back caches in worst-case execution time (WCET) analysis

Ferdinand and Wilhelm (1999) introduced an analysis of write-back caches to determine for each memory access, which cache lines may have to be written back. The basic idea is to track for each potentially dirty memory block whether it must or may be cached; however, this analysis has neither been integrated into a WCET analysis nor has it been experimentally evaluated. Sondag and Rajan (2010) implement a similar idea in the context of multi-level cache analysis, where the write-back behaviour of the first-level cache influences the contents of the second-level cache. While potential write backs from the first- to the second-level cache are correctly accounted for, the cost of write backs to main memory does not seem to be taken into account within their WCET analysis. We note that both approaches (Ferdinand and Wilhelm 1999; Sondag and Rajan 2010) are not particularly suited to precisely bound the number of write backs, as imprecisions in the may- and must-analyses yield many potential write backs for a single write back in a concrete execution. To analyze a program's WCET, Li et al. (1996) proposed to capture both the software and the microarchitectural behaviour via integer linear programming (ILP). Their analysis is able to cover write-back caches, however, scalability is a major concern. The key distinction between the work presented in this paper and previous research is that our work focuses on the open problem of integrating write-back costs into schedulability analysis. Data cache analysis is not per-se the focus of the work in this paper, nevertheless we provide a discussion of related work in that area in the appendix. For readers interested in cache analysis techniques, a recent survey is given by Lv et al. (2016).

## 1.2 Organisation

The remainder of the paper is organized as follows. Section 2 discusses caches, different write policies and a classification of write backs, as well as how a task's write-back behaviour can be characterized. Section 3 sets out the task model used and recaps on

existing response-time analysis techniques. Sections 4 and 5 derive analyses bounding the cost of using write-back caches under fixed-priority non-preemptive and fixed-priority preemptive scheduling respectively. Section 6 discusses the *sustainability* of the analysis presented in those sections. Section 7 provides an evaluation of the performance of the different analyses for write-back caches, as compared to no cache and a write-through cache. Section 8 discusses the use of write buffers to improve the performance of write-through caches, and evaluates the effectiveness of different sized buffers. Section 9 discusses how information characterising write-back cache behaviour can be obtained. Finally, Sect. 10 concludes with a summary and a discussion of how the work in this paper may be extended. The appendix provides a brief review of related work on data cache analysis.

#### 2 Caches

Caches are fast but small memories that store a subset of the main memory's contents to bridge the difference in speed between the processor and main memory. To reduce management overhead and to profit from spatial locality, data is not cached at the granularity of words, but at the granularity of so-called *memory blocks*. To this end, main memory is logically partitioned into equally-sized memory blocks. Blocks are cached in *cache lines* of the same size. The size of a memory block varies from one processor to another, but is usually between 32 and 128 bytes.

When accessing a memory block, the cache logic has to determine whether the block is stored in the cache, a *cache hit*, or not, a *cache miss*. To enable an efficient look-up, each memory block can only be stored in a small number of cache lines referred to as a *cache set*. Thus caches are partitioned into a number of equally-sized cache sets. The size of a cache set is called the *associativity* of the cache.

The *placement policy* determines the cache set a memory block maps to. Typically, the number of cache sets is a power of two, and *modulo placement* is employed, where the least significant bits of the block number determine the cache set that a memory block maps to. Since caches are usually much smaller than main memory, a *replacement policy* is used to decide which memory block to replace on a cache miss. As stated earlier, we limit our attention to *direct-mapped* caches, where each cache set consists of exactly one cache line. In this case, the only possible action on a cache miss is to replace the memory block currently stored in the cache line that the accessed memory block maps to.

In this paper, we assume a timing-compositional architecture (Hahn et al. 2013), i.e. the timing contribution of cache misses and write backs can be analyzed separately from other architectural features such as the pipeline behaviour.

## 2.1 Write policies

Data written to the cache needs to eventually also be written to main memory. When exactly the data is written to main memory is determined by the *write policy*. There are two basic write policies: With a *write-through* policy, the write to main memory is requested at the same time as the write to the cache. With a *write-back* policy, the write

to main memory is postponed until the memory block containing the data is evicted from the cache, it is then written back to main memory in its entirety.

Write through is simpler to implement than write back, but may result in a significantly larger number of accesses to main memory. If a cached memory block is written to multiple times before being evicted, under write back only the final write needs to be performed to main memory. The drawback of write-back caches is that additional *dirty* bits are required to keep track of which cache lines have been modified since they were fetched from main memory, the writes are delayed, and the logic required to implement the cache is more complex.

Due to the potential performance advantages of write-back caches they are often preferred in embedded microprocessor designs. Alternatively, caches may be configurable as write back or write through. Examples include: Infineon Tricore TC1M (separate data and instruction caches, LRU replacement policy, write back); Freescale MPC740 (separate data and instruction caches, PLRU replacement policy, configurable for write back or write through); Renesas SH7705 (unified data and instruction cache, LRU replacement policy, configurable for write back or write through); Renesas SH7750 (separate instruction and data caches, direct mapped, configurable for write back or write through); NEC VR4181 and VR4121 (separate instruction and data caches, direct mapped, write back).

A second question to answer when designing a cache is what happens on a write to a memory block that is not cached. There are two *write-miss policies*: With *write allocate* a cache line is allocated to the memory block containing the word that is being written, which is fetched from main memory, then the write is performed in the cache. With *no-write allocate* the write is performed only in main memory, and no cache line is allocated. In principle, each write policy can be used in conjunction with each write-miss policy; however, usually, write through is combined with no-write allocate, and write back is combined with write allocate. In this paper we assume a cache employing *write back* and *write allocate*, which minimizes the total number of accesses to main memory.

#### 2.2 Classification of write backs

For analysis purposes, it is useful to classify write backs into three categories:

*Job-internal* write backs. These are write backs of dirty cache lines previously written to by the same job. We assume that the cost of job-internal write backs is included in the WCET of a task, since it does not depend on the scheduling policy used.

Carry-in write backs. These are write backs of dirty cache lines that were not written to by the job itself and that were present in the cache when the job was dispatched. We assume that the cost of carry-in write backs is not included in the WCET of a task, since it depends on the scheduling policy used. (The WCET is instead determined assuming an arbitrary, but clean initial cache state). Carry-in write backs can be further distinguished depending on whether they emanate from a job that is still active or not: Carry-in write backs from jobs that are still active can only come from lower priority preempted tasks. We refer to these as "lp-carry-in" write backs. Carry-in write backs

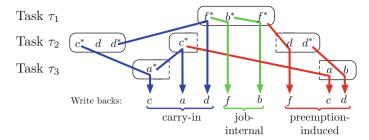

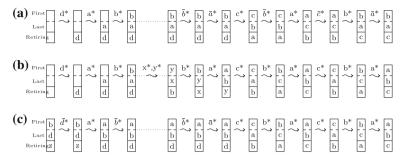

Fig. 1 Example illustrating different kinds of write backs

from finished jobs can emanate from both lower and higher priority tasks. We refer to these as "finished-carry-in" write backs.

*Preemption-induced* write backs. These are write backs of dirty cache lines that were not written to by the task itself and that were introduced by a preempting task. Preemption-induced write backs can only come from higher priority jobs that are finished.

Consider Fig. 1 for an example schedule of three tasks containing the three types of write backs described above. In the example,  $x^*$  denotes a write to memory block x, whereas just x denotes a read from memory block x. Memory blocks a, c and b, d, f map to the same cache sets, and hence cache lines, respectively.

The first write to memory block a of task  $\tau_3$ , causes the eviction of c, which was written to by a finished job of task  $\tau_2$ , thus it causes a *finished-carry-in* write-back. On the other hand, the access to c in the second job of  $\tau_2$ , causes an lp-carry-in write back of a. The first access to b within task  $\tau_1$  evicts f, which was previously modified in the same job, thus causing a job-internal write back. Finally, the read of d in the second job of task  $\tau_2$  causes a preemption-induced write back of f which was previously written to by task  $\tau_1$ . Similarly, the reads of a and b in task  $t_2$  result in preemption-induced write backs of  $t_2$  and  $t_3$  previously written to by task  $t_3$ .

## 2.3 Characterizing a task's write backs

We assume that job-internal write backs are accounted for within WCET analysis. To bound carry-in write backs, and in the case of preemptive scheduling, preemption-induced write backs, we need to characterize the memory-access behaviour of each task. To do so, we introduce the following concepts:

An Evicting Cache Block (ECB) of task  $\tau_i$  is a memory block that may be accessed by task  $\tau_i$ . We denote the set of cache lines that evicting cache blocks of task  $\tau_i$  map to by  $ECB_i$ . Note ECBs have previously been considered in the analysis of cache-related preemption delays (Altmeyer et al. 2012).

A *Dirty Cache Block* (DCB) of task  $\tau_i$  is a memory block that may be written to by task  $\tau_i$ . We denote the set of cache lines that dirty cache blocks of task  $\tau_i$  map to by  $DCB_i$ .

A *Final Dirty Cache Block* (FDCB) of task  $\tau_i$  is a DCB that may still be cached at completion of the task. We denote the set of cache lines that final dirty cache blocks of task  $\tau_i$  map to by  $FDCB_i$ . (By definition,  $FDCB_i \subseteq DCB_i \subseteq ECB_i$ ).

By evicting dirty cache lines, ECBs may cause both carry-in and preemption-induced write backs. In preemptive scheduling, lp-carry-in write backs may occur due to DCBs, while preemption-induced and finished-carry-in write backs can only be due to FDCBs. In non-preemptive scheduling, preemption-induced write backs do not occur, and carry-in write backs are necessarily finished-carry-in write backs, and can thus only be due to FDCBs. With both scheduling paradigms, job-internal write backs can occur and carry-in write backs can occur due to jobs of all tasks, including the previous job of the same task.

# 3 Task model and basic analysis

In this section, we set out the basic task model used in the rest of the paper, and recapitulate existing response-time analyses for fixed-priority preemptive scheduling (FPPS) and fixed-priority non-preemptive scheduling (FPNS).

#### 3.1 Task model

We consider a set of sporadic tasks scheduled on a uniprocessor under either FPPS or FPNS. A task set  $\Gamma$  comprises a static set of n tasks  $\{\tau_1, \tau_2, \ldots, \tau_n\}$ . Each task has a unique priority, which without loss of generality is given by its index. Thus task  $\tau_1$  has the highest priority and task  $\tau_n$  the lowest. Each task  $\tau_i$  gives rise to a potentially unbounded sequence of jobs separated by a minimum inter-arrival time or period  $T_i$ . Each job of task  $\tau_i$  has a bounded worst-case execution time  $C_i$ , and relative deadline  $D_i$ . Deadlines are assumed to be *constrained*, i.e.  $D_i \leq T_i$ . Note  $C_i$  is the worst-case execution time in the non-preemptive case, starting from an arbitrary clean cache. Thus  $C_i$  does not include the cost of reloading cache lines evicted due to preemption, or additional write backs that may be required when loading memory blocks into dirty cache lines. On the other hand, it does include the cost of job-internal write backs.

The worst-case response time  $R_i$  of task  $\tau_i$  is given by the longest time from the release of a job of the task until it completes execution. If the worst-case response time is not greater than the deadline  $(R_i \leq D_i)$ , then the task is said to be schedulable. The utilization  $U_i$  of a task  $\tau_i$  is given by  $U_i = \frac{C_i}{T_i}$  and the utilization of the task set is the sum of the utilizations of the individual tasks  $U = \sum_{i=1}^n U_i$ .

We use hp(i) and hep(i) to denote respectively the set of indices of tasks with priorities higher than, and higher than or equal to that of task  $\tau_i$  (including  $\tau_i$  itself). Similarly, we use lp(i) and lep(i) to denote respectively the set of indices of tasks with priorities lower than, and lower than or equal to that of task  $\tau_i$ .

## 3.2 Schedulability analysis for FPPS

For task sets with constrained deadlines scheduled using FPPS, the exact response time of task  $\tau_i$  may be computed according to the following recurrence relation (Audsley et al. 1993; Joseph and Pandya 1986):

$$R_i^P = C_i + \sum_{j \in hp(i)} \left\lceil \frac{R_i^P}{T_j} \right\rceil C_j \tag{1}$$

Iteration starts with  $R_i^P = C_i$  and ends either on convergence or when  $R_i^P > D_i$  in which case the task is unschedulable.

# 3.3 Schedulability analysis for FPNS

Determining exact schedulability of a task  $\tau_i$  under FPNS requires checking all of the jobs of task  $\tau_i$  within the worst-case priority level-*i* busy period (Bril et al. 2009). (This is the case even when all tasks have constrained deadlines).

The worst-case priority level-i busy period starts with an interval of blocking due to a job of the longest task of lower priority than  $\tau_i$ . Just after that job starts to execute, jobs of task  $\tau_i$  and all higher priority tasks are released simultaneously, and then rereleased as soon as possible. Finally, the busy period ends at some time t when there are no ready jobs of priority i or higher that were not released strictly before time t.

In this paper, we make use of the following *sufficient* schedulability test for FPNS, applicable only to constrained-deadline task sets. It is based on a test originally given for non-preemptive scheduling on Controller Area Network (CAN) (Davis et al. 2007). This schedulability test considers two scenarios. Either the worst-case response time for task  $\tau_i$  occurs for the first job in the priority level-i busy period, or for a subsequent job. The start time  $W_{i,0}^{NP}$  of the first job q=0 of task  $\tau_i$  in the worst-case priority level-i busy period can be computed using the following recurrence relation:

$$W_{i,0}^{NP} = \max_{k \in lp(i)} C_k + \sum_{j \in hp(i)} \left( \left\lfloor \frac{W_{i,0}^{NP}}{T_j} \right\rfloor + 1 \right) C_j$$

(2)

and hence its worst-case response time is given by:

$$R_{i,0}^{NP} = W_{i,0}^{NP} + C_i (3)$$

Subsequent jobs of task  $\tau_i$  may be subject to *push-through* blocking due to non-preemptive execution of the previous job of the same task. Let the jobs of task  $\tau_i$  be indexed by values of  $q=0,1,\ldots$ , where q=0 is the first job in the busy period. We consider job q+1, assuming that job q is schedulable (we return to this point later). Since job q is schedulable it completes by its deadline at the latest and therefore also by the release of job q+1. Consider the length of the time interval from when job q starts executing to when job q+1 starts executing. Note when job q starts executing

there can be no jobs of higher priority tasks that are ready to execute. In the worst-case, jobs of all higher priority tasks may be released immediately after job q starts to execute. Thus an upper bound on the length  $W_{i,q+1}^{NP}$  of this interval can be computed using the following recurrence relation:

$$W_{i,q+1}^{NP} = C_i + \sum_{j \in hp(i)} \left( \left\lfloor \frac{W_{i,q+1}^{NP}}{T_j} \right\rfloor + 1 \right) C_j \tag{4}$$

Since we assume that job q completes by its deadline and deadlines are constrained  $(D_i \leq T_i)$ , then the interval  $W_{i,q+1}^{NP}$  must also upper bound the time from the release of job q+1 until it starts to execute. As job q+1 takes time  $C_i$  to execute, an upper bound on its worst-case response time is given by:

$$R_{i,q+1}^{NP} = W_{i,q+1}^{NP} + C_i (5)$$

Assuming that job q=0 is schedulable according to (2) then schedulability of the second and subsequent jobs in the busy period can be determined by induction using (5).

We note the similarity between (2) and (4), and also between (3) and (5). Thus we may combine them obtaining an upper bound for the response time of task  $\tau_i$ , under FPNS. This upper bound may be compared with the task's deadline to determine schedulability.

$$W_i^{NP} = \max_{k \in lep(i)} C_k + \sum_{j \in hp(i)} \left( \left\lfloor \frac{W_i^{NP}}{T_j} \right\rfloor + 1 \right) C_j \tag{6}$$

$$R_i^{NP} = W_i^{NP} + C_i (7)$$

The analysis expressed in (5) can be improved by noting that the start time of job q must be at least  $C_i$  before the release of job q + 1, hence the response time upper bound given in (5) may be reduced by  $C_i$ . In this paper, for ease of presentation, we make use of the simpler test embodied in (6) and (7).

# 4 Write backs under FPNS

In this section, we extend the sufficient schedulability test for FPNS for constrained-deadline task sets given in (6) and (7) to account for carry-in write backs. In non-preemptive scheduling only job-internal and finished-carry-in write backs may occur. As discussed earlier, we assume that job-internal write backs are accounted for within WCET analysis.

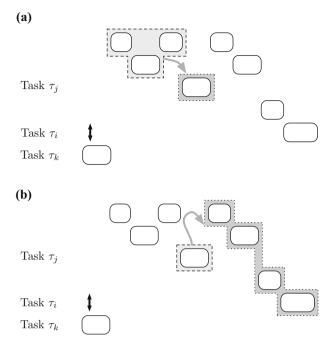

We identify two methods of accounting for finished-carry-in write backs, which are illustrated in Fig. 2. In the first method, we associate with each job of a task, the carry-in write backs that occur within the job. This method is used in the ECB-Only and FDCB-Union approaches described in Sect. 4.1. By contrast, in the second method we

**Fig. 2** Carry-in write backs may be accounted for either, **a** within the job of the task  $\tau_i$  under analysis, or **b** in subsequent jobs of both higher (e.g.  $\tau_i$ ) and lower (e.g.  $\tau_k$ ) priority tasks

associate with each job of a task the carry-in write backs that occur in *subsequent jobs* due to dirty cache lines left by the job itself. This method is used in the *FDCB-Only* and *ECB-Union* approaches described in Sect. 4.2.

## 4.1 Carry-in write backs within the job

## 4.1.1 ECB-Only approach

The number of ECBs provides an upper bound on the number of carry-in write backs a task suffers. Thus, assuming timing compositionality (Hahn et al. 2013), the WCET of task  $\tau_i$ , including the cost of write backs, is bounded by

$$C_i' = C_i + WBT \cdot |ECB_i| \tag{8}$$

where WBT is an upper bound on the time to perform one write back. Replacing  $C_i$  by  $C'_i$  as defined above (and similarly  $C_k$  and  $C_j$ ), (6) and (7) can be used to derive worst-case response times accounting for write backs.

<sup>&</sup>lt;sup>1</sup> Note that this holds for direct-mapped caches as well as for set-associative caches with LRU replacement. This is different from additional cache misses, which are not directly bounded by the number of ECBs (Burguière et al. 2009).

# 4.1.2 FDCB-Union approach

The ECB-Only approach can be improved upon by taking into account which cache lines may be dirty when a job is started. In non-preemptive execution, dirty cache lines at a job's start are the final dirty cache lines left by other jobs.

When analyzing  $\tau_i$ 's response time, we distinguish two types of finished-carry-in write backs: Those that are due to dirty cache lines introduced before  $\tau_i$ 's release by tasks with lower or equal priority to  $\tau_i$ , represented by  $\delta_i$ , and those that are due to dirty cache lines introduced before and after  $\tau_i$ 's release by tasks of higher priority than  $\tau_i$ , represented by  $\gamma_i^{\text{wb}}$ .

Each final dirty cache line of a task with priority lower than or equal to that of task  $\tau_i$  may result in at most one write back during  $\tau_i$ 's response time, excluding write backs that occur during the blocking time. Write backs of these dirty cache lines can only occur within the response time of task  $\tau_i$  if the cache lines are accessed by (i.e. in the  $ECB_k$ ) some task  $\tau_k$  of priority i or higher. The term  $\delta_i$  accounts for these write backs. Note that we exclude from  $\delta_i$  cache lines that may be dirty due to higher priority tasks as such cache lines are accounted for by the  $\gamma_{i,j}^{wb}$  term introduced next, thus:

$$\delta_i = WBT \cdot \left| \left( \bigcup_{k \in lep(i)} FDCB_k \setminus \bigcup_{k \in hp(i)} FDCB_k \right) \cap \left( \bigcup_{k \in hep(i)} ECB_k \right) \right| \quad (9)$$

The number of finished-carry-in write backs that can be made during the execution of one job of task  $\tau_j$  due to dirty cache lines introduced by tasks of higher priority than  $\tau_i$  is upper bounded by  $\gamma_{i,j}^{\text{wb}}$ . Note that only cache lines accessed by task  $\tau_j$  (i.e. in  $ECB_j$ ) can be written back during the execution of a job of  $\tau_j$ .

$$\gamma_{i,j}^{\text{wb}} = WBT \cdot \left| \left( \bigcup_{k \in hp(i)} FDCB_k \right) \cap ECB_j \right|$$

(10)

We now adapt (6) and (7) to include the write backs  $(\gamma_{n+1,b}^{wb})$  that can occur within one job of a blocking task  $\tau_b$ ; the write backs  $(\delta_i)$  that can occur during jobs other than that of a blocking task, due to dirty cache lines left by tasks of lower priority than  $\tau_i$  before the start of the busy period; and finally, the write backs  $(\gamma_{i,j}^{wb})$  and  $(\gamma_{i,i}^{wb})$  that can occur within each of the other jobs that contribute to the response time of task  $(\gamma_i)$ , due to dirty cache lines introduced by tasks of higher priority than  $(\gamma_i)$ .

$$W_{i,WB}^{NP} = \max_{b \in lep(i)} \left( C_b + \gamma_{n+1,b}^{\text{wb}} \right) + \delta_i$$

$$+ \sum_{j \in hp(i)} \left( \left\lfloor \frac{W_{i,WB}^{NP}}{T_j} \right\rfloor + 1 \right) \left( C_j + \gamma_{i,j}^{\text{wb}} \right)$$

(11)

$$R_{i,WB}^{NP} = W_{i,WB}^{NP} + \left(C_i + \gamma_{i,i}^{\text{wb}}\right) \tag{12}$$

In the  $\gamma_{n+1,b}^{\text{wb}}$  term, n+1 denotes a priority that is lower than that of any task, thus  $\gamma_{n+1,b}^{\text{wb}}$  accounts for all carry-in write backs that may occur during the execution of a blocking task  $\tau_b$  due to cache lines left dirty by previous jobs of any task. In contrast,  $\gamma_{i,j}^{\text{wb}}$  and  $\gamma_{i,i}^{\text{wb}}$  need only cover write backs due to dirty cache lines from tasks of higher priority than  $\tau_i$ , since all other write backs are accounted for in  $\delta_i$ .

The ECB-Only approach pessimistically assumes that each time a task is executed the cache is full of dirty cache lines. The FDCB-Union approach improves upon this by more precisely modeling which cache lines could actually be dirty. FDCB-Union strictly dominates ECB-Only, meaning that any task set that is deemed schedulable according to the ECB-Only approach is guaranteed to be deemed schedulable using the FDCB-Union approach. This can be seen by first considering the  $C_j + \gamma_{i,j}^{\text{wb}}$  terms in (11) and (12). From (10), it follows that  $C_j + \gamma_{x,j}^{\text{wb}}$  cannot be greater than the value of  $C'_i$  used in (8) for any task  $\tau_i$  and index x, and hence cannot exceed the inflated WČET values used in the ECB-Only approach. Second, we must consider the additional contributions in the  $\delta_i$  term. For an FDCB to contribute to  $\delta_i$ , then from (9), that FDCB cannot be in  $FDCB_k$  of any task  $\tau_k$  with a priority higher than that of task  $\tau_i$ . Also, it must be in the  $ECB_i$  of task  $\tau_i$  or the  $ECB_k$  of some higher priority task  $\tau_k$ . If it is in  $ECB_i$  and contributes to  $\delta_i$  then from (10) it is not included in the  $\gamma_{i,i}^{\text{wb}}$  term in (12), thus the inflated WCET  $C_i'$  in the ECB-Only approach covers both this contribution to  $\delta_i$  and the  $\gamma_{i,i}^{\text{wb}}$  term in (12). Similarly, if the FDCB is in  $ECB_j$ and contributes to  $\delta_i$  then it is not included in the  $\gamma_{i,j}^{\text{wb}}$  term in (11), thus the inflated WCET  $C'_i$  in the ECB-Only approach again covers both this contribution to  $\delta$  and  $\gamma_{i,j}^{\text{wb}}$ . Finally, it serves only to consider a system with no FDCBs to see that FDCB-Union strictly dominates ECB-Only. At the other extreme, if all ECBs are also FDCBs, then FDCB-Union reduces to ECB-Only (with  $\delta_i = 0$ ).

#### 4.2 Carry-in write backs in subsequent jobs

## 4.2.1 FDCB-Only approach

Instead of using  $\gamma_{i,j}^{\text{wb}}$  to mean the cost of carry-in write backs that occur within the execution of a job of task  $\tau_j$ , we can re-define  $\gamma_{i,j}^{\text{wb}}$  to cover the write backs that occur in subsequent jobs due to dirty cache lines left by a job of task  $\tau_j$ . This is achieved by assuming that all of these cache lines may be evicted by the subsequent jobs:

$$\gamma_{i,j}^{\text{wb}} = WBT \cdot \left| FDCB_j \right| \tag{13}$$

With this approach,  $\delta$  needs to account for *all* carry-in write backs due to cache lines that were dirty prior to  $\tau_i$ 's release:

$$\delta = WBT \cdot \left| \bigcup_{k} FDCB_{k} \right| \tag{14}$$

Finally, the final dirty cache lines that  $\tau_i$  leaves do not affect its own response time. As a consequence (12) can be simplified as follows (with (11) unchanged):

$$R_{i,WB}^{NP} = W_{i,WB}^{NP} + C_i (15)$$

## 4.2.2 ECB-Union approach

The above approach can be improved by taking into account which of the dirty cache lines may actually be evicted by subsequent jobs of tasks which may execute within  $\tau_i$ 's response time (i.e. by also considering the cache lines  $(ECB_k)$  accessed by each task  $\tau_k$  of priority i or higher).

$$\gamma_{i,j}^{\text{wb}} = WBT \cdot \left| FDCB_j \cap \left( \bigcup_{k \in hep(i)} ECB_k \right) \right|$$

(16)

Similarly, in the  $\delta_{b,i}$  term, we need only account for those dirty cache lines that may be evicted during  $\tau_i$ 's response time. This depends on the blocking task  $\tau_b$ :

$$\delta_{b,i} = WBT \cdot \left| \left( \bigcup_{k} FDCB_{k} \right) \cap \left( \bigcup_{j \in hep(i) \cup \{b\}} ECB_{j} \right) \right|$$

(17)

Hence we include  $\delta_{b,i}$  in the blocking term resulting in the following adaptation of (11):

$$W_{i,WB}^{NP} = \max_{b \in lep(i)} (C_b + \gamma_{i,b}^{\text{wb}} + \delta_{b,i})$$

$$+ \sum_{j \in hp(i)} \left( \left\lfloor \frac{W_{i,WB}^{NP}}{T_j} \right\rfloor + 1 \right) (C_j + \gamma_{i,j}^{\text{wb}})$$

(18)

The ECB-Union approach strictly dominates the FDCB-Only approach. This can be seen by comparing the  $\gamma_{i,j}^{\text{wb}}$  terms and the  $\delta_{b,i}$  terms. Comparing the  $\gamma_{i,j}^{\text{wb}}$  terms in (13) and (16) we note that surprisingly there is no advantage gained by ECB-Union, since  $FDCB_j \subseteq ECB_j$  and  $i \in lep(j)$  in all uses of this term, hence (16) effectively reduces to (13). Considering the  $\delta_{b,i}$  terms, if there are a number of lower priority tasks with FDCBs that are not present in the ECBs of tasks with priorities higher than or equal to  $\tau_i$  then (17) can improve upon (14), with dominance apparent from the set intersection.

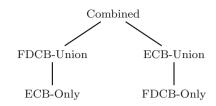

We note that the ECB-Union and FDCB-Union approaches are incomparable, and hence we may form a combined approach by taking the minimum response time computed by either approach. By construction, this combined approach dominates both ECB-Union and FDCB-Union. Since it can be applied on a per task basis, the combined approach classifies more task sets as schedulable than can be found by using the ECB-Union and FDCB-Union approaches individually on each task set. Figure 3 illustrates these relationships via a Hasse diagram.

Fig. 3 Hasse diagram illustrating the dominance relationships between different approaches to account for write backs under fixed-priority non-preemptive scheduling

Table 1 Example task set

| Task                | С   | T    | ECB                    | DCB                    | FDCB   |

|---------------------|-----|------|------------------------|------------------------|--------|

| $\overline{\tau_1}$ | 100 | 1000 | {1, 4, 5}              | {1}                    | {1}    |

| $\tau_2$            | 100 | 1000 | {2, 3, 4, 5}           | {2, 3, 4}              | {2, 3} |

| $\tau_3$            | 100 | 1000 | {2, 3, 5}              | {2, 3, 5}              | {2, 3} |

| $	au_4$             | 100 | 1000 | $\{1, 2, 3, 4, 5, 6\}$ | $\{1, 2, 3, 4, 5, 6\}$ | {1}    |

# 4.3 Worked example

Below, we present a worked example illustrating the various approaches to analysing write backs under fixed-priority non-preemptive scheduling and their differences in performance. Table 1 gives the task set parameters.

For ease of presentation, we assume a write-back delay of 1 and choose task parameters so that only one job of each task may be released during another task's response time. The sets of UCBs are assumed to be empty (i.e. we focus on write backs and do not consider CRPD due to cache misses).

## 4.3.1 ECB-Only

The ECB-Only approach (8) effectively increases the tasks' execution times by  $WBT \cdot |ECB|$ :  $C'_1 = 103$ ,  $C'_2 = 104$ ,  $C'_3 = 103$ ,  $C'_4 = 106$ . The response time is then computed using (6) and (7) giving  $R_1 = 209$ ,  $R_2 = 313$ ,  $R_3 = 416$ , and  $R_4 = 522$ .

#### 4.3.2 FDCB-Union

The FDCB-Union approach extends the ECB-Only approach by taking into account which cache lines may be dirty when a job is started. The term  $\delta_i$  accounts for dirty cache lines of lower or equal priority tasks and is computed using (9):  $\delta_1=1, \delta_2=2, \delta_3=0, \delta_4=0$ . The term  $\gamma_{i,j}^{\text{wb}}$  accounts for write backs due to higher priority tasks and is computed using (10):

Further, we have:  $\gamma_{5,1}^{\text{wb}} = 1$ ,  $\gamma_{5,2}^{\text{wb}} = 2$ ,  $\gamma_{5,3}^{\text{wb}} = 2$ ,  $\gamma_{5,4}^{\text{wb}} = 3$  and  $\gamma_{1,1}^{\text{wb}} = 0$ ,  $\gamma_{2,2}^{\text{wb}} = 0$ ,  $\gamma_{3,3}^{\text{wb}} = 2$ ,  $\gamma_{4,4}^{\text{wb}} = 3$ . The response time is then computed using (11) and (12) giving  $R_1 = 204$ ,  $R_2 = 306$ ,  $R_3 = 408$ , and  $R_4 = 511$ .

Note that the FDCB-Union approach dominates ECB-Only and results in shorter response times in this example.

## 4.3.3 FDCB-Only

The FDCB-Only approach accounts for write backs in subsequent jobs, instead of write backs in the execution of the job itself. Hence, the term  $\delta$  accounts for dirty cache lines prior to the release of the task under analysis and is given by (14) thus  $\delta_i = 3$ . The  $\gamma_{i,i}^{\text{wb}}$  term is given by (13):

$$\begin{array}{c|ccccc} \gamma_{i,j}^{\text{wb}} & 1 & 2 & 3 \\ \hline 2 & 1 & - & - \\ 3 & 1 & 2 & - \\ 4 & 1 & 2 & 2 \end{array}$$

Further,  $\gamma_{5,1}^{\text{wb}} = 1$ ,  $\gamma_{5,2}^{\text{wb}} = 2$ ,  $\gamma_{5,3}^{\text{wb}} = 2$ ,  $\gamma_{5,4}^{\text{wb}} = 1$ . The response time is then computed using (11) and (15) giving  $R_1 = 205$ ,  $R_2 = 306$ ,  $R_3 = 408$ , and  $R_4 = 509$ .

#### 4.3.4 ECB-Union

The ECB-Union approach only differs from FDCB-Only in the  $\delta$  terms. This difference, although technically possible, is neither visible in this example, nor in the evaluation. Instead, the ECB-Union approach results in the same response times as the FDCB-Only approach.

We observe that this example suffices to highlight the incomparability between ECB-Union and FDCB-Union. The response time for task  $\tau_1$  is smaller with FDCB-Union (204 vs. 205), while the response time for task  $\tau_4$  is smaller with ECB-Union (509 vs. 511). The combined approach, taking the minimum response times (204, 306, 408, 509) thus dominates all others.

#### 5 Write backs under FPPS

Response-time analysis for FPPS has previously been extended to account for preemption-related cache misses (Altmeyer et al. 2011, 2012) by introducing a term  $\gamma_{i,j}$  into the response-time equation for task  $\tau_i$  as follows:

$$R_i^P = C_i + \sum_{j \in hp(i)} \left\lceil \frac{R_i^P}{T_j} \right\rceil (C_j + \gamma_{i,j})$$

(19)

To also account for additional write backs in preemptive scheduling, we extend the recurrence relation as follows:

$$R_i^P = \delta_i + C_i + \sum_{j \in hp(i)} \left\lceil \frac{R_i}{T_j} \right\rceil \left( C_j + \gamma_{i,j}^{\text{miss}} + \gamma_{i,j}^{\text{wb}} \right)$$

(20)

Here,  $\delta_i$  is used to account for write backs due to cache lines that were already dirty on release of  $\tau_i$  and are written back within its response time. Additional cache misses due to preemptions are captured by  $\gamma_{i,j}^{\text{miss}}$ . Any of the existing techniques, for example those introduced by Altmeyer et al. (2012), can be used to account for such misses. Finally,  $\gamma_{i,j}^{\text{wb}}$  is used to account for carry-in and preemption-induced write backs of cache lines that were written to after  $\tau_i$ 's release.

cache lines that were written to after  $\tau_i$ 's release. We further sub-divide  $\gamma_{i,j}^{\text{wb}}$  into  $\gamma_{i,j}^{\text{wb-lp}}$  and  $\gamma_{i,j}^{\text{wb-fin}}$ , such that  $\gamma_{i,j}^{\text{wb}} = \gamma_{i,j}^{\text{wb-lp}} + \gamma_{i,j}^{\text{wb-fin}}$ , where  $\gamma_{i,j}^{\text{wb-lp}}$  accounts for lp-carry-in write backs and  $\gamma_{i,j}^{\text{wb-fin}}$  accounts for finished-carry-in and preemption-induced write backs (see Sect. 2.2 for their definitions). In the following we introduce four different ways of computing  $\gamma_{i,j}^{\text{wb-fin}}$ . These combine with the analysis derived for  $\delta_i$  and  $\gamma_{i,j}^{\text{wb-fin}}$  to give the *DCB-Only*, *ECB-Union*, *ECB-Only* and *DCB-Union* approaches for analysing write backs under FPPS.

## 5.1 Initially dirty cache line write backs

We first consider which cache lines may be dirty when the priority level-i busy period starts that leads to the worst-case response time of a job of task  $\tau_i$ . Only tasks of lower priority than  $\tau_i$  may be active immediately before the start of this busy period, so the cache lines in  $\bigcup_{j \in lp(i)} DCB_j$  may all be in the cache and dirty. Further, the cache lines in  $\bigcup_{k \in hep(i)} FDCB_k$  may have been left dirty by finished jobs of higher priority tasks. Among all the dirty cache lines, we need only account for those that may be evicted within  $\tau_i$ 's response time. As only  $\tau_i$  and higher priority tasks can run during this interval, these are  $\bigcup_{k \in hep(i)} ECB_k$ , hence we obtain the following formula for  $\delta_i$ :

$$\delta_{i} = WBT \cdot \left| \left( \bigcup_{j \in lp(i)} DCB_{j} \cup \bigcup_{k \in hep(i)} FDCB_{k} \right) \cap \left( \bigcup_{k \in hep(i)} ECB_{k} \right) \right|$$

(21)

## 5.2 Lower priority carry-in write backs

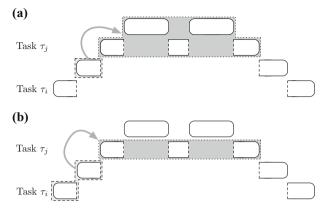

To bound lp-carry-in write backs  $(\gamma_{i,j}^{\text{wb-lp}})$  due to preempted tasks, we identify two methods, both illustrated in Fig. 4.

(a) the lp-carry-in write backs of dirty cache lines introduced by the job *immediately-preempted* by a job of  $\tau_j$  that occur within the response time of  $\tau_j$ , i.e. either executing  $\tau_j$  or a higher priority task.

**Fig. 4** Methods of accounting for lp-carry-in write backs. **a** Effect of immediately-preempted task (light grey) on all preempting tasks (dark grey). **b** Effect of preempted tasks (light grey) on immediately preempting task (dark grey)

(b) the lp-carry-in write backs of dirty cache lines introduced by any preempted lower priority tasks that occur within the execution of a job of  $\tau_i$ .

Using method (a), we define the DCB-Only and ECB-Union approaches, and with method (b), the ECB-Only and DCB-Union approaches.

#### 5.2.1 DCB-Only approach

Using method (a), any task that could be active during the response time of task  $\tau_i$  and has a lower priority than task  $\tau_j$  (i.e. a task in the set  $aff(i, j) = hep(i) \cap lp(j)$ ) could be immediately preempted by task  $\tau_j$ , thus we obtain the following upper bound on the cost of write backs  $\gamma_{i,j}^{\text{wb-lp}}$  associated with jobs of task  $\tau_j$ :

$$\gamma_{i,j}^{\text{wb-lp}} = WBT \cdot \max_{h \in aff(i,j)} |DCB_h|$$

(22)

Note, when using this DCB-Only approach we assume that (21) is simplified ignoring the ECBs.

$$\delta_i = WBT \cdot \left| \bigcup_{j \in lp(i)} DCB_j \cup \bigcup_{k \in hep(i)} FDCB_k \right|$$

(23)

# 5.2.2 ECB-Union approach

The DCB-Only approach can be refined by noting that we are only interested in write backs of these dirty cache lines due to execution of tasks while the job of task  $\tau_j$  is

active, i.e. due to execution of  $\tau_i$  or a higher priority task (see Fig. 4) thus:

$$\gamma_{i,j}^{\text{wb-lp}} = WBT \cdot \max_{h \in aff(i,j)} \left| DCB_h \cap \bigcup_{l \in hep(j)} ECB_l \right|$$

(24)

## 5.2.3 ECB-Only approach

Using method (b), the lp-carry-in write backs of dirty cache lines introduced by *any* preempted lower priority tasks that occur within the execution of  $\tau_j$  are upper bounded by the ECBs of  $\tau_i$ :

$$\gamma_{i,j}^{\text{wb-lp}} = WBT \cdot \left| ECB_j \right| \tag{25}$$

Note, when using this ECB-Only approach we assume that (21) is simplified ignoring the DCBs.

$$\delta_i = WBT \cdot \left| \bigcup_{k \in hep(i)} ECB_k \right| \tag{26}$$

## 5.2.4 DCB-Union approach

The ECB-Only approach can be refined by noting that we are only interested in write backs of dirty cache lines introduced by *preempted lower priority tasks* (see Fig. 4). Note, that we do not need to account for lp-carry-in write backs due to dirty cache lines of tasks of lower priority than  $\tau_i$  as these are already accounted for in  $\delta_i$ .

$$\gamma_{i,j}^{\text{wb-lp}} = WBT \cdot \left| \left( \bigcup_{h \in aff(i,j)} DCB_h \right) \cap ECB_j \right|$$

(27)

## 5.3 Finished-carry-in write backs

A job of task  $\tau_j$  can leave  $|FDCB_j|$  dirty cache lines, which may have to be written back within  $\tau_i$ 's response time. This yields the following simple bound on the cost of finished-carry-in and preemption-induced write backs:

$$\gamma_{i,j}^{\text{wb-fin}} = WBT \cdot |FDCB_j|. \tag{28}$$

One might assume that this bound can be improved by taking into account the evicting cache blocks of other tasks; however, as  $FDCB_j \subseteq ECB_j$ , then without further information, we must assume that the next job of task  $\tau_j$  will have to clean up the final dirty cache lines left by the previous job of the same task, thus no improvement is possible.

Fig. 5 Hasse diagram illustrating the dominance relationships between approaches to account for write backs under fixed-priority preemptive scheduling

By construction, the ECB-Union approach dominates DCB-Only, and the DCB-Union approach dominates ECB-Only. Further, since ECB-Union and DCB-Union are incomparable we may form a combined approach that takes the smallest response time computed by either approach, and hence dominates both. Figure 5 illustrates these relationships via a Hasse diagram.

In some cases there could be pessimism in the analysis for FPPS as a result of write backs that are counted as both job-internal write backs in the WCET of a task, and also as carry-in write backs that occur when a task is preempted and a cache line is written back by the preempting task. As an example consider the sequence of accesses  $c^*$ ,  $c^*$ ,  $c^*$ ,  $d^*$ , where memory blocks  $d^*$  and  $d^*$  are mapped to the same cache line, and  $d^*$  indicates a write. Here the read of  $d^*$  causes a job-internal write back of  $d^*$ . Preemption between the final write to  $d^*$  and the read of  $d^*$  could result in the preempting task writing back  $d^*$  (a carry-in write back), but no job-internal write back. In this case the analysis would over-approximate the total number of write backs. However, preemptions between the writes to  $d^*$  could induce a further carry-in write back in addition to the job-internal one. While there is some over-approximation in the analysis, our evaluations, in the next section, show that this over-approximation is small, with the combined approach close to the upper bound computed without write-back costs.

### 5.4 Worked example

Below, we present a worked example illustrating the various approaches to analysing write backs under fixed-priority preemptive scheduling and their differences in performance. Table 2 gives the task set parameters. (Note the example task set is the same as that used in Sect. 4.3. It is repeated here for ease of reference).

For ease of presentation, we again assume a write-back delay of 1 and choose task parameters so that only one job of each task may be released during another task's response time. The sets of UCBs are assumed to be empty.

In the case of fixed-priority preemptive scheduling, all four approaches use the same response time equation (20), and the same  $\gamma_{i,j}^{\text{wb-fin}}$  terms to account for the finished carry-in write backs (28):  $\gamma_{\_,1}^{\text{wb-fin}} = 1$ ,  $\gamma_{\_,2}^{\text{wb-fin}} = 2$ ,  $\gamma_{\_,3}^{\text{wb-fin}} = 2$ ,  $\gamma_{\_,4}^{\text{wb-fin}} = 1$ . The approaches only differ in the  $\delta_i$  terms to account for initially dirty cache lines and the  $\gamma_{i,j}^{\text{wb-lp}}$  terms.

Table 2 Example task set

| Task               | C   | T    | ECB                    | DCB                    | FDCB   |

|--------------------|-----|------|------------------------|------------------------|--------|

| $\overline{	au_1}$ | 100 | 1000 | {1, 4, 5}              | {1}                    | {1}    |

| $\tau_2$           | 100 | 1000 | {2, 3, 4, 5}           | {2, 3, 4}              | {2, 3} |

| $\tau_3$           | 100 | 1000 | {2, 3, 5}              | {2, 3, 5}              | {2, 3} |

| $	au_4$            | 100 | 1000 | $\{1, 2, 3, 4, 5, 6\}$ | $\{1, 2, 3, 4, 5, 6\}$ | {1}    |

# 5.4.1 DCB-Only

Uses (23) to compute:  $\delta_1 = 6$ ,  $\delta_2 = 6$ ,  $\delta_3 = 6$ ,  $\delta_4 = 3$ .

$$R_1 = 106, R_2 = 210, R_3 = 315, R_4 = 426.$$

# 5.4.2 ECB-Union

Uses (21) to compute:  $\delta_1 = 3$ ,  $\delta_2 = 5$ ,  $\delta_3 = 5$ ,  $\delta_4 = 3$ .

$$R_1 = 103, R_2 = 207, R_3 = 312, R_4 = 421.$$

# 5.4.3 ECB-Only

Uses (26) to compute:  $\delta_1 = 3$ ,  $\delta_2 = 5$ ,  $\delta_3 = 5$ ,  $\delta_4 = 6$ .

$$R_1 = 103, R_2 = 209, R_3 = 315, R_4 = 421.$$

#### 5.4.4 DCB-Union

Uses (21) to compute:  $\delta_1 = 3$ ,  $\delta_2 = 5$ ,  $\delta_3 = 5$ ,  $\delta_4 = 3$ .

$$R_1 = 103, R_2 = 207, R_3 = 313, R_4 = 418.$$

The example shows the dominance relationships of ECB-Union over DCB-Only and DCB-Union over ECB-Only, as well as the incomparability between ECB-Union and DCB-Union. The response time for task  $\tau_3$  is smaller with ECB-Union than with DCB-Union (312 vs. 313). Vice versa, the response time for task  $\tau_4$  is smaller with DCB-Union than with ECB-Union (418 vs. 421). The combined approach, taking the minimum response times (103, 207, 312, 418) thus dominates all others.

# 6 Sustainability of the analysis

The analysis given in this paper builds upon response-time analyses for FPPS and FPNS (see Sects. 3.2 and 3.3 respectively), integrating the effects of write-back costs. The response-time analyses used for FPPS and FPNS are both *sustainable* (Baruah and Burns 2006), meaning that a system that is deemed schedulable by the schedulability test used will not become unschedulable or be deemed unschedulable by the test if the task parameters are *improved*. These improvements include (i) reduced execution times, (ii) increased periods or minimum inter-arrival times, and (iii) increased deadlines.

We note that with the integration of write-back costs and CRPD given in Sects. 4 and 5, sustainability still holds with respect to the above parameters. Further, the analysis is sustainable with respect to improvements in the sets of cache lines considered, i.e. ECBs, DCBs, and FDCBs. (Here, by improvement we mean removal of one or more elements from a set, such that the new set is a subset of the old). This can be seen from the formulaes involved, since the response times computed are monotonically non-decreasing with respect to increases (addition of elements) to any of these sets. In all of the equations given in Sects. 4 and 5, for the overheads of write backs, the ECBs, DCBs, and FDCBs are combined using union, intersection, and cardinality operators. Thus the overheads are monotonically non-decreasing with respect to the content of those sets, and so any response time  $R'_i$  computed using  $ECB'_j$ ,  $DCB'_j$ ,  $FDCB'_j$  is no smaller than  $R_i$  computed using  $ECB_j$ ,  $DCB_j$ ,  $FDCB_j$  where  $ECB'_j \supseteq ECB_j$ ,  $DCB'_i \supseteq DCB_j$ , and  $FDCB'_i \supseteq FDCB_j$ . The only exception that requires further consideration occurs in the FDCB-Union approach (Sect. 4.1) where (9) makes use of the set subtraction operator. Here, any reduction in the value of  $\delta_i$  due to an additional element in  $FDCB_k$  where  $k \in hp(i)$  is matched by an increase in  $\gamma_{i,j}^{\text{wb}}$  given by (10) for at least one of the higher priority tasks in hp(i). Since each  $\gamma_{i,i}^{\text{wb}}$  term for a higher

priority task is included in the response time equation (11) at least once, the computed response time cannot decrease with the addition of any element to  $FDCB_i$ .

# 7 Experimental evaluation

In this section, we evaluate the performance of the different analyses introduced in Sects. 4 and 5 for write-back caches under fixed-priority preemptive and non-preemptive scheduling, as compared to no cache and a write-through cache. For both write-back and write-through caches, we assumed a write-allocate policy. Preliminary experiments showed that the difference between write allocate and no-write allocate for a write-through cache were minimal, with the former giving slightly better performance on the benchmarks studied.

We assume a timing-compositional processor with separate instruction and data caches. Each cache is direct-mapped and has 512 cache lines of size 32 bytes. Thus both caches have a capacity of 16 KB. Further, we assume a write-back latency *WBT* of 10 cycles. Cache misses also take 10 cycles, while non-memory instructions and cache hits take 1 cycle.

As a *proof-of-concept* for the analysis techniques, we obtained realistic estimates for WCETs and the sets of DCBs and ECBs, from the Mälardalen benchmark suite (Gustafsson et al. 2010) and the EEMBC Benchmark suite (EEMBC 2016) (Sect. 9 explains how this was done). Table 3 shows the WCETs (without inter-task interference) assuming a write-back cache ( $C^{\rm wb}$ ), a write-through cache ( $C^{\rm wt}$ ), and no data cache ( $C^{\rm nc}$ ) for the selected benchmarks. Table 4 shows the number of UCBs, ECBs, DCBs, and FDCBs. We note that these stand-alone WCETs are a substantial factor of 1.4 to 3.0 times lower with a write-back cache than with write through, and 2 to 9 times lower than with no data cache. Since we assume a separate instruction and data cache, the UCB and ECB values are shown separately for each cache.

We note that fixed-priority non-preemptive scheduling suffers from the long task problem, whereby task sets that contain some tasks with short deadlines and others with long WCETs are trivially unschedulable due to blocking. To ameliorate this problem, we only selected benchmarks for Table 4 where the stand-alone WCETs were in the range [7000:70,000] cycles. This interval corresponds to the most populated range where the smallest and largest WCETs differ by a factor of 10. This restriction has little effect on the results for FPPS, while also providing task sets that can actually be scheduled using FPNS.

We evaluated the guaranteed performance of the various approaches on a large number of randomly generated task sets (10,000 per utilization level for the baseline experiments, and 200 per level for the weighted schedulability (Bastoni et al. 2010)) experiments. The task set parameters were generated as follows:

- The default task set size was 10.

- Each task was assigned data from a randomly chosen row of Table 4, corresponding to code from the benchmarks.

- The task utilizations  $(U_i)$  were generated using UUnifast (Bini and Buttazzo 2005).

- Task periods were set based on utilization and the stand-alone WCET for a write-back cache, i.e.,  $T_i = C_i^{\text{wb}}/U_i$ .

| Table 3 | Data from t | he Mälardalen | and EEMBC ber    | nchmarks used t   | for evaluation |

|---------|-------------|---------------|------------------|-------------------|----------------|

| Table 3 | Data mom t  | He Maiardalen | and deliving del | nciiniarks useu i | OI EVAIUALIOII |

| Name      | $ UCB^I $ | $ ECB^I $ | $ UCB^D $ | $ ECB^D $ | DCB | FDCB |

|-----------|-----------|-----------|-----------|-----------|-----|------|

| cnt       | 12        | 82        | 21        | 68        | 28  | 28   |

| compress  | 21        | 71        | 53        | 103       | 60  | 60   |

| countneg  | 15        | 77        | 59        | 103       | 66  | 66   |

| crc       | 19        | 89        | 25        | 73        | 40  | 39   |

| expint    | 16        | 76        | 11        | 42        | 13  | 13   |

| fdct      | 52        | 144       | 15        | 48        | 19  | 19   |

| fir       | 22        | 83        | 17        | 57        | 17  | 16   |

| jfdctint  | 46        | 145       | 17        | 53        | 23  | 23   |

| loop3     | 7         | 309       | 9         | 42        | 12  | 12   |

| ludcmp    | 38        | 128       | 21        | 61        | 28  | 28   |

| minver    | 103       | 213       | 18        | 71        | 33  | 33   |

| ns        | 14        | 70        | 9         | 116       | 13  | 11   |

| nsichneu  | 345       | 494       | 52        | 95        | 54  | 53   |

| qurt      | 61        | 132       | 14        | 49        | 17  | 17   |

| select    | 47        | 124       | 10        | 49        | 16  | 16   |

| sqrt      | 51        | 102       | 11        | 48        | 16  | 16   |

| statemate | 92        | 167       | 25        | 68        | 21  | 20   |

| a2time    | 16        | 122       | 8         | 100       | 69  | 67   |

| aifirf    | 25        | 141       | 33        | 188       | 161 | 54   |

| basefp    | 11        | 88        | 15        | 512       | 507 | 467  |

| canrdr    | 8         | 40        | 9         | 371       | 195 | 186  |

| iirflt    | 35        | 288       | 28        | 259       | 147 | 138  |

| pntrch    | 24        | 38        | 20        | 237       | 176 | 70   |

| puwmod    | 3         | 50        | 5         | 512       | 307 | 275  |

| rspeed    | 8         | 53        | 7         | 122       | 71  | 70   |

| tblook    | 12        | 115       | 14        | 125       | 71  | 71   |

- Task deadlines were implicit  $D_i = T_i$ .

- Task priorities were in deadline-monotonic order.

- Tasks were placed in memory sequentially in priority order, thus determining the direct mapping to cache.

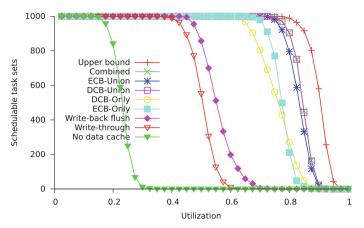

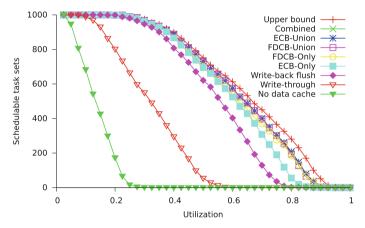

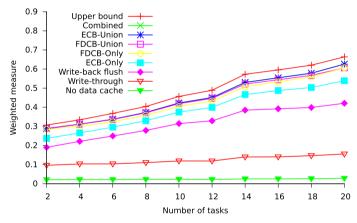

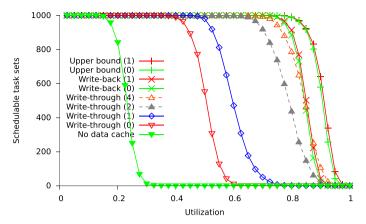

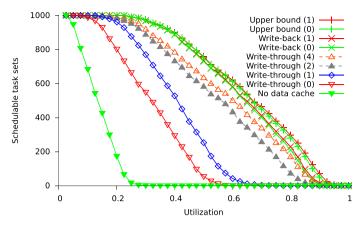

Figures 6 and 7 show the baseline results for FPPS and FPNS respectively (the graphs are best viewed online in colour). Table 5 summarises these results using the weighted schedulability measure (Bastoni et al. 2010).

Additional experimental results showing how this measure varies with the number of tasks and with the memory latency are given in the next subsection on weighted schedulability.

The lines in the figures correspond to the four different approaches, plus the combined approach, along with results for a write-through data cache and a system with no data cache. The first line refers to an optimistic *upper bound* where we assumed

Table 4 WCETs from the Mälardalen and EEMBC benchmarks used for evaluation

| Name      | $C^{\mathrm{wb}}$ | $C^{ m wt}$ | $C^{\mathrm{wt}}/C^{\mathrm{wb}}$ | $C^{\mathrm{nc}}$ | $C^{\rm nc}/C^{\rm wb}$ |

|-----------|-------------------|-------------|-----------------------------------|-------------------|-------------------------|

| cnt       | 9325              | 13485       | 1.44                              | 24565             | 2.63                    |

| compress  | 10673             | 18713       | 1.75                              | 43443             | 4.07                    |

| countneg  | 36180             | 57250       | 1.58                              | 114340            | 3.16                    |

| crc       | 68889             | 133909      | 1.94                              | 272859            | 3.96                    |

| expint    | 9268              | 15208       | 1.64                              | 31098             | 3.35                    |

| fdct      | 7883              | 16793       | 2.13                              | 38423             | 4.87                    |

| fir       | 8328              | 18998       | 2.28                              | 43668             | 5.24                    |

| jfdctint  | 9711              | 18621       | 1.91                              | 39181             | 4.03                    |

| loop3     | 14189             | 28729       | 2.02                              | 57929             | 4.08                    |

| ludemp    | 10058             | 15948       | 1.58                              | 39668             | 3.94                    |

| minver    | 18976             | 30616       | 1.61                              | 54746             | 2.88                    |

| ns        | 27464             | 37674       | 1.37                              | 98634             | 3.59                    |

| nsichneu  | 18988             | 24458       | 1.28                              | 66808             | 3.51                    |

| qurt      | 10473             | 16003       | 1.52                              | 23573             | 2.25                    |

| select    | 8981              | 17031       | 1.89                              | 30331             | 3.37                    |

| sqrt      | 27667             | 40537       | 1.46                              | 59117             | 2.13                    |

| statemate | 64638             | 195778      | 3.02                              | 581908            | 9.00                    |

| a2time    | 12655             | 22975       | 1.81                              | 53815             | 4.25                    |

| aifirf    | 44898             | 86768       | 1.93                              | 181698            | 4.04                    |

| basefp    | 50491             | 92221       | 1.82                              | 213771            | 4.23                    |

| canrdr    | 32641             | 65211       | 1.99                              | 156611            | 4.79                    |

| iirflt    | 29995             | 56995       | 1.90                              | 127605            | 4.25                    |

| pntrch    | 23887             | 43137       | 1.80                              | 109257            | 4.57                    |

| puwmod    | 48782             | 97072       | 1.98                              | 239752            | 4.91                    |

| rspeed    | 10913             | 21393       | 1.96                              | 51713             | 4.73                    |

| tblook    | 12533             | 25493       | 2.03                              | 58813             | 4.69                    |

the stand-alone WCETs for write-back caches, but without any cost for write backs. This line upper bounds the performance of any sound analysis for write-back caches, and thus gives an indication of the precision of the analyses introduced in this paper.

The line *write-back flush* corresponds to a pessimistic analysis for write-back caches. In the case of FPNS, this analysis assumes that the entire cache is dirty and is flushed (written back) at the start of each task. To account for this, the WCET for each task is increased by  $N \cdot WBT$ , where N is the number of caches lines (e.g. 512) and WBT is the time to write back one cache line (e.g. 10 cycles). In the case of FPPS, not only could the entire cache be dirty and require writing back at the start of each preempting task, it could also be dirty at the end of each preemption and so also require writing back by the preempted task. The *write-back flush* analysis for FPPS therefore assumes that the entire cache is dirty and is flushed (written back) at both the start and at the end of each task. To account for this, the WCET for each task is increased

Fig. 6 Number of schedulable task sets (FPPS)

Fig. 7 Number of schedulable task sets (FPNS)

**Table 5** Weighted schedulability measure for FPNS and FPPS

| Approach                 | FPPS     | FPNS     |

|--------------------------|----------|----------|

| Write-back (upper bound) | 0.793458 | 0.445750 |

| Combined                 | 0.693003 | 0.412270 |

| (F)DCB-Union             | 0.692087 | 0.411087 |

| ECB-Union                | 0.672489 | 0.396159 |

| (F)DCB-Only              | 0.561542 | 0.396159 |

| ECB-Only                 | 0.581876 | 0.365523 |

| Write-back (flush)       | 0.304987 | 0.305039 |

| Write-through            | 0.249231 | 0.112666 |

| No data cache            | 0.052548 | 0.021463 |

|                          |          |          |

by  $2N \cdot WBT$ . The results for *write-back flush* lower bound any useful analysis for a write-back cache.

For preemptive scheduling, in *all* cases, we include the cost of additional cache misses due to CRPD using the UCB-Union approach (Altmeyer et al. 2012).

The results shown in Figs. 6 and 7 indicate that the guaranteed performance obtained for write-back caches using the analyses introduced in this paper exceeds that which can be obtained for write-through caches. The new methods also provide a substantial improvement over the pessimistic *write-back flush* analysis, which in turn has an advantage over analysis for write-through caches. This shows that the gain from using a write-back cache comes from a combination of reduced WCETs and accurate analysis.

Further, the *upper bound* line indicates that the combined approaches used to analyse write-back cache offer a high degree of precision.

In Figs. 6 and 7 the ECB-Union approaches are outperformed by DCB-Union and FDCB-Union respectively. We note that this is not always the case as shown by the worked example in Sects. 5.4 and 4.3. In our experiments, the performance of the DCB-Union approach for FPPS and the FDCB-Union approach for FPNS is close to that of the associated combined approach. The reason for this is the relatively weak performance of the ECB-Union approach in each case. This occurs because the sets of ECBs for the benchmark tasks are substantially larger than the sets of DCBs and FDCBs. This degrades the relative performance of the ECB-Union approaches, particularly for low priority tasks which are the most critical to task set schedulability. (For a low priority task, the union of ECBs over all higher priority tasks may well cover all of the cache).

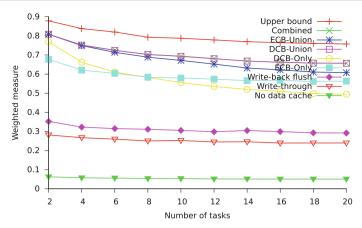

## 7.1 Weighted schedulability

The weighted schedulability measure  $W_y(p)$  for a schedulability test y and parameter p, combines results for all task sets generated for a set of equally spaced utilization levels (e.g. from 0.025 to 0.975 in steps of 0.025). Let  $S_y(\tau, p)$  be the binary result (1 or 0) of schedulability test y for a task set  $\tau$  assuming parameter p.

$$W_{y}(p) = \left(\sum_{\forall \tau} u(\tau) \cdot S_{y}(\tau, p)\right) / \sum_{\forall \tau} u(\tau)$$

(29)

where  $u(\tau)$  is the utilization of task set  $\tau$ . Weighting the results by task set utilization reflects the higher value placed on being able to schedule higher utilization task sets.

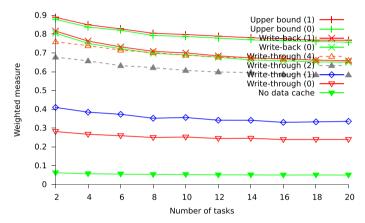

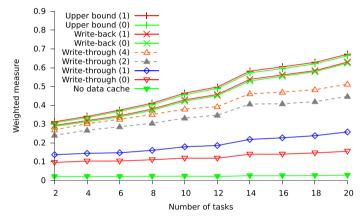

Figures 8 and 9 show how the weighted schedulability measure varies with task set size for FPPS and FPNS respectively. With preemptive scheduling, the relative performance of the different approaches remains consistent, with an overall gradual decline in schedulability as the number of tasks increases. This is due to an increase in the number of tasks increasing the number of preemptions and to some degree also their cost. (With FPPS, it is also simply harder to schedule task sets with increasing numbers of tasks, even without considering overheads).

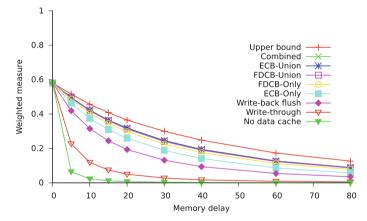

With FPNS, as the number of tasks increases, the WCET of each task in relation to its period and deadline tends to decrease. This enables an overall increase in schedulability

Fig. 8 Weighted schedulability versus number of tasks (FPPS)

Fig. 9 Weighted schedulability versus number of tasks (FPNS)

with a write-back cache; however, at the very low level of schedulability achieved by write-through cache and no cache, schedulability is more dependent on a random choice of tasks with similar WCETs and hence similar deadlines, which avoid the long task problem. This becomes rarer with more tasks counteracting the previous effect.

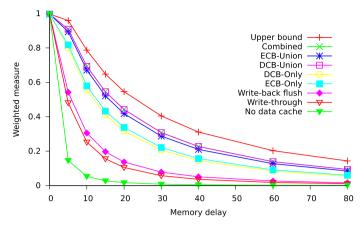

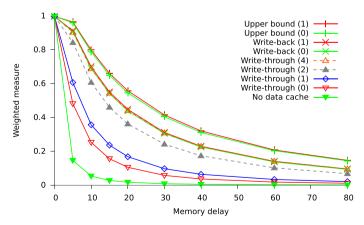

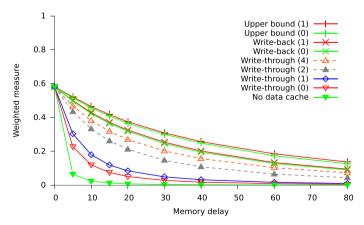

Figures 10 and 11 show how the weighted schedulability measure varies with memory delay (time for write back or write through) for FPPS and FPNS respectively. Both figures show that as expected, increasing the memory delay has a detrimental effect on schedulability. As the memory delay increases, the larger number of writes to memory with a write-through cache becomes more heavily penalized and the relative performance of that approach (and no cache) deteriorates rapidly. We observe that for the benchmarks studied in our experiments, the guaranteed performance obtained with a write-back cache under FPPS was similar to that for a write-through cache when the latter was used on a higher performance system with one quarter of the memory delay

Fig. 10 Weighted schedulability versus memory latency (FPPS)

Fig. 11 Weighted schedulability versus memory latency(FPNS)

(e.g. 20 vs. 5 cycles, 40 vs. 10 cycles, or 80 vs. 20 cycles). For FPNS, where long task execution times have an increased impact on schedulability, the difference was even more stark, with the guaranteed performance obtained with a write-back cache with a memory delay of 40 cycles similar to that with a write-through cache with a delay of 5 cycles.

## 8 Write buffers

In this section, we discuss *write buffers* and their use, predominantly in improving the performance of write-through caches. At the end of the section we discuss the use of write buffers for write-back caches.

The key performance issue with a write-through cache is that the processor can potentially stall each time there is a write access, i.e. it may have to wait until the write to memory completes before continuing with subsequent instructions. This problem

can, to a large extent, be remedied via the use of a *write buffer*. A write buffer is a small buffer that operates between the cache and main memory. It holds data that is waiting to be written to memory. When a write occurs, the address and data (block) are placed in the write buffer. This allows the processor to continue with subsequent instructions, while the write to memory occurs in parallel via the write buffer.

Write buffers are characterized by a *depth* (indicating the number of entries), and a *width* (which is typically the same as a cache line), as well as the policies defining their operation. These policies include: (i) the *local-hazard* policy, which determines what happens when a read access occurs to an address that is currently in the write buffer; (ii) the *coalescence policy*, which determines what happens when a write access occurs to an address that is currently in the write buffer, and finally (iii) the *retirement policy*, which determines when write buffer entries are retired, i.e. written to memory. We discuss these policies in more detail below. (The interested reader is also referred to the work of Skadron and Clark (1997), which discusses write buffer design from the perspective of improving average-case performance).

## 8.1 Local hazard policy

Care is needed in the design of a write buffer, since a naive design could potentially result in data inconsistency, termed a *local hazard*, as follows: If a read occurs which is a cache miss, but the data is in the write buffer waiting to be written to memory, then reading from memory could result in an inconsistent value being obtained. To avoid this hazard there are two possible options that we consider (i) *read from the write buffer* or (ii) *full flush of the write buffer* and then read from memory. (More complex schemes are possible, such as flushing the write buffer only as far as necessary to write the required data to memory, or flushing only the specific item. They are not considered here).

# 8.2 Coalescence policy

Entries in a write buffer consist of an address and a block of data. The latter is typically the same size as a cache line. When a write occurs and there are no entries in the write buffer, then the block of data is copied to the write buffer and the specific word that is being written is marked as valid via a flag bit. The flag bit indicates that the word should later be written to memory.

If a write occurs to an address that is already in an entry in the write buffer then it could potentially be coalesced. In this case the entry containing the address is found in the buffer and the appropriate word of data is updated and marked as valid. We refer to this mechanism as *write merge*. Merging writes in this way has the advantage that it enables multiple writes to the same address or to the same block to be coalesced, resulting in fewer writes to memory. The write-merge mechanism has similarities to a write-back cache, in that it takes advantage of the spacial locality of writes. Merging writes also makes better use of the limited capacity of the write buffer.

The alternative to merging writes is to simply add a new entry to the write buffer on each write. This still facilitates latency hiding, since the processor is able to continue