This is a repository copy of *On the analysis of random replacement caches using static probabilistic timing methods for multi-path programs*.

White Rose Research Online URL for this paper: <a href="https://eprints.whiterose.ac.uk/125897/">https://eprints.whiterose.ac.uk/125897/</a>

Version: Published Version

#### Article:

Lesage, Benjamin Michael Jean-Rene, Griffin, David Jack orcid.org/0000-0002-4077-0005, Altmeyer, Sebastian et al. (2 more authors) (2018) On the analysis of random replacement caches using static probabilistic timing methods for multi-path programs. Real-Time Systems. pp. 307-388. ISSN 1573-1383

https://doi.org/10.1007/s11241-017-9295-2

# Reuse

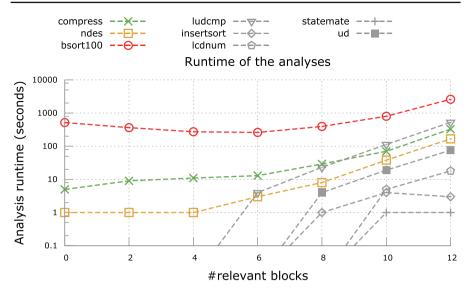

Items deposited in White Rose Research Online are protected by copyright, with all rights reserved unless indicated otherwise. They may be downloaded and/or printed for private study, or other acts as permitted by national copyright laws. The publisher or other rights holders may allow further reproduction and re-use of the full text version. This is indicated by the licence information on the White Rose Research Online record for the item.

# **Takedown**

If you consider content in White Rose Research Online to be in breach of UK law, please notify us by emailing eprints@whiterose.ac.uk including the URL of the record and the reason for the withdrawal request.

# On the analysis of random replacement caches using static probabilistic timing methods for multi-path programs

Benjamin Lesage¹ · David Griffin¹ · Sebastian Altmeyer² · Liliana Cucu-Grosjean³ · Robert I. Davis¹,³ ₪

© The Author(s) 2017. This article is an open access publication

**Abstract** Probabilistic hard real-time systems, based on hardware architectures that use a random replacement cache, provide a potential means of reducing the hardware over-provision required to accommodate pathological scenarios and the associated extremely rare, but excessively long, worst-case execution times that can occur in deterministic systems. Timing analysis for probabilistic hard real-time systems requires the provision of probabilistic worst-case execution time (pWCET) estimates. The pWCET distribution can be described as an exceedance function which gives an upper bound on the probability that the execution time of a task will exceed any given execution time budget on any particular run. This paper introduces a more effective static probabilistic timing analysis (SPTA) for multi-path programs. The analysis estimates the temporal contribution of an evict-on-miss, random replacement cache to the pWCET distribution of multi-path programs. The analysis uses a conservative join function that provides a proper over-approximation of the possible cache contents and the pWCET

☑ Benjamin Lesage benjamin.lesage@york.ac.uk

David Griffin david.griffin@york.ac.uk

Sebastian Altmeyer altmeyer@uva.nl

Liliana Cucu-Grosjean liliana.cucu@inria.fr

Robert I. Davis rob.davis@york.ac.uk

University of York, York, UK

Published online: 18 December 2017

- <sup>2</sup> University of Amsterdam, Science Park 904, Room C3.101, 1098 XH, Amsterdam, Netherlands

- 3 INRIA, Paris, France

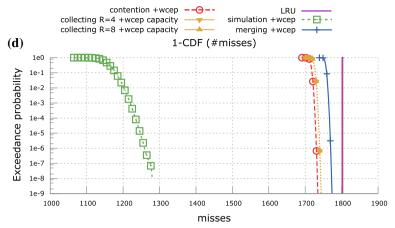

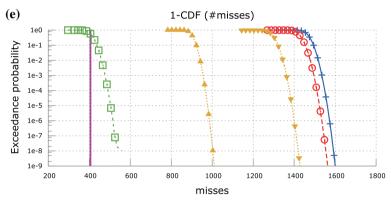

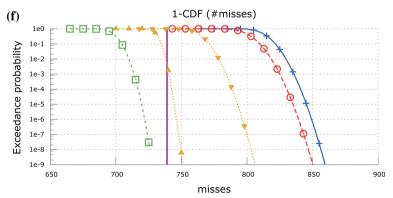

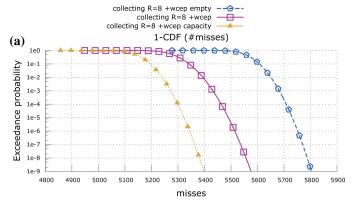

distribution on path convergence, irrespective of the actual path followed during execution. Simple program transformations are introduced that reduce the impact of path indeterminism while ensuring sound pWCET estimates. Evaluation shows that the proposed method is efficient at capturing locality in the cache, and substantially outperforms the only prior approach to SPTA for multi-path programs based on path merging. The evaluation results show incomparability with analysis for an equivalent deterministic system using an LRU cache. For some benchmarks the performance of LRU is better, while for others, the new analysis techniques show that random replacement has provably better performance.

**Keywords** Cache analysis · Probabilistic timing analysis · Random replacement policy · Multi-path

#### **Extensions**

This paper builds upon previous work published in RTSS 2015 (Lesage et al. 2015a) with the following extensions:

- we introduce and prove additional properties relevant to the comparison of the contribution of different cache states to the probabilistic worst-case execution time of tasks in Sect. 3:

- an improved join transfer function, used to safely merge states from converging paths, is introduced in Sect. 5 and by construction dominates the simple join introduced in Lesage et al. (2015a);

- we present and prove the validity of path renaming in Sect. 6 which allows the definition of additional transformations to reduce the set of paths considered during analysis;

- our evaluation explores new configurations in terms of both the analysis methods used and the benchmarks considered (see Sect. 7).

#### 1 Introduction

Real-time systems such as those deployed in space, aerospace, automotive and railway applications require guarantees that the probability of the system failing to meet its timing constraints is below an acceptable threshold (e.g. a failure rate of less than  $10^{-9}$  per hour for some aerospace and automotive applications). Advances in hardware technology and the large gap between processor and memory speeds, bridged by the use of cache, make it difficult to provide such guarantees without significant overprovision of hardware resources.

The use of deterministic cache replacement policies means that pathological worst-case behaviours need to be accounted for, even when in practice they may have a vanishingly small probability of actually occurring. The use of cache with a random replacement policy means that the probability of pathological worst-case behaviours can be upper bounded at quantifiably extremely low levels, for example well below the maximum permissible failure rate (e.g.  $10^{-9}$  per hour) for the system. This allows

the extreme worst-case behaviours to be safely ignored, instead of always included in the estimated worst-case execution times.

The random replacement policy further offers a trade-off between performance and cost thanks to a minimal hardware cost (Al-Zoubi et al. 2004). The policy and variants have been implemented in a selection of embedded processors (Hennessy and Patterson 2011) such as the ARM Cortex series (2010), or the Freescale MPC8641D (2008). Randomisation further offers some level of protection against side-channel attacks which allow the leakage of information regarding the running tasks. While methods relying solely on the random replacement policy may still be circumvented (Spreitzer and Plos 2013), the definition of probabilistic timing analysis is a step towards the analysis of other approaches such as randomised placement policies (Wang and Lee 2007; 2008).

The timing behaviour of programs running on a processor with a cache using a random replacement policy can be determined using static probabilistic timing analysis (SPTA). SPTA computes an upper bound on the probabilistic Worst-Case Execution Time (pWCET) in terms of an exceedance function. This exceedance function gives the probability, as a function of all possible values for an execution time budget x, that the execution time of the program will exceed that budget on any single run. The reader is referred to Davis et al. (2013) for examples of pWCET distributions, and to Cucu-Grosjean (2013) for a detailed discussion of what is meant by a pWCET distribution.

This paper introduces an effective SPTA for *multi-path* programs running on hardware that uses an evict-on-miss, random replacement cache. Prior work on SPTA for multi-path programs by Davis et al. (2013) used a path merging approach to compute cache hit probabilities based on reuse distances. The analysis derived in this paper builds upon more sophisticated SPTA techniques for the analysis of single path programs given by Altmeyer and Davis (2014, 2015). This new analysis provides substantially improved results compared to the path merging approach. To allow the analysis of the behaviour of caches in isolation, we assume the existence of a valid decomposition of the architecture with regards to cache effects with bounded hit and miss latencies (Hahn et al. 2015).

#### 1.1 Related work

We now set the work on SPTA in context with respect to related work on both probabilistic hard real-time systems and cache analysis for deterministic replacement policies. The methods introduced in this paper belong to the realm of analyses that estimate bounds on the execution time of a program. These bounds may be classified as either a worst-case probability distribution (pWCET) or a worst-case value (WCET).

The first class is a more recent research area with the first work on providing bounds described by probability distributions published by Edgar and Burns (2000, 2001). The methods for obtaining such distributions can be categorised into three different families: measurement-based probabilistic timing analyses, static probabilistic timing analyses, and hybrid probabilistic timing analyses.

The second class is a mature area of research and the interested reader may refer to Wilhelm et al. (2008) for an overview of these methods. A specific overview of cache analysis for deterministic replacement policies together with a comparison between deterministic and random cache replacement policies is provided at the end of this section.

#### 1.1.1 Probabilistic timing analyses

Measurement-based probabilistic timing analyses (Bernat et al. 2002; Cucu-Grosjean et al. 2012) collect observations on the execution time of the task under study on the target hardware. These observations are then combined, e.g. through the use of extreme value theory (Cucu-Grosjean et al. 2012), to produce the desired worst-case probabilistic timing estimate. Extreme Value Theory may potentially underestimate the pWCET of a program as shown by Griffin and Burns (2010). The work of Cucu-Grosjean et al. (2012) overcomes this limitation and also introduces the appropriate statistical tests required to treat worst-case execution times as rare events. The soundness of the results produced by such methods is tied to the observed execution times which should be representative of the ones at runtime. This implies a responsibility on the user who is expected to provide input data to exercise the worst-case paths, less the analysis results in unsound estimates (Lesage et al. 2015b). These methods nonetheless exhibit the benefits of time-randomised architectures. The occurrence probability of pathological temporal cases can be bounded and safely ignored provided they meet requirements expressed in terms of failure rates.

Path upper-bounding (Kosmidis et al. 2014) defines a set of program transformations to alleviate the responsibility of the user to provide inputs which cover all execution paths. The alternative paths of conditional constructs are padded with semantic-preserving instructions and memory accesses such that any path followed in the modified program is an upper-bound of any of the original alternatives. Measurement-based analyses can then be performed on the modified program as the paths exercised at runtime upper-bound any alternative in the original application. Hence, upper-bounding creates a distinction between the original code and the measured one. It may also result in paths which are the sum of the original alternatives.

Hybrid probabilistic timing analyses are methods that apply measurement-based methods at the level of sub-programs or blocks of code and then operations such as convolution to combine these bounds to obtain a pWCET for the entire program. The main principles of hybrid analysis were introduced by Bernat et al. (2002, 2003) with execution time probability distributions estimated at the level of sub-programs. Here, dependencies may exist among the probability distributions of the sub-programs and copulas are used to describe them (Bernat et al. 2005).

By contrast, SPTAs derive the pWCET distribution for a program by analysing the structure of the program and modelling the behaviour of the hardware it runs on. Existing work on SPTA has primarily focussed on randomized architectures containing caches with random replacement policies. Initial results for the evict-on-miss (Quinones et al. 2009) and evict-on-access (Cucu-Grosjean et al. 2012; Cazorla et al. 2013) policies were derived for single-path programs. These methods use the *reuse distance* of each access to determine its probability of being a cache hit. These results

were superseded by later work by Davis et al. (2013) who derived an optimal lower bound on the probability of a cache hit under the evict-on-miss policy, and showed that evict-on-miss dominates evict-on-access. Altmeyer and Davis (2014) proved the correctness of the lower bound derived in Davis et al. (2013), and its optimality with regards to the limited information that it uses (i.e. the reuse distance). They also showed that the probability functions previously given in Kosmidis et al. (2013) and Quinones et al. (2009) are unsound (optimistic) for use in SPTA. In 2013, a simple SPTA for multipath programs was introduced by Davis et al. (2013), based on path merging. With this method, accesses are represented by their reuse distances. The program is then virtually reduced to a single sequence which upper-bounds all possible paths with regards to the reuse distance of their accesses.

In 2014, more sophisticated SPTA methods for single path programs were derived by Altmeyer and Davis (2014). They introduced the notion of cache contention, which combined with reuse distance enables the computation of a more precise bound on the probability that a given access is a cache hit. Altmeyer and Davis (2014) also introduced a significantly more effective method based on combining exhaustive evaluation of the cache behaviour for a limited number of *relevant* memory blocks with cache contention. This method provides an effective trade-off between analysis precision and tractability. Griffin et al. (2014a) introduces orthogonal Lossy compression methods on top of the cache states enumeration to improve the trade-off between complexity and precision.

Altmeyer and Davis further refined their approach to SPTA for single path programs in 2015 (Altmeyer et al. 2015), bridging the gap between contention and enumeration-based analyses. The method relies on simulation of the behaviour of a random replacement cache. As opposed to exhaustive state analyses however, focus is set at each step on a single cache state to capture the outcome across all possible states. The resulting approach offers an improved precision over contention-based methods, at a lower complexity than exhaustive state analyses.

In this paper, we build upon the state-of-the-art approach (Altmeyer and Davis 2014), extending it to multi-path programs. The techniques introduced in the following notably allow for the identification on control flow convergence of relevant cache contents, i.e. the identification of the outcomes in multi-path programs. The approach focuses on the enumeration of possible cache states at each point in the program. To reduce the complexity of such an approach, only a few blocks, identified as the most relevant, are analysed at a given time.

#### 1.1.2 Deterministic architectures and analyses

Static timing analysis for deterministic caches (Wilhelm et al. 2008) relies on a two step approach with a low-level analysis to classify the cache accesses into hits and misses (Theiling et al. 1999) and a high-level analysis to determine the length of the worst-case path (Li and Malik 2006). The most common deterministic replacement policies are least-recently used (LRU), first-in first-out (FIFO) and pseudo-LRU (PLRU). Due to the high-predictability of the LRU policy, academic research typically focusses on LRU caches—with a well-established LRU cache analysis based on abstract interpretation (Alt et al. 1996; Theiling et al. 1999). Only recently, analyses for FIFO (Grund and

Reineke 2010) and PLRU (Grund and Reineke 2010; Griffin et al. 2014b) have been proposed, both with a higher complexity and lower precision than the LRU analysis due to specific features of the replacement policies. Despite the focus on LRU caches and its analysability, FIFO and PLRU are often preferred in processor designs due to the lower implementation costs which enable higher associativities.

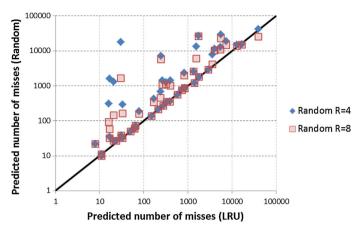

Recently, Reineke (2014) observed that SPTA based on reuse distances (Davis et al. 2013) results, by construction, in less precise bounds than existing analyses based on stack distance for an equivalent system with a LRU cache (Wilhelm et al. 2008). However, this does not hold for the more sophisticated SPTA based on cache contention and collecting semantics given by Altmeyer and Davis (2014). Analyses for deterministic LRU caches are incomparable with these analyses for random replacement caches. This is illustrated by our evaluation results. It can also be seen by considering simple examples such as a repeated sequence of accesses to five memory blocks  $\langle a, b, c, d, e, a, b, c, d, e \rangle$  with a four-way associative cache. With LRU, no hits can be predicted. By contrast, with a random replacement cache and SPTA based on cache contention, four out of the last five accesses can be assumed to have a non-zero probability of being a cache hit (as shown in Table 1 of Altmeyer and Davis 2014), hence SPTA for a random replacement cache outperforms analysis of LRU in this case. We note that in spite of recent efforts (de Dinechin et al. 2014) the stateless random replacement policies have lower silicon costs than LRU, and so can potentially provide improved real-time performance at lower hardware cost.

Early work (David and Puaut 2004; Liang and Mitra 2008) in the domain of SPTA for *deterministic* architectures relied for its correctness on knowledge of the probability that a specific path would be taken or that specific input data would be encountered; however, in general such assumptions may not be available. The analysis given in this paper does not require any assumption about the probability distribution of different paths or inputs. It relies only on the *random* selection of cache lines for replacement.

# 1.2 Organisation

In this paper, we introduce a set of methods that are required for the application of SPTA to multi-path programs. Section 2 recaps the assumptions and methods upon which we build. These were used in previous work (Altmeyer and Davis 2014) to upper-bound the pWCET distribution of a trace corresponding to a single path program. We then proceed by defining key properties which allows the ordering of cache states w.r.t. their contribution to the pWCET of a program (Sect. 3). We address the issue of multi-path programs in the context of SPTA in Sect. 4. This includes the definition of conservative (over-approximate) join functions to collect information regarding cache contention, possible cache contents, and the pWCET distribution at each program point, irrespective of the path followed during execution. Further improvements on cache state conservation at control flow convergence are introduced in Sect. 5. Section 6 introduces simple program transformations which improve the precision of the analysis while ensuring that the pWCET distribution of the transformed program remains sound (i.e. upper-bounds that of the original). Multi-path SPTA is applied to a selection of benchmarks in Sect. 7 and the precision and run-time of the different approaches

compared. Section 8 concludes with a summary of the main contributions of the paper and a discussion of future work.

# 2 Static probabilistic timing analysis

In this section, we recap on state-of-the-art SPTA techniques for single path programs (Altmeyer and Davis 2014). We first give an overview of the system model assumed throughout the paper in Sect. 2.1. We further recap on the existing methods (Altmeyer and Davis 2014) to evaluate the pWCET of a single path trace using a collecting approach (Sect. 2.2) supplemented by a contention one. The pertinence of the model is discussed at the end of this section. The notations introduced in the present contributions have been summarised in Table 1.

We assume an architecture for which a valid decomposition exists with regards to the cache, such that its timing contribution can be analysed in isolation from other components (Hahn et al. 2015). Further, the overall execution time penalty emanating from cache misses and hits are assumed to be bounded by the latencies assumed by the analysis. Thus a local worst-case, a miss in the context of the cache, can be added to the local worst-case for other components to obtain a bound on the global worst case (Reineke et al. 2006). This enables analysis of the impact of the cache in isolation from other architectural features.

#### 2.1 Cache model

We assume a single level, private, N-way fully-associative cache with an evict-on-miss random replacement policy. On an access, should the requested memory block be absent from the cache then the contents of a randomly selected cache line are evicted. The requested memory block is then loaded into the selected location. Given that there are N ways, the probability of any given cache line being selected by the replacement policy is  $\frac{1}{N}$ . We assume a fixed upper-bound on the hit and miss latencies, denoted by  $\mathcal H$  and  $\mathcal M$  respectively, such that  $\mathcal H < \mathcal M$ . (We note that the restriction to a fully-associative cache can be easily lifted for a set-associative cache through the analysis of each cache set as an independent fully-associative cache.)

#### 2.2 Collecting semantics

We now recap on the collecting semantics introduced by Altmeyer and Davis (2014) as a more precise but more complex alternative to the contention-based method of computing pWCET estimates. This approach performs exhaustive cache state enumeration for a selection of *relevant* accesses, hence providing tight analysis results for those accesses. To prevent state explosion, at each point in the program no more than *R* memory blocks are *relevant* at the same time. The *relevant* accesses are ones heuristically identified as benefiting the most from a precise analysis.

A trace t is defined as an ordered sequence  $[e_1, \ldots, e_n]$  of n accesses to memory blocks, such that  $e_i = e_j$  if accesses  $e_i$  and  $e_j$  target the same memory block. If access

Table 1 Summary of introduced notations

| Notation                         | Description                                                                                                                           |  |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| pWCET                            | Upper-bound on the execution time distribution of a program over all paths                                                            |  |

| $\mathcal{H}$                    | Upper-bound on the latency incurred by a cache hit                                                                                    |  |

| $\mathcal{M}$                    | Upper-bound on the latency incurred by a cache miss                                                                                   |  |

| N                                | Cache associativity                                                                                                                   |  |

| $\mathbb{E}$                     | Set of accessed cache blocks                                                                                                          |  |

| $\mathbb{E}^{\perp}$             | Set of accessed cache blocks including non-relevant elements $\perp$                                                                  |  |

| $t = [e_1, \dots, e_i]$          | A trace, a sequence of accesses to memory blocks                                                                                      |  |

| $\mathcal{D}$                    | Execution time or cache miss probabilistic distribution                                                                               |  |

| $\mathcal{D}(x)$                 | Occurrence probability of execution time x                                                                                            |  |

| $P(\mathcal{D} \ge x)$           | Likelyhood that distribution $\mathcal{D}$ exceeds execution time $x$                                                                 |  |

| $s \in \mathbb{CS}$              | Analysed cache state                                                                                                                  |  |

| $(C, P, \mathcal{D}) = s$        | Analysed cache state including:                                                                                                       |  |

|                                  | - C: Cache contents, set of blocks known to be present in cache;                                                                      |  |

|                                  | - P: Occurrence probability of the cache state at a specific program point;                                                           |  |

|                                  | - $\mathcal{D}$ : Execution time distribution up to a specific program point                                                          |  |

| $\mathcal{D}_{init}$             | Initial, empty execution time distribution                                                                                            |  |

| $S \in 2^{CS}$                   | Set of possible caches states at a specific program point                                                                             |  |

| $S \oplus S'$                    | Weighted merge on cache states, merge probability and distributions for cache states with identical contents                          |  |

| u(s, e)                          | Update cache state $s$ upon access to element $e$ , replacing a line and increasing the corresponding distribution $D$ upon a miss    |  |

| U(S,e)                           | Update each cache state in set $S$ upon access to element $e$                                                                         |  |

| rd(e,t)                          | Reuse distance of element $e$ in trace $t$ , upper-bound on the number of evictions since the last access to $e$                      |  |

| frd(e,t)                         | Forward reuse distance of element $e$ in trace $t$ , upper-bound on the number of evictions before the next access to $e$             |  |

| con(e,t)                         | Cache contention for element $e$ in trace $t$ , bound on the number of blocks contending for cache space since the last access to $e$ |  |

| $\hat{P}(e_i^{hit})$             | Lower-bound on the probability of access $e_i$ to hit in cache                                                                        |  |

| $\hat{\xi_i}$                    | Upper-bound on the execution time probability of element $e_i$ , expressed as a probability mass function                             |  |

| $\hat{\mathcal{D}}(t)$           | Upper-bound on the execution time distribution of trace <i>t</i>                                                                      |  |

| $\mathcal{D}(t,s)$               | Execution time distribution of trace $t$ starting from cache state $s$                                                                |  |

| $\mathcal{D}(t,S)$               | Execution time distribution of trace t starting from possible cache states S                                                          |  |

| $\mathcal{D}\otimes\mathcal{D}'$ | Convolution of distributions $\mathcal{D}$ and $\mathcal{D}'$                                                                         |  |

| $\mathcal{D}\odot\mathcal{D}'$   | Least upper-bound of distributions $\mathcal{D}$ and $\mathcal{D}'$                                                                   |  |

| $\mathcal{D} \leq \mathcal{D}'$  | Distribution $\mathcal{D}'$ upper-bounds $\mathcal{D}$ , iff $\forall x, P(\mathcal{D} \ge x) \le P(\mathcal{D}' \ge x)$              |  |

| $G = (V, L, v_s, v_e)$           | Control flow graph G capturing possible paths in a program, including:                                                                |  |

|                                  | V: Set of nodes in the program, each corresponding to an accessed element;                                                            |  |

|                                  | L: Set of edges between nodes;                                                                                                        |  |

Table 1 continued

| Notation                  | Description                                                                                                                                        |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                           | $v_s \in V$ : Start node in the program;                                                                                                           |  |

|                           | $v_e \in V$ : End node in the program                                                                                                              |  |

| $\pi = [v_1, \dots, v_k]$ | Path from node $v_1$ to $v_k$ , valid sequence of nodes in a CFG                                                                                   |  |

| $v_i \to *v_j$            | Set of paths from $v_i$ to $v_j$                                                                                                                   |  |

| $dom(v_n)$                | Dominators of node $v_n$ , nodes guaranteed to be traversed before $v_n$ from the CFG entry $v_s$                                                  |  |

| $post-dom(v_n)$           | Post-dominators of node $v_n$ , nodes guaranteed to be traversed after $v_n$ to the CFG exit $v_e$                                                 |  |

| $\Pi(V)$                  | All paths with nodes included exclusively in set of vertices $V$                                                                                   |  |

| $\Pi(G)$                  | All paths from the start to the end of CFG $G$                                                                                                     |  |

| $\hat{\mathcal{D}}(\pi)$  | Upper-bound on the execution time distribution of path $\pi$                                                                                       |  |

| $\hat{\mathcal{D}}(G)$    | pWCET of $G$ , upper-bound on the execution time of its paths                                                                                      |  |

| $rd^G(v)$                 | Maximum reuse distance of node $v$ across all paths in $G$ leading to $v$                                                                          |  |

| $frd^G(v)$                | Maximum forward reuse distance of node $v$ across all paths in $G$ leading to $v$                                                                  |  |

| $con^G(v)$                | Maximum contention of node $v$ across all paths in $G$ leading to $v$                                                                              |  |

| $s \sqsubseteq S$         | Cache state $s$ holds less pessimistic information than the set of cache states $S$                                                                |  |

| $S \sqsubseteq S'$        | The set of cache states $S$ holds less pessimistic information than states in $S'$                                                                 |  |

| $S \sqcup S'$             | Upper-bound on cache states $S$ and $S'$ , more pessimistic than both $S$ and $S'$                                                                 |  |

| $C \leq_{rank} C'$        | Ranking of cache contents <i>C</i> , used for heuristic comparison of contents based on their expected contribution to execution time distribution |  |

| Flush(S)                  | Empty the contents of all cache states in S                                                                                                        |  |

$e_i$  is relevant, the block it accesses will be considered relevant until the next non-relevant access to the same block. The precise approach is only applied for relevant accesses while the contention-based method outlined in Sect. 2.2.1 is used for the others, identified as  $\bot$  in the trace of relevant blocks. The set of elements in a trace becomes  $\mathbb{E}^\bot = \mathbb{E} \cup \{\bot\}$ .

The abstract domain of the analysis is a set of cache states. A cache state is a triplet  $CS = (C, P, \mathcal{D})$  with cache contents C, a corresponding probability  $P \in \mathbb{R}, 0 < P \leq 1$ , and a miss distribution  $\mathcal{D} \colon \mathbb{N} \to \mathbb{R}$  when the cache is in state C. C is a set of at most N memory blocks picked from  $\mathbb{E}$ . A cache state which holds less than N memory blocks represents partial knowledge about the cache contents without any distinction between empty lines or unknown contents. The set of all cache states is denoted by  $\mathbb{CS}$ . Miss distribution  $\mathcal{D}$  captures for each possible number of misses n, the probability that n misses occurred from the beginning of the program up to the current point in the program. The method computes all possible behaviours of the random cache with the associated probabilities. It is thus correct by construction as it simply enumerates all states exhaustively.

<sup>&</sup>lt;sup>1</sup> This suits evict-on-miss caches which do not prioritize empty lines when filling the cache.

The analysis starts from the empty cache state  $\{(\emptyset, 1, \mathcal{D}_{init})\}\$  where

$$\mathcal{D}_{init}(x) = \begin{cases} 1 & if \ x = 0 \\ 0 & otherwise \end{cases} \tag{1}$$

The update function u describes the update for a single cache state upon access to element  $e \in \mathbb{E}^{\perp}$ . Upon accessing a relevant element  $e \neq \perp$ , if e is present in the cache, its contents are left unchanged. Otherwise new cache states need to be generated considering that each element may be evicted with the same probability  $\frac{1}{N}$  (in the *evict* function). A miss is accounted for in the resulting distributions  $\mathcal{D}'$  only upon misses on a relevant access. Formally:

$$u: \mathbb{CS} \times \mathbb{E}^{\perp} \to 2^{\mathbb{CS}}$$

(2)

$$u((C, P, D), e) = \begin{cases} \{(C, P, D)\} & \text{if } e \in C \land e \neq \bot \\ evict((C, P, D), e) & \text{otherwise} \end{cases}$$

(3)

$$u: \mathbb{CS} \times \mathbb{E}^{\perp} \to 2^{\mathbb{CS}}$$

$$u((C, P, D), e) = \begin{cases} \{(C, P, D)\} & \text{if } e \in C \land e \neq \bot \\ evict((C, P, D), e) & \text{otherwise} \end{cases}$$

$$evict((C, P, D), e) = \begin{cases} \{(C \setminus \{e'\} \cup \{e\}, P \cdot \frac{1}{N}, D') \mid e' \in C\} \cup \{(C \cup \{e\}, P \cdot \frac{N - |C|}{N}, D')\} & \text{if } e \neq \bot \\ \{(C \setminus \{e'\}, P \cdot \frac{1}{N}, D') \mid e' \in C\} \cup \{(C, P \cdot \frac{N - |C|}{N}, D')\} & \text{if } e = \bot \end{cases}$$

$$D'(x) = \begin{cases} D(x) & \text{if } e = \bot \\ 0 & \text{if } x = 0 \\ D(x - 1) & \text{otherwise} \end{cases}$$

$$(2)$$

$$(3)$$

$$evict((C, P, D), e) = \begin{cases} \{(C \setminus \{e'\} \cup \{e\}, P \cdot \frac{1}{N}, D') \mid e' \in C\} \cup \{(C \cup \{e\}, P \cdot \frac{N - |C|}{N}, D')\} & \text{if } e \neq \bot \end{cases}$$

$$(5)$$

$$\mathcal{D}'(x) = \begin{cases} \mathcal{D}(x) & \text{if } e = \bot \\ 0 & \text{if } x = 0 \\ \mathcal{D}(x - 1) & \text{otherwise} \end{cases}$$

(5)

The evict(s, e) function creates N different cache states, one per possible evicted element, some of which might represent the same cache contents. To reduce the state space, a merge operation [+] combines two cache states if they contain exactly the same memory blocks. If merging occurs, each distribution is weighted by its probability:

$$\left[+\right]: 2^{\mathbb{CS}} \to 2^{\mathbb{CS}} \tag{6}$$

$$\biguplus \left( \left\{ \begin{array}{c} (C_0, P_0, \mathcal{D}_0) \\ \vdots \\ (C_n, P_n, \mathcal{D}_n) \end{array} \right\} \right) = \left\{ Merge\left( \left\{ (C_i, P_i, \mathcal{D}_i) | C_i = C_j \right\} \right) \middle| 0 \le j \le n \right\}$$

$$(7)$$

$$Merge\left\{\begin{cases} (C_0, P_0, \mathcal{D}_0) \\ \vdots \\ (C_n, P_n, \mathcal{D}_n) \end{cases}\right\} = \left(C_0, \sum_{i=0}^n P_i, \sum_{i=0}^n \frac{P_i}{\sum_{k=0}^n P_k} \cdot \mathcal{D}_i\right)$$

(8)

where  $p \cdot \mathcal{D}$  denotes the multiplication of the elements of distribution  $\mathcal{D}$ ,  $(p \cdot \mathcal{D})(x) =$  $p \cdot \mathcal{D}(x)$ , and  $\mathcal{D}_1 + \mathcal{D}_2$  is the summation of two distributions,  $(\mathcal{D}_1 + \mathcal{D}_2)(x) =$  $\mathcal{D}_1(x) + \mathcal{D}_2(x)$ .

The update function can be defined for a set of cache states using the update function u for a single cache state and the  $\oplus$  merge operator as follows:

$$U: 2^{\mathbb{CS}} \times \mathbb{E}^{\perp} \to 2^{\mathbb{CS}} \tag{9}$$

$$U(S, e) = \biguplus \{ u(CS, e) \mid CS \in S \}$$

(10)

Given  $S_{res}$  the set of cache states at the end of the execution of a trace t, the miss distribution  $\hat{\mathcal{D}}_{miss}$  of the relevant blocks in t is the sum of the individual distributions of each cache state weighted by their probability of occurrence:

$$\hat{\mathcal{D}}_{miss} = \sum \{ P \cdot \mathcal{D} \mid (C, P, \mathcal{D}) \in S_{res} \}$$

(11)

The corresponding execution time distribution,  $\hat{\mathcal{D}}$ , can then be derived, for a trace of *n* accesses, as follows:

$$\hat{\mathcal{D}}(m \times \mathcal{M} + (n - m) \times \mathcal{H}) = \hat{\mathcal{D}}_{miss}(m)$$

(12)

# 2.2.1 Non-relevant blocks analysis

One possible naive approach for non-relevant blocks would be to classify them as misses in the cache and add the resulting latency to the previously computed distributions. The collecting approach proposed by Altmeyer and Davis (2014) relies on the application of the contention methods to estimate the behaviour of the non-relevant blocks in a trace. Each access in a trace has a probability of being a cache hit  $P(e_i^{hit})$ , and of being a cache miss  $P(e_i^{miss}) = 1 - P(e_i^{hit})$ . These methods rely on different metrics to lower-bound the hit probability of each access such that the derived bound can be soundly convolved.

The reuse distance rd(e) of element e is the maximum number of accesses to consecutively different blocks since the last access to the same block. It captures an upper-bound on the maximum number of possible evictions between two accesses to the same block, similarly to the stack distance for LRU caches. It differs from the stack distance in that accesses to the same intermediate block may thus be accounted for multiple times if they may have been evicted during the access sequence. Should there be no such prior access to the same block, the reuse distance is defined as  $\infty$ . Given the set of all traces  $\mathbb T$  and of all elements  $\mathbb E$ , the reuse distance is formally defined as:

$$rd(e_i, [e_1, \dots, e_{i-1}]) = \begin{cases} |\{k | j < k < i \land e_k \neq e_{k-1}\}| & \text{if } e_i = e_j \land \\ \forall k : j < k < i, e_i \neq e_k \end{cases}$$

$$0 \text{ otherwise}$$

$$(13)$$

Note that this definition of the reuse distance is a variation of the one proposed in earlier work. The revised equation (13) computes the same property, but has to discard successive accesses to the same block. Successive accesses to the same memory block lead to guaranteed cache hits under an evict-on-miss cache replacement policy. Traces are thus collapsed in Altmeyer et al. (2015) to remove all successive accesses to the same memory block. The number of cache misses is not impacted and cache hits can later be accounted for as an additional contribution to the trace. This last step is not straightforward for multi-path programs as the number of guaranteed hits varies on different paths.

Conversely, we define the forward reuse distance frd(e) of an element e as the maximum number of possible evictions before the next access to the same block. If its block is not reused before the end of the trace, the forward reuse distance of an access is defined as  $\infty$ :

$$frd: \mathbb{E} \times \mathbb{T} \to \mathbb{N} \cup \{\infty\}$$

$$frd(e_i, [e_{i+1}, \dots, e_m]) = \begin{cases} |\{k \mid j < k < i \land e_k \neq e_{k-1}\}| & \text{if } e_i = e_j, \\ \forall k : i < k < j, e_i \neq e_k \end{cases}$$

$$otherwise$$

$$(14)$$

The probability of  $e_i$  being a hit is set to 0 if there are more blocks since the last access to the same block that contend for cache space than the N available lines. This is captured by the cache contention  $con(e_i, t)$  (Altmeyer and Davis 2014) of element  $e_i$  in trace t. The definition of  $\hat{P}(e_i^{hit})$  which denotes a lower bound on the actual probability  $P(e_i^{hit})$  of a cache hit is as follows:

$$\hat{P}(e_i^{hit}) = \begin{cases} 0 & con(e_i, t) \ge N \\ \left(\frac{N-1}{N}\right)^{rd(e_i, t)} & otherwise \end{cases}$$

(15)

The cache contention con(e) (Altmeyer and Davis 2014) of element e captures the number of cache blocks which contend with e for space in the cache. It includes all potential hits and the R relevant blocks, denoted  $relevant\_blocks$ , since we have to assume they occupy a separate location in the cache. Contention depends on and contributes to the potential hits captured by  $\hat{P}(e_j^{hit})$ , j < i, and is computed from the first accesses, where  $rd(e_i, t) = \infty$ , to the last. The contention also accounts for the first miss  $e_r$  which follows the previous access to the same memory block as  $e_i$  and hence contends with  $e_i$ . The replacement policy means that  $e_r$  always contends for space. The cache contention is formally defined as:

$$con: \mathbb{E} \times \mathbb{T} \to \mathbb{N} \cup \{\infty\}$$

$$con(e_i, t) = \begin{cases} \infty & \text{if } rd(e_i, t) = \infty \\ |\{e_k | k \in conS(e_i, t) \land e_k \notin relevant\_blocks\}| + R & \text{otherwise} \end{cases}$$

$$(16)$$

with

$$conS(e_{i}, t) = \{j \mid e_{j} \in t \land \hat{P}(e_{j}^{hit}) \neq 0 \land k < j < i \land e_{k}$$

$$= e_{i} \land \forall x : k < x < i, e_{i} \neq e_{x}\}$$

$$\cup \{r \mid rd(e_{i}, t) \neq 0 \land k$$

$$r = min(\{x \mid \hat{P}(e_{x}^{hit}) = 0 \land k < x < i \land e_{k}$$

$$= e_{i} \land \forall y : k < y < i, e_{i} \neq e_{y}\})\}$$

$$(17)$$

*Example* We now illustrate the distinction between cache contention and reuse distance in identifying accesses with a null hit probability in (15). Consider the following sequence of accesses, on a 4 line fully-associative cache, where the reuse distance of each access is given as a super-script:

$$a, b, c, b^1, d, f, a^5, b^3, c^5, d^4, f^4$$

All second accesses to blocks a, b, c, d, and f have a non-zero chance to hit when considered in isolation. However as highlighted in Altmeyer and Davis (2014), those cannot be simply combined as the hit probability of a block depends on the behaviour of other blocks; the last 5 accesses of the sequence, each accessing a different block, cannot hit at the same time assuming a 4 line cache. The hit probability of an access need to be set to 0 in (15) if enough blocks are inserted in cache since the last access to the same block. Should the reuse distance be considered to identify whether or not an access is a potential hit, the last occurrences of a, c, d, and f would be considered as misses.

Using cache contention, some accesses are assumed to be potential hits, occupying cache space to the detriment of others. Cache contention captures a specific but potential hit/miss scenario the occurrence of which is bounded using each access hit probability in (15). As proven in Altmeyer and Davis (2014), the estimated hit probability of the overall sequence holds. In our example, contention identifies that a, b, and c can be kept in the cache simultaneously. Using the contention as a super-script, we have:

$$a, b, c, b^1, d, f, a^2, b^2, c^3, d^4, f^4$$

$c^3$  implies that c may be present in cache, assuming only three other blocks may have been kept alongside it, a and b as potential cache hits, and d then replaced by f. This assumption regarding d and f is an important difference between contention and the stack distance metric used in LRU cache analysis. Using the stack distance, i.e. the number of different blocks accessed since the last access to c, d and f would be regarded as occupying a different line in cache, resulting in a guaranteed miss for c.  $d^4$  is classified as a miss:  $a^2$ ,  $b^2$  and  $c^3$  have been identified as potential misses, and f is a miss resulting in the eviction of the fourth and only cache line where d could be held.  $f^4$  is similarly classified as a miss.

Note that this definition of contention is an improvement on the one proposed in earlier work. Instead of accounting for each access independently, we account for their accessed blocks instead. The reasoning behind this optimisation is that if an accessed block hits more than once, it does not occupy additional lines. In the previous example, b is only accounted for once in the contention of  $a^2$  and  $c^3$ . The subtle difference lies in (17) where the blocks  $e_j$  are accounted for instead of each access j individually ( $e_i = e_j$  if they access the same block).

The execution time of an element  $e_i$  can be approximated with the help of the discrete random variable  $\hat{\xi}_i$  which has a probability mass function (PMF) defined as:

$$\hat{\xi}_{i}(x) = \begin{cases} \hat{P}(e_{i}^{hit}) & \text{if } x = \mathcal{H} \\ 1 - \hat{P}(e_{i}^{hit}) & \text{if } x = \mathcal{M} \\ 0 & \text{otherwise} \end{cases}$$

(18)

An estimated pWCET (Cucu-Grosjean 2013) distribution  $\hat{\mathcal{D}}$  of a trace, is an upper-bound on the execution time distribution  $\mathcal{D}$  induced by the randomised cache for the trace,  $^2$  such that  $\forall v, P(\hat{\mathcal{D}} \geq v) \geq P(\mathcal{D} \geq v)$ . In other words, the distribution  $\hat{\mathcal{D}}$  is greater than  $\mathcal{D}$  (López et al. 2008), denoted  $\hat{\mathcal{D}} \geq \mathcal{D}$ .

The probability mass functions  $\hat{\mathcal{E}}_i$  are independent upper-bounds on the behaviour of corresponding accesses  $e_i$ . An estimate for trace t can be derived by combining the probability mass function  $\hat{\mathcal{E}}_i$  for each of its composing memory accesses  $e_i$ :

$$\hat{\mathcal{D}}(t) = \bigotimes_{e_i \in t} \hat{\mathcal{E}}_i \tag{19}$$

where  $\otimes$  represents the convolution of PMFs:

$$(\hat{\xi}_i \otimes \hat{\xi}_j)(x) = \sum_{k=-\infty}^{+\infty} \hat{\xi}_i(k) \cdot \hat{\xi}_j(x-k)$$

(20)

The resulting distribution for non-relevant accesses is independent of the relevant blocks considered in the cache during the collecting analysis step. A worst-case is assumed where the R blocks are always kept in cache. The distributions resulting from the two analysis steps, collecting and contention, can therefore be soundly convolved to estimate the execution time of a trace. The pWCET of a trace can then be derived by convolving the execution time distributions produced by the contention, and collecting approaches, as derived from  $\hat{\mathcal{D}}^{miss}$ .

#### 2.3 Discussion: relevance of the model

The SPTA techniques described apply whether the contents of the memory block are instruction(s), data or both. While address computation (Huynh et al. 2011) may not be able to pinpoint the exact target of an access, e.g. for data-dependent requests, relational analysis (Hahn and Grund 2012), introduced in the context of deterministic systems, can be used to identify accesses which map to the same or different sets, and access the same or different block. Two accesses which obey the same block relation can then be replaced by accesses to the same unique element, hence improving the precision of the analysis.

The methods assume that there are no inter-task cache conflicts due to preemption, i.e. a run-to-completion semantics with non-preemptable program execution. Concur-

$<sup>\</sup>frac{1}{2}$  Note the precise execution time distribution is effectively that which would be observed by executing the trace an infinite number of times.

rent cache accesses are also precluded, i.e. we assume a private cache or appropriate isolation (Chiou et al. 2000).

In practice, detailed analysis could potentially distinguish between different latencies for each access, beyond  $\mathcal{M}$  and  $\mathcal{H}$ , but such precise estimation of the miss latency requires additional analysis steps, e.g. analysis of the main memory (Bourgade et al. 2008). Further, to reduce the pessimism inherent in using a simple bound, particularly for the miss latency, events such as memory refresh can be accounted for as part of higher level schedulability analyses (Atanassov and Puschner 2001; Bhat and Mueller 2011).

# 3 Comparing cache contents

The execution time distribution of a trace in our model depends solely on the behaviour of the cache. The contribution of a cache state to the execution time of a trace thus solely depends on its initial contents. The characterisation of the relation between the initial contents of different caches allows for a comparison of their temporal contribution to the same trace. This section introduces properties and conditions that allow this comparison. They are used in later techniques to improve the selection of cache contents on path convergence, and identify paths with the worst impact on execution time.

An *N*-tuple represents the concrete contents of an *N*-way cache, such that each element corresponds to the block held by a single line. The symbol \_ is used to denote an empty line. For each such concrete cache *s*, there is a corresponding abstract cache contents *C* which holds the exact same set of blocks. *C* might also capture uncertainty regarding the contents of some lines.

Given cache state  $s = \langle l_1, \ldots, l_N \rangle$ ,  $s = [l_i = b]$  represents the replacement of memory block or line  $l_i$  in cache by memory block b. Note that b can only be present once in the cache,  $b \in s \Rightarrow s[l_i = b] = s$ .  $s[-l_i]$  is a shorthand for  $s[l_i = \_]$  and identifies the eviction of memory block  $l_i$  from the cache.  $s[l_i = b][l_j = e]$  denotes a sequence of replacements where b first replaces  $l_i$  in s, then e replaces  $l_j$ . Two cache states s and s' although not strictly identical may exhibit the same behaviour if they hold the exact same contents, e.g.  $\langle a, \_ \rangle = \langle \_, a \rangle$  are represented using the same abstract contents  $\{a\}$ . Under the evict-on-miss random replacement policy, there is no correlation between the physical and logical position of a block with respects to the eviction policy.

We distinguish the execution time distribution of trace t using input cache state s with the notation  $\mathcal{D}(t,s)$ . The execution time distribution of the sequence [[b],t], the concatenation of access [b] to trace t, can be expressed as follows:

$$\mathcal{D}([[b], t], s = \langle l_1, \dots, l_N \rangle) = \begin{cases} \mathcal{H} + \mathcal{D}(t, s) & \text{if } b \in s \\ \mathcal{M} + \sum_{i \in [1, N]} \frac{1}{N} \cdot \mathcal{D}(t, s[l_i = b]) & \text{otherwise} \end{cases}$$

(21)

$<sup>^3</sup>$  We assume a fully-associative cache, but this restriction can be lifted to set-associative caches through the independent analysis of each set.

where the sum of distributions and the product of a distribution with  $\frac{1}{N}$  are defined as per (6), and  $(\mathcal{L} + \mathcal{D})(x) = \mathcal{L} + \mathcal{D}(x)$  denotes the sum of distribution  $\mathcal{D}$  with latency  $\mathcal{L}$ . Upon a hit, the input cache state s is left unchanged, while evictions occur to make room for the accessed block upon a miss.

The extension of this definition to the concatenation of traces requires the identification of the outcomes of an execution, i.e. the cache state C corresponding to each possible sequence of events, along with its occurrence probability P and execution time distribution  $\mathcal{D}$ :

$$\mathcal{D}([t_p, t_s], s) = \sum_{(C, P, \mathcal{D}) \in outcomes(t_p, s)} P \cdot (\mathcal{D} \otimes \mathcal{D}(t_s, C))$$

(22)

where  $outcomes(t_p, s)$  is the set of cache states produced by the execution of  $t_p$  from input cache state s and  $\otimes$  is the convolution of distributions.

**Theorem 1** *The eviction of a block from any input cache state s cannot decrease the execution time distribution of any trace t*,  $\mathcal{D}(t, s) \leq \mathcal{D}(t, s[-e])$ .

**Corollary 1** In the context of evict-on-miss randomised caches, for any trace, the empty state is the worst initial state over any other input cache state s,  $\mathcal{D}(t,s) \leq \mathcal{D}(t,\emptyset)$ .

The eviction of a block might trigger additional misses, resulting in a distribution that is no less than the one where the cache contents is left untouched. This provides evidence that the assumption upon a non-relevant access that a block in cache is evicted, as per the update function in (3), is sound. Similarly, the replacement of a block in the cache might trigger additional misses but might also result in additional hits instead upon reuse of the replacing block. The impact of such a behaviour is however bounded.

**Theorem 2** The replacement of a random block in cache triggers at most one additional hit.

The distribution for any trace t from any cache state s is upper-bounded by the distribution for trace t after the replacement of a random block in s and assuming a single hit turns into a miss.

$$\mathcal{H} + \mathcal{D}(t,s) \le \mathcal{M} + \sum_{i \in [1,N]} \frac{1}{N} \cdot \mathcal{D}(t,s[l_i = e])$$

(23)

Proof See Appendix.

The block selected for eviction impacts the likelihood of those additional latencies suffered during the execution of the subsequent trace. Intuitively, the closer the evicted block is to reuse, the worse the impact of the eviction. We use the forward reuse distance of blocks at the beginning of trace t, frd(b, t) as defined in (14), to identify the blocks which are closer to reuse than others.

**Theorem 3** The replacement of a block in input cache state s by one which is reused later in trace t cannot result in a decreased execution time distribution:  $frd(b, t) \leq frd(e, t) \leq \infty \land b \in s \land e \notin s \Rightarrow \mathcal{D}(t, s) \leq \mathcal{D}(t, s[b = e])$

# 4 Application of SPTA to multi-path programs

In this section, we improve upon the state-of-the-art SPTA techniques for traces (Altmeyer and Davis 2014) recapitulated in Sect. 2 and present methods for multi-path programs, that is complete control-flow graphs. A naive approach would be to compute all possible traces  $\mathcal{T}$  of a task, analyse each independently and combine their distributions. However, there are two significant problems with such an approach.

Firstly, while the merge operation (6) could be used to provide a weighted combination given the probability of each path being taken at runtime, such assumptions about path probability do not hold in general. This issue can however be resolved by taking the maximum distribution of the resulting execution-time distributions for each trace:

$$\bigodot_{t \in \mathcal{T}} \mathcal{D}(t) \tag{24}$$

where we define the ⊙ operation as follows

$$\bigcirc: ((\mathbb{N} \to \mathbb{R}) \times (\mathbb{N} \to \mathbb{R})) \to (\mathbb{N} \to \mathbb{R}) \tag{25}$$

$$\mathcal{D}_a \odot \mathcal{D}_b := \mathcal{D}^H \tag{26}$$

with

$$\mathcal{D}^{H}(x) = \max\left(\sum_{y \ge x} \mathcal{D}_{a}(y) - \sum_{y > x} \mathcal{D}^{H}(y), \sum_{y \ge x} \mathcal{D}_{b}(y) - \sum_{y > x} \mathcal{D}^{H}(y), 0\right)$$

(27)

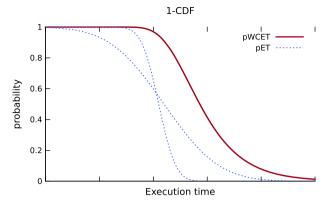

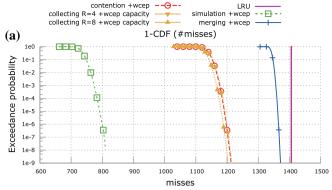

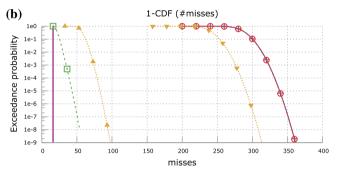

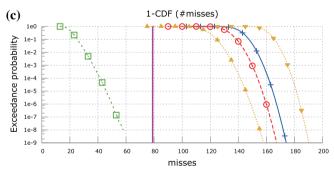

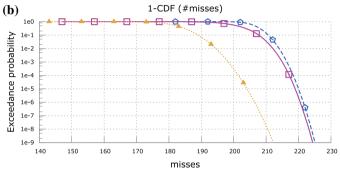

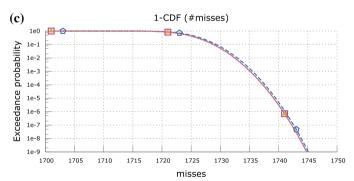

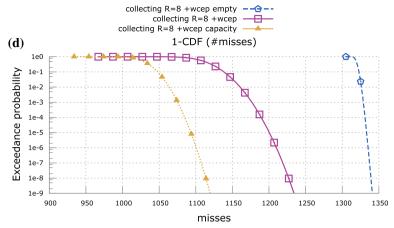

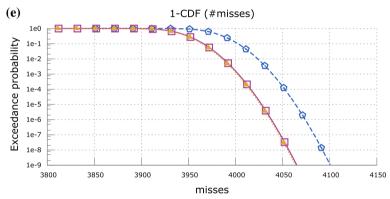

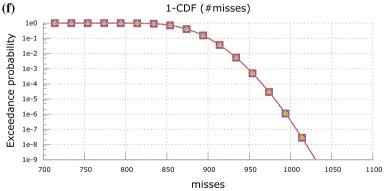

The  $\odot$  operator computes the least upper-bound of the complementary cumulative distribution (1-CDF) of all its operands (similar to the upper-bound depicted in Fig. 1), a maximum of distributions which is valid irrespective of the path executed at runtime. By construction the following properties hold

$$\mathcal{D}_a \odot \mathcal{D}_b \ge \mathcal{D}_a \wedge \mathcal{D}_a \odot \mathcal{D}_b \ge \mathcal{D}_b \tag{28}$$

$$\mathcal{D}_a < \mathcal{D}_b \Rightarrow \mathcal{D}_a \odot \mathcal{D}_b = \mathcal{D}_b \tag{29}$$

Secondly, the number of distinct traces is exponential in the number of control flow divergences, conditional constructs and loop iterations, which means that this naive approach is computationally intractable. A standard data-flow analysis is also problematic, since it is not possible to assign to each instruction a corresponding contribution to the execution time distribution.

Our analysis on control-flow graphs resolves these problems. It relies on the collecting and the contention approaches for relevant and non-relevant blocks respectively, as

Fig. 1 Relation between the execution time distribution of different paths (pET) and the pWCET of a program

per the cache collecting approach on traces given by Altmeyer and Davis (2014). First, the loops in the control-flow graph are unrolled. This allows the implementation of the following steps, the computation of cache contention, the identification of relevant blocks and the cache collection, to be performed as simple forward traversals of the control flow graph. Approximation of the possible incoming states on path convergence keeps the analysis tractable. Finally, the contention and collecting distributions are combined using convolution.

#### 4.1 Program representation

We represent the possible paths in a program using a control-flow graph (CFG), that is a directed graph  $G = (V, L, v_s, v_e)$  with a finite set V of nodes, a set  $L \subseteq V \times V$  of edges, a start node  $v_s \in V$  and an end node  $v_e \in V$ . Each node v corresponds to an element in  $\mathbb{E}$  accessed at node v. A path  $\pi$  from node  $v_1$  to node  $v_k$  is a sequence of nodes  $\pi = [v_1, v_2, \ldots, v_{k-1}, v_k]$  where  $\forall i : (v_i, v_{i+1}) \in L$  and defines a corresponding trace. By extension,  $[\pi, \pi']$  denotes the path composed of path  $\pi$  followed by path  $\pi'$ . Given a set of nodes V', the symbol  $\Pi(V')$  denotes the set of all paths with nodes that are included exclusively in V', and  $\Pi(G) \subseteq \Pi(V)$  the set of all paths of CFG G from  $v_s$  to  $v_e$ . Similarly to traces, the pWCET  $\hat{\mathcal{D}}(G)$  of a program is the least upper-bound on the execution time distributions (pET) of all possible paths. Hence,  $\forall \pi \in \Pi(G), \hat{\mathcal{D}}(G) \geq \mathcal{D}(\pi)$ . Figure 1 illustrates this relation using the 1-CDF  $(F(x) = P(\mathcal{D} \geq x))$  of different execution time distributions and a valid pWCET.

We say that a node  $v_d$  dominates  $v_n$  in the control-flow graph G if every path from the start node  $v_s$  to  $v_n$  goes through  $v_d$ ,  $v_s \to^* v_n = v_s \to^* v_d \to^* v_n$ , where  $v_s \to^* v_d \to^* v_n$  is the set of paths from  $v_s$  to  $v_n$  through  $v_d$ . Similarly, a node  $v_p$  post-dominates  $v_n$  if every path from  $v_n$  to the end node  $v_e$  goes through  $v_p$ ,  $v_n \to^* v_e = v_n \to^* v_p \to^* v_e$ . We refer to the set of dominators and post-dominators of node  $v_n$  as  $dom(v_n)$  and  $post-dom(v_n)$  respectively.

We assume that the program always terminates. Bounded recursion and loop iterations are requirements to ensure this termination property of the analysed application.

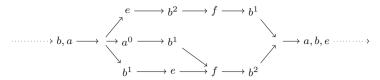

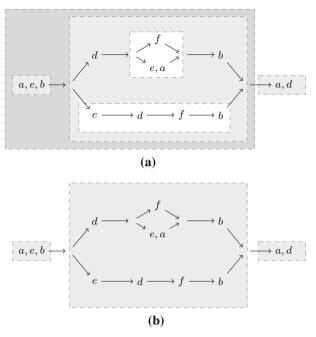

Fig. 2 Simple do-while loop structure with an embedded conditional. b is the loop head, with its body comprising  $\{b, c, d, e\}$  and the e to b edge as the back-edge. e and c are both valid exits

The additional restrictions described below are for the most part tied to the WCET analysis framework (Wilhelm et al. 2008) and not exclusive to the new method. These are reasonable assumptions for the software in critical real-time systems.

Any cycle in the CFG must be part of a natural loop. We define a natural loop  $l=(v_h,V_l)$  in G with a header  $v_h \in V$  and a finite set of nodes  $V_l \subseteq V$ . Considering the example in Fig. 2, b is the head of the loop composed of accesses  $V_l = \{b,d,c,e\}$ . The header is the single entry-point of the loop,  $\forall v_n \in V_l, v_h \in dom(v_n)$ . Conversely, a natural loop may exhibit multiple exits, e.g. as a result of break constructs. Loop l contains at least one back edge to  $v_h$ , an edge whose end is a dominator of its source  $\exists v_b \in V_l, (v_b, v_h) \in L$ . All nodes in the loop can reach one of its back edges without going through the header  $v_h$ . The transition from the header  $v_h$  of loop l to one of its nodes  $v_n \in V_l$  begins an iteration of the loop. The maximum number of consecutive iterations of each loop, iterations which are not separated by the traversal of a node outside  $V_l$ , is assumed to be upper-bounded by max-iter(l, ctx). The value of max-iter(l, ctx) might change depending on the context ctx, call stack and loop iteration, of loop l, e.g. to capture triangular loops. This guarantees a finite number of paths in the program.

Calls are also subject to a small set of restrictions to guarantee the termination of the program. Recursion is assumed to be bounded, that is cycles or repetitions in the call graph of the analysed application must have a maximum number of iterations, similarly for loops in the control flow. Function pointers can be represented as multiple targets attached to a single call. Here, the set of target functions must be exact or an over-estimate of the actual ones, so as to avoid unsound estimates which do not take all valid paths into account.

#### 4.2 Complete loop unrolling

In the first analysis step, we conceptually transform the control-flow graph into a directed acyclic graph by loop unrolling and function inlining (Muchnick 1997). In contrast to the naive approach of enumerating all possible traces, analysis through complete loop unrolling has linear rather than exponential complexity with the number of loop iterations.

Loop unrolling and function inlining are well-known techniques to improve the precision of data-flow analyses. A complete physical unrolling that removes all backedges significantly increases the size of the control-flow graph. A virtual unrolling and inlining is instead performed during analysis such that calls and iterations are processed as required by the control flow. The analysis then distinguishes the different call and iteration contexts of a vertex. In either case, the size of the graph explored

during analysis and its complexity scales with the number of accesses in the program under consideration.

Unrolling simplifies the analysis and significantly improves the precision. As opposed to state of the art analyses for deterministic replacement policies (Alt et al. 1996), the analysis of random caches through cache state enumeration does not rely on the computation of a fixpoint. The abstract domain for the analysis is by nature growing with every access since it includes the estimated distribution of misses. Successive iterations increase the probability of blocks in the loop's working set being in the cache, and in turn increase the likelihood of hits in the next iteration. The exhaustive analysis, if not supplemented by other methods, must process all accesses in the program.

We assume in the following that unrolling is performed on all analysed programs. Section 6.4.2 discusses preliminary work to bypass this restriction. The analysis of large loops, with many predicted iterations, can be broken down into the analysis of a single iteration or groups thereof provided a sound upper-bound of the input state is used. The contributions of different segments are then combined to compute that of the complete loop or program. Such an upper-bound input can be derived as an example using cache state compression (Griffin et al. 2014a) to remove low value information. The definition of techniques to exploit the resulting trade-off between precision and analysis complexity is left as future work.

#### 4.3 Reuse distance/cache contention on CFG

To extend the concept of reuse distance to control-flow graphs, we lift the definition from a single trace to all traces and take the maximal reuse distance of all possible traces ending in the node v:

$$rd^G \colon \mathbb{V} \to \mathbb{N} \cup \{\infty\} \tag{30}$$

$$rd^{G}(v) = \max_{\pi = [v_{s}, \dots, v]} (rd(v, \pi))$$

(31)

The cache contention is extended accordingly:

$$con^G : \mathbb{V} \to \mathbb{N}$$

(32)

$$con^{G}(v) = \max_{\pi = [v_{s}, \dots, v]} (con(v, \pi))$$

(33)

An upper-bound of both metrics for each access can be computed through a forward data flow analysis. The reuse distance analysis uses the maximum of the possible values on path convergence. Similarly, we lift the definition of the forward reuse distance to control-flow graphs. It can be computed through a backward data flow analysis. The contention for each block at each point in the program is computed through a forward data flow analysis. The computation of the contention relies on the estimation of the set of contending cache blocks. Its analysis domain is more complex than the reuse distance as different sets of contending blocks may arise on different paths. The analysis tracks all such sets from incoming paths, as long as they are conclusive to a

potential cache hit, i.e. all sets are smaller than the associativity of the cache, and not included into each other, i.e. one does not upper-bound the other.

We then traverse the unrolled control-flow graph in reverse post-order, compute the distributions with the contention-based approach, and use the maximum distribution on path convergence, with the maximum operator  $\odot$  as the join operator.

#### 4.4 Selection of relevant blocks

The selection of relevant blocks in Altmeyer and Davis (2014) also needs to be modified to accommodate for a control-flow graph. Cache state enumeration is only performed for relevant accesses, ensuring more precise analysis results for the selected accesses. Earlier work (Altmeyer and Davis 2014) relied on an absolute set of R relevant blocks for the whole trace. Instead, we only restrict ourselves to at most R relevant blocks at any point in the program. Given a position in the control-flow, the heuristic tracks the R blocks with the shortest lifespan, i.e. the shortest distance between their last and next access. Such accesses are among the most likely to be kept in the cache and benefit from a precise estimate of their hit probability through state enumeration. Note that this heuristic relies on a lower bound on the lifespan of blocks instead of an upper bound.

The *R* blocks with the smallest lifespan are analysed using the collecting semantics, as they are the most likely to be kept in cache. For each of these blocks *b*, the access prior to *b* must ensure its insertion in the cache during analysis. As such, the access needs to be marked as relevant, included in the *relevant\_accesses* set, and excluded from accesses contributing to contention. The computation of cache contention is modified to account for relevant accesses instead of blocks:

$$con(e_i, t) = \begin{cases} \infty & \text{if } rd(e_i, t) = \infty \\ |\{e_k | k \in conS(e_i, t) \land k \notin relevant\_accesses\}| + R & \text{otherwise} \end{cases}$$

(34)

#### 4.5 Approximation of cache states

We assume no information about the probability of taking one path or another, hence the join operator must combine cache states in such a way that the resulting state is an over-approximation of all incoming paths, i.e. it contains the same or degraded information. To capture this property, we introduce the partial ordering  $\sqsubseteq$  between a cache state and a set thereof such that  $s \sqsubseteq S_b$  implies that  $S_b$  holds more pessimistic information than s, resulting in more pessimistic timing estimates. We overload this operator to relate sets of cache states where  $S_a \sqsubseteq S_b$  implies that  $S_b$  holds more pessimistic information than  $S_a$ . More formally, the  $\sqsubseteq$  notation (Peleska and Löding 2008) identifies  $S_b$  as an upper-bound of  $S_a$  in  $2^{\mathbb{CS}}$ .

Consider a simple cache state  $s = (\{a, b\}, 0.5, \mathcal{D})$ . Intuitively, the information represented by  $s_a = (\{a\}, 0.5, \mathcal{D})$  is more pessimistic than that captured by  $s, s \sqsubseteq s_a$ .

Conversely,  $s_c = (\{a, c\}, 0.5, \mathcal{D})$  holds less pessimistic information regarding c, so  $s \not\sqsubseteq s_c$ . The set  $S = \{(\{a\}, 0.25, \mathcal{D}), (\{b\}, 0.25, \mathcal{D})\}$  also approximates  $s, s \sqsubseteq S$ ; the knowledge that a and b are both present in the cache (s) is reduced to guarantees only about the presence of either a or b in S. As a consequence, the sequence of accesses abab will trigger more misses starting from states in S, than from state s. Assuming  $\mathcal{D} < \mathcal{D}'$ , then  $s' = (\{a, b\}, 0.5, \mathcal{D}')$  holds more pessimistic information than  $s, s \sqsubseteq s'$ .

The intuition behind the approximation of a cache state is that the information it captures is further diluted into a single cache state or a set of cache states. The relation  $s \sqsubseteq S$  holds if the set of cache states S approximates cache state  $s = (C, P, \mathcal{D})$ . In other words, (i) S is as likely to occur, (ii) all blocks known to be in states of S are present in s, and (iii) the contribution of S to the pWCET is greater than or equal to the contribution  $\mathcal{D}$  of s. We formally define  $s \sqsubseteq S$  as follows:

$$(C, P, \mathcal{D}) \sqsubseteq S \Rightarrow \left(P = \left(\sum_{(C', P', \mathcal{D}') \in S} P'\right)\right) \land \left(\forall (C', P', \mathcal{D}') \in S, C \supseteq C' \land \mathcal{D} \leq \mathcal{D}'\right)$$

(35)

By extension, the over-approximation of a set of cache states is the composition of approximations  $F(s) \in 2^{\mathbb{CS}}$  of each element s in the set. We formally define the  $\sqsubseteq$  partial ordering between sets of cache states  $S_a \in 2^{\mathbb{CS}}$  and  $S_b \in 2^{\mathbb{CS}}$  as follows:

$$S_a \sqsubseteq S_b \Rightarrow \exists F : \mathbb{CS} \to 2^{\mathbb{CS}}, (\forall s \in S_a, s \sqsubseteq F(s)) \land S_b = \biguplus_{s \in S_a} F(s)$$

(36)

A join function  $\sqcup$  is valid if given any set of cache states  $S_a \in 2^{\mathbb{CS}}$  and  $S_b \in 2^{\mathbb{CS}}$ ,  $S_a \sqsubseteq (S_a \sqcup S_b)$  and  $S_b \sqsubseteq (S_a \sqcup S_b)$ . An optimal join function  $\sqcup$  should return the least upper-bound of its parameters, i.e. the smallest state which upper-bounds all its inputs. Our definition of the  $\sqsubseteq$  operator is however independent of the executed path:  $S_a$  and  $S_b$  may admit multiple upper-bounds incomparable to each other. The definition of an optimal join function would require a more complete ordering, taking into account the upcoming sequence of accesses to order sets of cache states depending on the likelihood their contents are reused. Optimality would still be challenged in multiple path applications where different paths stem from the join.

To prove over-approximation results in more pessimistic timing estimates, we derive the execution time distribution of a trace t using the set of input cache states S from its definition for a single state and the concatenation of traces respectively in (21) and (22):

$$\mathcal{D}(t,S) = \sum_{(C',P',\mathcal{D}')\in S} P' \cdot (\mathcal{D}' \otimes \mathcal{D}(t,C'))$$

(37)

where the sum of distributions and the product of a distribution with P are defined as per (6), and  $\otimes$  is the convolution of distributions.

The definition of over-approximations and their contribution to the execution time distribution of a trace relies on the merge  $\uplus$  and convolution  $\otimes$  operators defined respectively in (6) and (20). Both offer properties used in the evaluation of the con-

tribution of their operands. The convolution operator preserves the relative ordering between its inputs, and the merge operation adds the contribution of its operands.

**Lemma 1** The convolution operation preserves the ordering between execution time distributions:

$$\mathcal{D} \leq \mathcal{D}' \Rightarrow \mathcal{D} \otimes \mathcal{A} \leq \mathcal{D}' \otimes \mathcal{A}$$

Proof See Appendix.

**Lemma 2** The contributions of merged sets of cache states S and A is the sum of their individual contributions:

$$\forall t, \mathcal{D}(t, S) + \mathcal{D}(t, A) = \mathcal{D}(t, S \uplus A)$$

Proof See Appendix.

**Theorem 4** The over-approximation  $S_b$  of a set of cache states  $S_a$  holds more pessimistic information than  $S_a$ ,

$$\forall t, S_a \sqsubseteq S_b \Rightarrow \mathcal{D}(t, S_a) < \mathcal{D}(t, S_b)$$

*Proof* The relation between  $S_b$  and  $S_a$ , defined in (36), implies the existence of an approximation function F for the cache states in  $S_a$  such that:

$$(\forall s \in S_a, s \sqsubseteq F(s)) \land S_b = \biguplus_{s \in S_a} F(s)$$

(38)

From (38) and (35), we know that each cache contents C' in the approximation  $F(s) = (C', P', \mathcal{D}')$  is included in the contents C of cache state  $s = (C, P, \mathcal{D})$ . C' can thus be derived by evicting blocks from C. From Theorem 1 we can infer:

$$\forall (C, P, \mathcal{D}) \in S_a, \forall (C', P', \mathcal{D}') \in F((C, P, D)), \mathcal{D}(t, C) \le \mathcal{D}(t, C') \tag{39}$$

From Lemma 1, we can convolve both sides of the inequality with the same distribution  $\mathcal{D}$ :

$$\forall (C, P, \mathcal{D}) \in S_a, \forall (C', P', \mathcal{D}') \in F((C, P, D)), \mathcal{D} \otimes \mathcal{D}(t, C) \leq \mathcal{D} \otimes \mathcal{D}(t, C') \tag{40}$$

Approximate distributions  $\mathcal{D}'$  in F(s) are also by definition greater than their counterpart  $\mathcal{D}$  in s. We can similarly factor  $\mathcal{D}(t, C)$  into both sides of inequality  $\mathcal{D} \leq \mathcal{D}'$ :

$$\forall (C, P, \mathcal{D}) \in S_a, \forall (C', P', \mathcal{D}') \in F((C, P, D)), \mathcal{D} \otimes \mathcal{D}(t, C') \leq \mathcal{D}' \otimes \mathcal{D}(t, C')$$

(41)

By transitivity of the  $\leq$  operator, we can compare the contribution to the execution time distribution of  $s = (C, P, \mathcal{D})$  and each of the corresponding approximations in

F((C, P, D)). That is a comparison between the leftmost term in (40) and rightmost term in (41) through  $\mathcal{D} \otimes \mathcal{D}(t, C')$ :

$$\forall (C, P, D) \in S_a, \forall (C', P', D') \in F((C, P, D)), D \otimes D(t, C) \leq D' \otimes D(t, C')$$

(42)

We multiply both sides of the inequality by the positive occurrence probability P':

$$\forall (C, P, \mathcal{D}) \in S_a, \forall (C', P', \mathcal{D}') \in F((C, P, D)), P' \cdot (\mathcal{D} \otimes \mathcal{D}(t, C))$$

$$\leq P' \cdot (\mathcal{D}' \otimes \mathcal{D}(t, C')) \tag{43}$$

The property holds for each approximation in F(s) and can be extended to their sum:

$$\forall (C, P, \mathcal{D}) \in S_a, \sum_{(C', P', \mathcal{D}') \in F((C, P, D))} P' \cdot (\mathcal{D} \otimes \mathcal{D}(t, C))$$

$$\leq \sum_{(C', P', \mathcal{D}') \in F((C, P, D))} P' \cdot \mathcal{D}' \otimes \mathcal{D}(t, C')$$

(44)

From (35) and (38), a state  $s \in S_a$  has the same occurrence probability as its approximation F(s):

$$\forall (C, P, \mathcal{D}) \in S_a, P \cdot (\mathcal{D} \otimes \mathcal{D}(t, C)) \leq \sum_{(C', P', \mathcal{D}') \in F((C, P, D))} P' \cdot \mathcal{D}' \otimes \mathcal{D}(t, C') \tag{45}$$

Both terms of the inequality correspond to the contribution of a set of cache states to the execution time distribution of trace t as per (37):

$$\forall (C, P, \mathcal{D}) \in S_a, P \cdot (\mathcal{D} \otimes \mathcal{D}(t, C)) \le \mathcal{D}(t, F((C, P, D))) \tag{46}$$

The property holds for any cache state  $s \in S_a$  and can be extended to their sum such that:

$$\sum_{(C,P,D)\in S_a} P \cdot (\mathcal{D} \otimes \mathcal{D}(t,C)) \le \sum_{s\in S_a} \mathcal{D}(t,F(s))$$

(47)

From Lemma 2, the inequality also holds for the merge  $\uplus$  across  $S_a$  of the approximations F(s):

$$\sum_{(C,P,D)\in S_a} P \cdot (\mathcal{D} \otimes \mathcal{D}(t,C)) \leq \mathcal{D}\left(t, \biguplus_{s\in S_a} F(s)\right)$$

By definition of  $S_b$  in (38) and the application of (37) to  $S_a$ , we conclude that:

$$\forall t \in \mathbb{T}, \mathcal{D}(t, S_a) \leq \mathcal{D}(t, S_b)$$

The  $\sqsubseteq$  relation defines a partial ordering between two sets of cache states  $S_a$  and  $S_b$ . Namely,  $S_a \sqsubseteq S_b$  implies that  $S_b$  holds more pessimistic information than  $S_a$ . In other words, the execution of any trace from  $S_b$  results in a larger execution time distribution than the execution of the same trace from  $S_a$ . This provides sufficient ground for the definition of a sound join operation, one that upper-bounds the upcoming contribution of cache states coming from different paths.

# 4.6 Join operation for cache collecting

We traverse the (directed acyclic) graph in reverse post-order and compute the set of cache states at each program point. The join operator  $\bigsqcup$  describes the combination of two data-flow states from two different sub paths.