This is a repository copy of *Hybrid architecture for shallow accumulation mode AlGaAs/GaAs heterostructures with epitaxial gates*.

White Rose Research Online URL for this paper: http://eprints.whiterose.ac.uk/88065/

Version: Accepted Version

## Article:

MacLeod, S.J., See, A.M., Hamilton, A.R. et al. (5 more authors) (2015) Hybrid architecture for shallow accumulation mode AlGaAs/GaAs heterostructures with epitaxial gates. Applied Physics Letters, 106. 012105 . ISSN 0003-6951

https://doi.org/10.1063/1.4905210

## Reuse

Unless indicated otherwise, fulltext items are protected by copyright with all rights reserved. The copyright exception in section 29 of the Copyright, Designs and Patents Act 1988 allows the making of a single copy solely for the purpose of non-commercial research or private study within the limits of fair dealing. The publisher or other rights-holder may allow further reproduction and re-use of this version - refer to the White Rose Research Online record for this item. Where records identify the publisher as the copyright holder, users can verify any specific terms of use on the publisher's website.

## Takedown

If you consider content in White Rose Research Online to be in breach of UK law, please notify us by emailing eprints@whiterose.ac.uk including the URL of the record and the reason for the withdrawal request.

## Hybrid architecture for shallow accumulation mode AlGaAs/GaAs heterostructures with epitaxial gates.

S. J. MacLeod,<sup>1</sup> A. M. See,<sup>1</sup> A. R. Hamilton,<sup>1, a)</sup> I. Farrer,<sup>2</sup> D. A. Ritchie,<sup>2</sup> J. Ritzmann,<sup>3</sup> A. Ludwig,<sup>3</sup> and A. D. Wieck<sup>3</sup>

<sup>1)</sup>School of Physics, University of New South Wales, Sydney, New South Wales 2052, Australia

<sup>2)</sup> Cavendish Laboratory, University of Cambridge, Cambridge, CB3 0HE, UK

<sup>3)</sup>Angewandte Festkörperphysik, Ruhr-Universität Bochum, D-44780 Bochum,

Germany

(Dated: 15 December 2014)

Accumulation mode devices with epitaxially grown gates have excellent electrical stability due to the absence of dopant impurities and surface states. We overcome typical fabrication issues associated with epitaxially gated structures (e.g. gate leakage and high contact resistance) by using separate gates to control the electron densities in the Ohmic and Hall bar regions. This hybrid gate architecture opens up a way to make ultrastable nanoscale devices where the separation between the surface gates and the 2D electron gas is small. In this work, we demonstrate hybrid devices made from the same wafer have reproducible electrical characteristics, with identical mobility and density traces over a large range of 2D densities. In addition, thermal cycling does not influence the measured electrical characteristics. As a demonstration of concept, we have fabricated a hybrid single-electron transistor on a shallow (50 nm) AlGaAs/GaAs heterostructure that shows clear Coulomb blockade oscillations in the low temperature conductance.

PACS numbers: 85.35.Gv, 73.63.Kv, 73.23.Hk, 85.30.-z Keywords: gallium arsenide, accumulation mode, SET, low resistance ohmic contacts

Much attention is focused on modulation doped Al-GaAs/GaAs devices which utilize an intentional doping layer to populate the 2D conducting channel. These type of devices are at the center of key experiments in semiconductor spintronics<sup>1</sup>, qubits<sup>2</sup> and many body effects<sup>3</sup>. However these devices may not be ideal for applications requiring high charge stability or low carrier densities: not only do the remote dopants act as scattering centers (particularly in shallow devices  $^{4}$ ), charge motion between dopants is a significant source of noise in quantum devices 5-7. Furthermore the surface gates can leak through the doping layer causing additional charge noise $^{8-10}$ . The alternative, accumulation-mode GaAs/AlGaAs heterostructures require a voltage applied to an overall top-gate<sup>11,12</sup> to induce carriers into the conduction channel, removing the need for intentional ionized dopants. Accumulation-mode devices are advantageous due to their charge stability<sup>13</sup> and robustness under thermal cycling<sup>14</sup>.

In most accumulation-mode devices the top-gate spans the entire conduction region and slightly overlaps the Ohmic contacts in order to effectively contact, and induce, a continuous 2D conducting region. However the close proximity of the contacts to the top-gate can cause electrical shorts between the two<sup>15–17</sup>. The shorting of the top-gate to the contacts is particularly problematic in shallow semiconductor-insulator-semiconductor field effect transistors  $(SISFETs)^{12}$  in which the top-gate is an in situ, degenerately-doped GaAs cap. In SISFETs a self-aligned Ohmic technique<sup>18</sup> is used to isolate the topgate from the contacts, but despite tight control of the Ohmic fabrication steps, top-gate leakage is still a major issue<sup>17</sup>. The problem of top-gate leakage is enhanced in shallow devices because the contacts are in close proximity to the *in situ* top-gate, due to a thinner insulating Al-GaAs region. Circumventing the top-gate leakage problem can be done with an alternative architecture whereby a metallic gate replaces the doped-cap. The metallic top-gate is isolated from the contacts by an amorphous dielectric layer in a metal-insulator-semiconductor field effect transistor (MISFET) configuration<sup>15,19</sup>. Furthermore MISFETs are advantageous because dual-gating is possible by using two metallic gates (with insulating layers in between) to either realize sub-micron features in accumulation-mode devices 20-22, or to independently control the accumulation layers near the contacts and in the conducting channel.<sup>23,24</sup>. The advantages introduced by the MISFET design come at the cost of using an amorphous dielectric which can cause charge noise<sup>19,25</sup>. Additionally surface states on the wafer can cause scattering even in  $300 \,\mathrm{nm}$  deep devices<sup>26</sup>.

Here we demonstrate a hybrid device which combines the benefits of the MISFET and SISFET deigns: like MISFETs the hybrid architecture is simple to fabricate with a high yield and the design is compatible with both shallow and deep devices. Like some dual gated MIS

<sup>&</sup>lt;sup>a)</sup>Electronic mail: Alex.Hamilton@unsw.edu.au

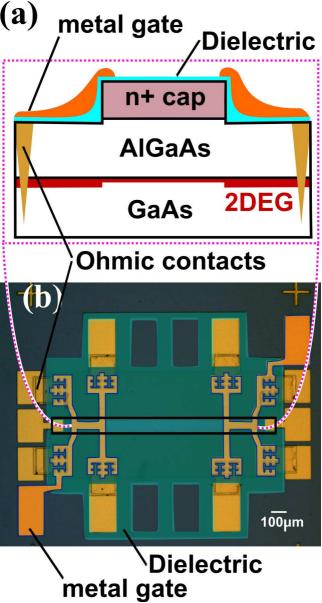

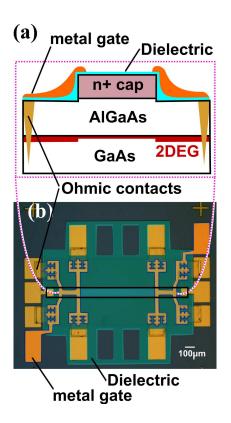

FIG. 1. (Color online) (a) A vertical profile of the hybridarchitecture is shown for a slice of the device shown in (b). The 2DEG is depicted with thick and thin lines representing the high density of electrons induced near the contacts, and the lower (variable) density of electrons in the 2D conduction channel respectively. (b) A colored optical micrograph of the device is shown here, the conduction channel lies under the doped n+ GaAs top-gate (outlined in black). An insulating dielectric AlO<sub>x</sub> layer (light green) covers the top-gate isolating the top-gate from the metallic Ohmic gates which sit on top (colored orange). The dark blue box shows the location of one of the Ohmic contacts which lie under the Ohmic gates and dielectric. The bonding pads are shown in gold.

devices, the hybrid device has independent control of the contact and channel resistance; like SISFETs the active region of the hybrid device is all high-quality singlecrystal with a heavily doped GaAs cap that eliminates the deleterious effects of surface charge and amorphous dielectrics. Furthermore standard nanostructure fabrication steps<sup>14,27</sup> can be incorporated into the hybrid device fabrication. The hybrid architecture retains the benefits of MIS and SIS structures by spatially separating the top-gate from the contacts using a dual gating scheme composed of two different materials. A degenerately doped GaAs cap is used as a top-gate similar to SISFETs, and metallic gates are deposited on top of a dielectric layer like MIS structures (see Fig. 1(b)). The carrier density near the contacts is controlled by metal ('Ohmic') gates which are deposited on an amorphous dielectric away from the active device region. The top-gate leakage is reduced by spatially separating the Ohmic con-

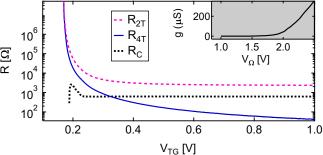

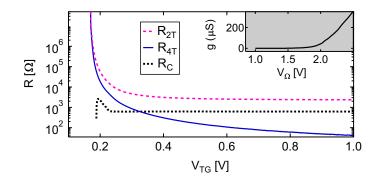

FIG. 2. (Color online) Contact resistance, two- and fourterminal resistance versus the voltage applied to the top-gate  $(V_{TG})$  is shown for the 160 nm deep device. A constant voltage is applied to the Ohmic gates  $(V_{\Omega} = 2.5 \text{ V})$  while  $V_{TG}$  is varied. The contact resistance is independent of  $V_{TG}$ . Inset: two-terminal conductance versus  $V_{\Omega}$  for one of the 160 nm deep devices when the top-gate is held fixed at  $V_{TG} = 1 \text{ V}$ . The ohmic gates can 'turn off' the channel independently of the top-gate.

tacts from the *in situ* GaAs top-gate, thus increasing the yield and simplifying the fabrication process. Additionally the independently-gated Ohmic regions ensure low density measurements are limited by the sample and not the contact resistance.

Figure 1(a) shows a side-profile schematic of a typical hybrid device. We fabricate both deep and shallow devices, the 'depth' of a device being defined as the thickness of the AlGaAs region. The deep (shallow) W0773 (B14507) heterostructure consists of a 160 nm (50 nm)AlGaAs layer on a GaAs buffer to form the 2DEG interface, followed by 25 nm (10 nm) of undoped GaAs spacer, and a  $35 \,\mathrm{nm}$  ( $31 \,\mathrm{nm}$ ) n+ doped cap. Optical lithography and a deep wet etch > 220 nm (> 91 nm) define the mesa then a shallow wet etch of the n+ cap is used to pattern the top-gate. A false color optical micrograph of a complete device is shown in Fig. 1(b), the top-gate region is outlined in red. Two gold bond pads contact the top-gate. NiAuGe Ohmic contacts are made to the 2DEG and a 30 nm layer of aluminum oxide (blue)<sup>28,29</sup> isolates the device from the Ti/Au ohmic gates (orange) deposited on the surface.

The behavior of the contact and channel resistances are first characterized at 4 K in a dc dip station using standard four-terminal ac lockin techniques, with an excitation voltage of 100  $\mu$ V. The hybrid device operates by applying a fixed voltage to the Ohmic gates ( $V_{\Omega} = 2.5$  V) to minimize the contact resistance. The resistance of the 2D channel is controlled by applying a separate voltage bias to the *in situ* top-gate ( $V_{TG}$ ) and the maximum topgate voltage ( $V_{TG;max}$ ) is chosen so the leakage current between the Ohmic contacts and top-gate is  $\leq 10$  pA (the resolution limit of the Source Measure Unit SMU) when  $V_{\Omega} = 2.5$  V. For the deep device  $V_{TG;max} = 1$  V and for the shallow device  $V_{TG;max} = 0.5$  V.

Figure 2 is a plot of the two-terminal  $(R_{2T})$ , four-

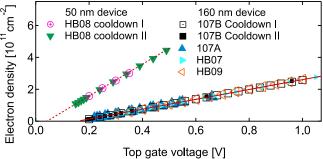

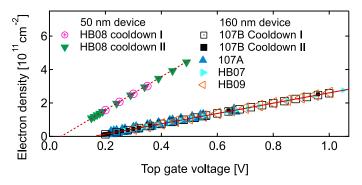

FIG. 3. (Color online) Electron density versus top-gate voltage for four deep devices and one shallow device. The density is identical for four different deep devices, and between thermal cycles both shallow and deep devices have reproducible density traces. The dashed and solid lines are lines of best fit for the shallow and deep devices respectively.

terminal  $(R_{4T})$  and contact  $(R_C)$  resistances for the deep device 107B, and are representative of the traces obtained for other deep and shallow devices. Independent control of the channel resistance and contact resistance are evident in the dependence of  $R_C$  and  $R_{4T}$  on the top-gate voltage as the contact resistance is flat over a large range of top-gate voltages (the small upturn at low  $V_{TG}$  is probably an artifact of subtracting two large numbers  $R_{4T}$ and  $R_{2T}$  to get  $R_C$ ). The channel resistance however, is dependent upon the top-gate voltage and decreases as  $V_{TG}$  increases. The two terminal resistance is the sum of all resistances from the source to the drain ohmics and follows a trend reflecting the sum of  $R_{4T}$  and  $R_{C}$ as expected. Independent control of the Ohmic gate is demonstrated in the inset to Figure 2, here the top-gate bias is fixed at  $V_{TG} = 1 \,\mathrm{V}$  while  $V_{\Omega}$  is swept from 2.5 V down to 1 V. Although the channel is conducting when  $V_{TG} = 1 \,\mathrm{V}$ , as  $V_{\Omega}$  is reduced  $R_C$  increases correspondingly, until it comes to dominate the total resistance between the source and drain, resulting in the two-terminal conductance decreasing to zero.

The 2D electron density  $(n_s)$  and mobility  $(\mu)$  are measured at low temperatures in a <sup>3</sup>He cryostat with a base temperature of 229 mK. The electron density is extracted from the slope of the Hall trace<sup>30</sup> at low magnetic field and is linearly dependent on  $V_{TG}$  as shown in Figure 3. The linear dependence of  $n_s$  is explained by treating the top-gate and 2D conducting channel as a simple parallel plate capacitor:  $n_s = C_g (V_{TG} - V_0)/e$  where  $C_g$  is the parallel capacitance between the top-gate and the 2D channel, and  $V_0$  is the gate bias at which  $n_s = 0$ . Both  $C_q$  and  $V_0$  should be the same for all devices made from the same wafer. However if any charge accumulates between the gate and the channel over time, or between thermal cycles this will be reflected as a shift up or down in the  $n_s$  versus  $V_{TG}$  traces<sup>31</sup>, and will result in different values of  $V_0$ . In MISFET devices, variations in charge trapped at the dielectric-GaAs interface can cause variations in  $V_0$  from one cool down to the next.

However in SISFET structures the variation in  $V_0$  should be much smaller as only the reconfiguration of a (small) number of charges in the undoped AlGaAs can affect  $V_0$ . For each of the deep devices measured, with one device being measured on two separate cool-downs from roomtemperature, all of the density traces lie on top of each other indicating any variation in charge trapped in the dielectric layer or elsewhere is not interfering with the applied gate potential in any of the deep devices measured. Lines of best fit for the 160 nm deep devices are  $n_s = (\{3.08, 3.09, 3.16, 3.10, 3.14\} \times 10^{11} \text{cm}^{-2}/\text{V}) V_{TG}$  $-(\{0.49, 0.48, 0.50, 0.49, 0.51\}) \times 10^{11} \text{cm}^{-2}$  for devices 107A, 107B (first cooldown), 107B (after thermal cycling), HB07 and HB09 respectively. The y-intercept bis proportional to  $V_0^{32}$ , from the average b we calculate  $V_0 = 0.13 \pm 0.001 \text{ V}^{33}$ . The 1 mV error is less than the stability of the source meter unit<sup>34</sup> used to bias the top-gate. The electron density of the shallow device HB08 was varied over the range  $9.86 \times 10^{10} \text{ cm}^{-2}$  to  $4.44 \times 10^{11} \text{ cm}^{-2}$ . with a line of best fit  $n_s = (-0.40 + 9.86V_{TG}) \times 10^{11} \text{ cm}^{-2}$ . The line of best fit to the density for the shallow 50 nmdevice has a gradient  $\sim 3$  times larger than that of the deep device as expected since the top-gate of the shallow  $50\,\mathrm{nm}$  device is  $\sim$  3 times closer to the 2DEG than the deep device.

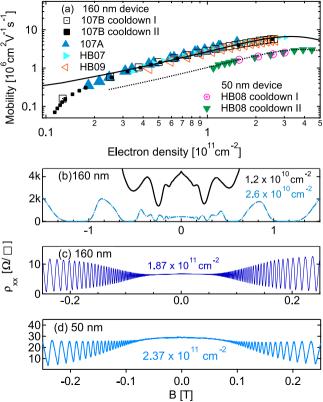

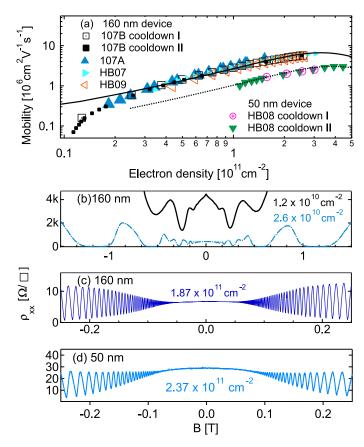

Figure 4 shows the density dependent mobility for each of the devices measured. The mobility traces are highly reproducible, they lie on top of each other for devices made from the same wafer, and are stable when the devices are thermal cycled. We investigate the dominant scattering mechanism in the 2DEG by fitting a power-law exponent to the  $\mu$  versus  $n_s$  traces<sup>4</sup> ( $\mu \propto n_s^{\alpha}$ ). The 160 nm device has  $\alpha = 1.1$ , suggesting background impurities limit the mobility<sup>4</sup>. Detailed transport modeling<sup>26</sup> confirms a higher level of background impurities in the shallow 50 nm wafer<sup>35</sup> explaining the lower mobility. The deep (160 nm) and shallow (50 nm) devices are grown in different MBE chambers with different impurity concentrations, which is why they have different mobilities.

Accumulation-mode devices, with reproducible transport properties and low  $R_c$  at low  $n_s$  are promising candidates to study the effects of disorder and interactions in the low density regime<sup>36</sup>, where interactions are strongest. Indeed Figs. 4 (b) to (d) show clean, symmetric Shubnikov de Haas (SdH) oscillations for low and high electron densities in both shallow and deep devices, indicating there is no parallel conduction, and the clean traces down to low density for the deep device show the ohmic resistance is not dominating the  $\rho_{xx}$  traces.

Clean, symmetric SdH are shown in Fig. 4(d) for the lowest measured density  $(n_s = 1.2 \times 10^{10} \,\mathrm{cm}^2)$  in the deep device HB08. Such low density SdH are possible due to the ohmic resistance remaining constant so that the operating range of the device is limited by the intrinsic properties of the conducing channel and not the resistance of the ohmic contacts. Indeed the SdH remain smooth as the sample undergoes a transition from quantum Hall liquid to insulator<sup>37</sup> at  $B = \pm 0.5 \,\mathrm{T}$  ( $\nu \lesssim 1$ ),

FIG. 4. (Color online) (a) Electron mobility versus electron density for four different deep devices and one shallow device. The mobility is reproducible for different devices and between thermal cycles when fabricated from the same wafer. The black dashed (solid) line is a fit to the mobility for the shallow 50 nm (deep 160 nm) device in the weak scattering limit ( $k_f \ell \geq 10$ , where  $\ell$  is the mean free path). (b) Low and (c) high density Shubnikov de Haas oscillations appear in the longitudinal resistance ( $\rho_{xx}$ ) for deep device 107B and are representative of the traces in other deep devices. The trace in (d) shows data from the shallow device HB08.

where  $\rho_{xx}$  increases over five orders of magnitude (the complete  $\rho_{xx}$  trace is not shown).

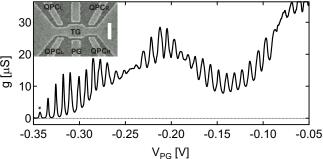

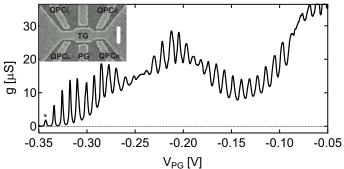

Combining the hybrid architecture with nanostructures is a reliable alternative to fabricating SISFET nanostructures. SISFET and hybrid nanostructures have identical fabrication steps<sup>14</sup>, and thus the advantages of SISFET devices are retained by hybrid devices, with the additional benefits of reliable fabrication and low contact resistance. Here we demonstrate a quantum dot (QD) fabricated with the hybrid architecture (see Fig. 5). The QD is fabricated<sup>14</sup> on the deep 160 nm wafer, whereby the QD is defined by etching the n+ cap into seven separate gates forming a left quantum point contact (QPC), central dot region and right QPC in series, as shown inset to Fig. 5. The quantum dot and adjacent 2DEG reservoirs are populated using the top-gate, and the quantum point contacts at each end are used to control the tunnel

FIG. 5. A plot of the two-terminal conductance g versus plunger gate voltage  $V_{PG}$  of a quantum dot device made with the hybrid architecture. Measurement were performed with  $V_L = -0.34 \text{ V}, V_R = -0.28 \text{ V}, V_{TG} = 1.2 \text{ V}, V_{OG} = 2.5 \text{ V}$  at T = 40 mK with an ac excitation of  $30 \mu \text{V}$ . A SEM image of the device is shown as an inset with a scale bar of 500 nm.

barriers. Figure. 5 shows a series of Coulomb blockade oscillations when the bottom plunger gate is used to tune the dot occupancy. Coulomb blockade oscillations are manifested in the two terminal conductance g with clear zeros in g either side of the last peak (marked with a \* in Fig. 5).

In summary, a hybrid architecture is presented for both deep and shallow AlGaAs/GaAs heterostructures, which use both a metallic and an *in situ* epitaxial gate. Reproducible transport measurements demonstrate the devices are highly stable with measurements limited by the intrinsic properties of the wafer and not by the contact resistance. Furthermore we demonstrate nanostructures can be integrated into the hybrid architecture.

The authors would like to thank K. Das. Gupta for helpful discussions. This project is supported by the Australian Government under the Australia-India Strategic Research Fund and by the Australian Research Council (ARC) DP scheme. A.R.H. acknowledges an ARC Outstanding Researcher Award. Devices were fabricated using the facilities at the NSW Node of the Australian National Fabrication Facility (ANFF). J.R., A.L. and A.D.W. acknowledge support from Mercur Pr-2013-0001, BMBF - Q.com-H 16KIS0109, and DFH/UFA CDFA-05-06.

- <sup>1</sup>J. Wunderlich, B.-G. Park, A. C. Irvine, L. P. Zârbo, E. Rozkotová, P. Nemec, V. Novák, J. Sinova, and T. Jungwirth, Science **330**, 1801 (2010).

- <sup>2</sup>R. Hanson, L. P. Kouwenhoven, J. R. Petta, S. Tarucha, and L. M. K. Vandersypen, Rev. Mod. Phys. **79**, 1217 (2007).

- <sup>3</sup>M. J. Iqbal, R. Levy, E. J. Koop, J. B. Dekker, J. P. de Jong, J. H. M. van der Velde, D. Reuter, A. D. Wieck, R. Aguado,

- Y. Meir, and C. H. van der Wal, Nature **501**, 79 (2013). <sup>4</sup>D. Laroche, S. Das Sarma, G. Gervais, M. P. Lilly, and J. L.

- Reno, Appl. Phys. Lett. **96**, 162112 (2010).

- <sup>5</sup>T. Fujisawa and Y. Hirayama, Appl. Phys. Lett. **77**, 543 (2000).

- <sup>6</sup>C. Kurdak, C.-J. Chen, D. C. Tsui, S. Parihar, S. Lyon, and G. W. Weimann, Phys. Rev. B. **56**, 9813 (1997).

- <sup>7</sup>G. Timp, R. E. Behringer, and J. E. Cunningham, Phys. Rev. B. 42, 9259 (1990).

- <sup>8</sup>D. H. Cobden, A. Savchenko, M. Pepper, N. K. Patel, D. A.

Ritchie, J. E. F. Frost, and G. A. C. Jones, Phys. Rev. Lett. **69**, 502 (1992).

- <sup>9</sup>M. Pioro-Ladrière, J. H. Davies, A. R. Long, A. S. Sachrajda, L. Gaudreau, P. Zawadzki, J. Lapointe, J. Gupta, Z. Wasilewski, and S. Studenikin, Phys. Rev. B **72**, 115331 (2005).

- <sup>10</sup>C. Buizert, F. H. L. Koppens, M. Pioro-Ladrière, H.-P. Tranitz, I. T. Vink, S. Tarucha, W. Wegscheider, and L. M. K. Vandersypen, Phys. Rev. Lett. **101**, 226603 (2008).

- <sup>11</sup>P. M. Solomon, T. W. Hickmott, H. Morkoç, and R. Fischer, Applied Physics Letters **42**, 821 (1983).

- <sup>12</sup>K. Matsumoto, M. Ogura, T. Wada, N. Hashizume, T. Yao, and Y. Hayashi, Electron. Lett **20**, 462 (1984).

- <sup>13</sup>O. Klochan, W. R. Clarke, R. Danneau, A. P. Micolich, L. H. Ho, A. R. Hamilton, K. Muraki, and Y. Hirayama, Appl. Phys. Lett. 89, 092105 (2006).

- <sup>14</sup>A. M. See, O. Klochan, A. R. Hamilton, A. P. Micolich, M. Aagesen, and P. E. Lindelof, Appl. Phys. Lett. **96**, 112104 (2010).

- <sup>15</sup>W. Y. Mak, F. Sfigakis, K. Das Gupta, O. Klochan, H. E. Beere, I. Farrer, J. P. Griffiths, G. A. C. Jones, A. R. Hamilton, and D. A. Ritchie, Appl. Phys. Lett. **102**, 103507 (2013).

- <sup>16</sup>T. Saku, K. Muraki, and Y. Hirayama, Jpn. J. Appl. Phys. 37, L765 (1998).

- <sup>17</sup>S. J. Sarkozy, K. D. Guptaa, F. Sfigakisa, H. E. Beere, I. Farrer, R. Harrell, D. Ritchie, and G. Jones, ECS Trans. **11**, 75 (2007).

- <sup>18</sup>B. E. Kane, L. N. Pfeiffer, K. W. West, and C. K. Harnett, Appl. Phys. Lett. **63**, 2132 (1993).

- <sup>19</sup>W. Y. Mak, K. D. Gupta, H. E. Beere, I. Farrer, F. Sfigakis, and D. A. Ritchie, Appl. Phys. Lett. **97**, 242107 (2010).

- <sup>20</sup>S. Sarkozy, K. D. Gupta, C. Siegert, A. Ghosh, M. Pepper, I. Farrer, H. E. Beere, D. A. Ritchie, and G. A. C. Jones, Appl. Phys. Lett. **94**, 172105 (2009).

- <sup>21</sup>W. H. Lim, F. A. Zwanenburg, H. Huebl, M. Mottonen, K. W. Chan, A.Morello, and A. S. Dzurak, Appl. Phys. Lett. **95**, 242102 (2009).

- <sup>22</sup>S. J. Angus, A. J. Ferguson, A. S. Dzurak, and R. G. Clark, Nano Lett. 7, 2051 (2007).

- <sup>23</sup>L. H. W. van Beveren, K. Y. Tan, N. S. Lai, A. S. Dzurak, and A. R. Hamilton, Appl. Phys. Lett. **97**, 152102 (2010).

- <sup>24</sup>R. H. Harrell, K. S. Pyshkin, M. Y. Simmons, D. A. Ritchie, C. J. B. Ford, G. A. C. Jones, and M. Pepper, Appl. Phys. Lett. 74, 2328 (1999).

- <sup>25</sup>J. H. Davies and I. A. Larkin, Phys. Rev. B **49**, 4800 (1994).

- <sup>26</sup>D. Q. Wang, J. C. H. Chen, O. Klochan, K. Das Gupta, D. Reuter, A. D. Wieck, D. A. Ritchie, and A. R. Hamilton, Phys. Rev. B 87, 195313 (2013).

- <sup>27</sup>A. M. See, I. Pilgrim, B. C. Scannell, R. D. Montgomery, O. Klochan, A. M. Burke, M. Aagesen, P. E. Lindelof, I. Farrer, D. A. Ritchie, R. P. Taylor, A. R. Hamilton, and A. P. Micolich, Phys. Rev. Lett. **108**, 196807 (2012).

- <sup>28</sup>M. J. Biercuk, D. J. Monsma, C. M. Marcus, J. S. Becker, and R. G. Gordon, Applied Physics Letters 83, 2405 (2003).

- $^{29}\mathrm{We}$  obtain similar values for the dielectric constant and breakdown field (at room temperature) as in Ref.  $^{28}$ . With a dielectric constant  $\sim 13$  and a breakdown field of  $4.2\,\mathrm{MV/cm}.$

- <sup>30</sup>See supplementary information for Hall traces.

- <sup>31</sup>O. A. Tkachenko, V. A. Tkachenko, D. G. Baksheyev, K. S. Pyshkin, R. H. Harrell, E. H. Linfield, D. A. Ritchie, and C. J. B. Ford, Journal of Applied Physics **89**, 4993 (2001).

- <sup>32</sup> Using a parallel plate capacitor model the density can be written as:  $n_s = \epsilon_r \epsilon_0 (V_{TG} - V_0)/ed$ . Here the dielectric constant for GaAs is  $\epsilon_r = 12.7$ , e is the charge of an electron and d = 185 nm is the distance from the 2DEG to the top gate for the deep 160 nm device. The y-intercept  $b = \epsilon_r \epsilon_0 V_0/ed$ .

- $^{33}$   $V_0 = ed/\epsilon_r \epsilon_0 b$ , where  $b = \{0.49, 0.48, 0.50, 0.49, 0.51\} \times 10^{11} {\rm cm}^{-2}$ . The mean value for  $V_0$  is  $0.13 \pm 0.001 \, {\rm V}$ . The standard error of the mean is calculated by  $s/\sqrt{n} = 1 \, {\rm mV}$ , where  $s = 0.00308 \, {\rm V}$  is the standard deviation, and n = 5 is the number of points.

- <sup>34</sup> The reported limit to the reproducability/stability of the SMU,  $\ell_{SMU} = 2 \, mV$  (2400 Series SourceMeter Users Manual, Keithley Instruments, Inc. Cleveland, Ohio, U.S.A., Seventh Printing, May 2002 Document Number: 2400S-900-01 Rev. G).

- <sup>35</sup> Reference [27] describes the model and fitting parameters used. The 50 nm (160 nm) device is fit using a background impurity density in the AlGaAs layer of  $N_{AlGaAs} = 7.8(3) \times 10^{20} \text{ m}^{-3}$  and a thickness  $d_{AlGaAs} = 50$  (160) nm;  $N_{GaAs} = 2.6(1) \times 10^{20} \text{ m}^{-3}$ in the GaAs buffer layer ( $d_{GaAs} = 1 \mu \text{m}$  for both devices); the surface charge density is set to zero in both cases and the interface roughness parameters are  $\Lambda = 1.4$  (1.25) nm (correlation length) and  $\Delta = 2.8(2.5)$  Å (roughness amplitude).

- <sup>36</sup>W. R. Clarke, C. E. Yasin, A. R. Hamilton, A. P. Micolich, M. Y. Simmons, K. Muraki, Y. Hirayama, M. Pepper, and D. A. Ritchie, Nat. Phys. 4, 55 (2008).

- <sup>37</sup>S. Kivelson, D.-H. Lee, and S.-C. Zhang, Phys. Rev. B 46, 2223 (1992).