This is a repository copy of *Future Energy Efficient Data Centers With Disaggregated Servers*.

White Rose Research Online URL for this paper: http://eprints.whiterose.ac.uk/123105/

Version: Accepted Version

# Article:

Mohammad Ali, HM, El-Gorashi, TEH, Lawey, AQ et al. (1 more author) (2017) Future Energy Efficient Data Centers With Disaggregated Servers. Journal of Lightwave Technology, 35 (24). pp. 5361-5380. ISSN 0733-8724

https://doi.org/10.1109/JLT.2017.2767574

© 2017 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

# Reuse

Unless indicated otherwise, fulltext items are protected by copyright with all rights reserved. The copyright exception in section 29 of the Copyright, Designs and Patents Act 1988 allows the making of a single copy solely for the purpose of non-commercial research or private study within the limits of fair dealing. The publisher or other rights-holder may allow further reproduction and re-use of this version - refer to the White Rose Research Online record for this item. Where records identify the publisher as the copyright holder, users can verify any specific terms of use on the publisher's website.

# Takedown

If you consider content in White Rose Research Online to be in breach of UK law, please notify us by emailing eprints@whiterose.ac.uk including the URL of the record and the reason for the withdrawal request.

eprints@whiterose.ac.uk https://eprints.whiterose.ac.uk/

# Future Energy Efficient Data Centers with Disaggregated Servers

Howraa M. Mohammad Ali, Taisir E. H. El-Gorashi, Ahmed Q. Lawey, and Jaafar M. H. Elmirghani

Abstract—The popularity of the Internet and the demand for 24/7 services uptime is driving system performance and reliability requirements to levels that today's data centers can no longer support. This article examines the traditional monolithic conventional server (CS) design and compares it to a new design paradigm: the disaggregated server (DS) data center design. The DS design arranges data centers resources in physical pools, such as processing, memory, and IO module pools, rather than packing each subset of such resources into a single server box. In this work, we study energy efficient resource provisioning and virtual machine (VM) allocation in DS-based data centers compared to CS-based data centers. First, we present our new design for the photonic DS-based data center architecture, supplemented with a complete description of the architectural components. Second, we develop a mixed integer linear programming (MILP) model to optimize VM allocation for the DS-based data center, including the data center communication fabric power consumption. Our results indicate that, in DS data centers, the optimum allocation of pooled resources and their communication power yields up to 42% average savings in total power consumption when compared with the CS approach. Due to the MILP high computational complexity, we developed an energy efficient resource provisioning heuristic for DS with communication fabric (EERP-DSCF), based on the MILP model insights, with comparable power efficiency to the MILP model. With EERP-DSCF, we can extend the number of served VMs where the MILP model scalability for a large number of VMs is challenging. Furthermore, we assess the energy efficiency of the DS design under stringent conditions by increasing the CPU to memory traffic and by including high non-communication power consumption to determine the conditions at which the DS and CS designs become comparable in power consumption. Finally, we present a complete analysis of the communication patterns in our new DS design and some recommendations for design and implementation challenges.

Index Terms— Disaggregated Server, Data Center, Silicon Photonics, Energy Efficiency, Resource Provisioning, Data Center Communication Fabric.

#### I. INTRODUCTION

VIRTUALIZED data centers provide key efficient services to clients with variable requirements. However, today's

The authors are from the School of Electronic and Electrical Engineering, University of Leeds, Leeds LS2 9JT, U.K.

data center architectures are rigid in that they are composed of "server boxes", where each box has a predetermined ratio of CPU to memory to I/O that is unchangeable [1]. The single box server adds barriers and difficulties, including inefficient resource utilization, prolonged provisioning, and difficulties in big data management, as well as a high risk of blocking when deploying virtual data center resource instances. To understand the usefulness of the DS concept, consider the example of a conventional 'server in a box' (CS), where a processing intensive task occupies the processor while the input-output (IO) module is idle. Such an idle resource cannot be accessed in this case by other servers due to the current CS constrained architecture. Similarly, a server running an application involving intensive IO usage may have a large idle fraction of the CPU processing capability not accessible by other tasks that require access through the bottleneck IO module. The DS concept removes the barriers of the CS approach and allows VMs to construct servers on the fly with the required specifications for a specific duration and release these resources at the end of the task, thus removing many barriers and improving data center efficiency significantly.

Another challenge facing current data centers is the energy consumption of the physical infrastructure that provides resources for the cloud. Thus, energy management is a key challenge for data centers in reducing all their energy related costs [2, 3].

Significant efforts have been dedicated to optimizing the power consumption of conventional data centers, including energy efficient data center designs [4, 5], energy efficient inter- and intra-data center network architectures [6-8], designing energy efficient cloud computing services [9], [10], designing energy efficient network topologies [11], using renewable energy optimally [12], and introducing energy efficient resource provisioning and virtual network embedding for cloud systems [13].

The above work has a major shortcoming in that it relies on the single-boxed server approach, where flexible addition and removal of physical resources is very limited. Accordingly, in this paper, the disaggregated server (DS) architecture is considered as a potential approach to minimize data centers' power consumption. In this approach, servers' resources are separated into discrete pools of resources that are mixed and matched in real time to create differently sized and shaped systems. This technique brings a new server vision for data centers and motivates a plethora of potential new applications and services [14].

The revolutionary concept of DS can bring about radical change to traditional data centers and can simplify the vertical scalability of virtual machines (VMs) by decoupling the server

Manuscript received January 2017; revised ...... This work was supported by the Engineering and Physical Sciences Research Council (EPSRC), INTERNET (EP/H040536/1), and STAR (EP/K016873/1). The first author would like to support the Higher Committee for Education Development in Iraq (HCED Iraq) for funding her PhD. All data is provided in full in the results section of this paper.

components from each other. On the other hand, resources are combined according to their types in a standalone and type homogenous "resource rack", constructing resource pools, where elements in the pool are interconnected using an optical backplane. Here, a data center network directly interconnects all resource racks via a high bandwidth and low latency interrack switching fabric [15]. Therefore, DS design introduces the sharing of CPU, memory, and network components' modularity and independent allocation of resources, such that a certain resource is no longer tightly coupled to any other resource, meaning that resources can be used more efficiently.

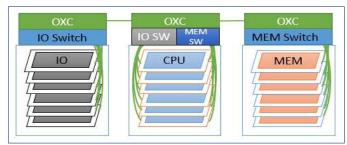

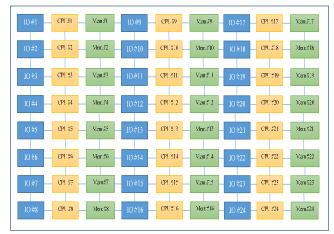

Fig. 1. DS concept.

Fig. 1 highlights the main concept of DS. In Fig. 1, we consider hybrid Electronic/Optical switching fabric in addition to the disaggregated resources pools. Therefore, resources in both the electronic IP layer (packet switched) and the optical layer (circuit switched) are needed. IP switches are needed to aggregate traffic from resources, and each IP switch is connected to an optical switch, which is connected to other optical switches by optical fiber links. Optical fibers provide the large capacity and fast data transmission required to support the communication between the disaggregated resources. Intel Silicon Photonic connectors (SiPh) [16] provide OEO processing for full wavelength conversion at each node. This architecture will be discussed in more detail in Section III, where we present the architecture of our DS design with a full description of all the components and communication patterns.

The main aim of this paper is to analyze the energy efficiency of the DS approach compared to CS using the MILP model and real-time heuristics. In addition, this paper gives a detailed description of the DS concept and provides a detailed architecture. In this work, we developed an energy efficient resource provisioning MILP model and simulation heuristic, considering the DS, and compared it to CS design. We accounted in our MILP model for the impact of the communication power on the total power saving and developed a heuristic which enables real time operation and verifies the MILP model. We have also designed a new switch-based communication architecture for the new DSbased data center.

It should be noted that the performance of the DS-based data center can be measured using several metrics and these include power consumption, latency, resilience, security, scalability and other metrics. It is not possible to study all these dimensions in a single article. Therefore our work reported here focuses on performance along the power consumption saving dimension. We however ensure that we serve all the VM requests, as serving a lower number of VM requests / rejecting VM requests results in unrealistic low

power consumption and potential service level agreement violation. We also outline the improvements needed in electrical and optical switching technology to achieve the DS vision and outline further rack-clustering measures that can be introduced to help reduce latency. Performance along other known dimensions such as security, resilience and scalability, while interesting is outside the scope of this paper.

The remainder of this paper is organized as follows. Section II briefly reviews the related work. In Section III, we present our disaggregated server design. A description is presented in Section IV of the resource provisioning strategy in DS design with communication fabric. In this section, we introduce our MILP model for resource provisioning in DS, discuss its results, and propose the EERP-DSCF real-time heuristic. Section V presents a detailed evaluation of our disaggregated server design and the implementation of our proposed architectures. Finally, Section VI concludes the paper.

## II. RELATED WORK

The idea of server disaggregation became prominent when pioneers, Intel and Facebook, announced their Open Compute Project [15-17] in the 2013 Open Compute Summit. Subsequently, a series of companies, including Cisco, Tencent, Mellanox, and some research groups, dedicated extensive time and effort to developing this topic. Before the 2013 Open Compute Summit, Mellanox Technologies [18] had shown that their Infiniband switching fabric can disaggregate the IO and storage subsystem, isolating these from the main computing system. The authors in [19-22]studied the DS idea and presented the design of a new generalpurpose architectural building block, a memory blade, which allows memory to be "disaggregated" from the rest of the system ensemble. In [23] the authors discussed the ability of current data center communication networks to support the idea of disaggregation. The authors in [24] proposed a cloud architecture that disaggregates resources into virtual resource pools in order to provide virtual machines with the right amount of resources. Their cloud architecture creates a distributed and shared physical resource layer by providing a virtual layer and a cloud resource aggregation layer between applications and physical servers in real time. In [25], the authors presented Marlin, a memory-based addressing model for both I/O device sharing among multiple hosts and interhost communications. Marlin is a PCI-based rack area network system which was designed to support the communications and resource sharing between disaggregated racks. In [26], Cisco presented the Cisco Composable Infrastructure, a software-defined infrastructure (SDI) solution which allows the infrastructure to be treated as a code, disaggregating compute resources so they can easily be programmed and automatically managed. A number of companies and university research groups have, in [27], provided their vision, work, and some metrics for the disaggregated data center. The authors in [28] and [29] presented an all-optical FPGA-based optical switch and interface card (SIC) for an optical programmable disaggregated data center network. In [30], a collaboration was set up between Tencent and Intel on a proof of concept project to demonstrate that the disaggregated data center and resource pooling, even in the early stages of

development, can introduce improved performance and reduced power consumption and can enhance the end users experience. The authors in [31] studied the trade-off between cost and performance of building a disaggregated memory system; they constructed a simple cost model that compares the savings expected from a disaggregated memory system to the expected costs, such as latency and bandwidth costs, and then identified the level at which a disaggregated memory system becomes cost competitive with a traditional directattached memory system. In [32], the authors proposed a software-defined architecture for the next generation data center, dRedBox, and presented a design prototype hardware architecture where system-on-chip (SoC)-based microservers, memory modules, and accelerators are placed in separated modular server trays interconnected via a high-speed, lowlatency optoelectronic system fabric and are allocated in arbitrary sets. In [33-35], we presented a detailed description and comprehensive review of the idea of DS, with a focus on the energy efficiency benefits of this design. We presented a summary of our MILP model and heuristics for resource provisioning and VM allocation in DS-based data centers and compared the performance of the new server approach to the CS-based data center. The idea of VM migration in DS was discussed and is augmented in this work with detailed results. Our contributions in this paper beyond the conference versions [33-35] are: (i) to the best of our knowledge, we are the first to develop a MILP model for energy efficient resource provisioning and VM allocation in disaggregated resources (CPU, memory, and IO) at the hardware level; (ii) we extend our MILP model in [33-35] to account for inter-rack communication power consumption; (iii) we develop simple and efficient heuristics that converge to near optimal solutions in a shorter time when compared with the MILP model; and (iv) we introduce a detailed architecture including a communications fabric that supports and enables interaction among the disaggregated resources.

#### III. DISAGGREGATED SERVER DESIGN

In this section, we present our photonically enabled design, which uses Intel's new photonic interconnect [16]. The design shares the memory and IO modules among multiple processors to form resource pools connected through a distributed switching fabric. The concept of distributed switch functionality and modular architecture design supports very granular resource deployment approaches, which allow for greater resilience and upgradability, and scaling up a VM can be done directly and seamlessly with this modular architecture. This architecture can potentially enable repartitioning of the resources in such a way that system resources can be better shared between different compute elements.

Based on the ideas and guidelines given in [16-18] and [27], we built our modular architecture for the disaggregated server, and proposed a new interconnect topology to support the communication between the disaggregated server blocks. Given a data center system, the main communication components are inter- and intra-rack communications. Considering the inter-rack communications, the communicating units (e.g. servers or disaggregated devices) are located in different racks, while, for the intra-rack

communication, these communicating units are located within the same rack. Thus, for DS, the communication that used to be confined inside single servers is now an inter-rack traffic and traverses the whole data center communication fabric.

To show the functionality of the suggested architecture and clarify its performance, we will define each type of these communications while describing our design. Moreover, we will show how each part of the architecture will perform its assumed function in supporting these communications. The following sections detail all the distributed components, focusing on each part of the architecture and the interconnecting components.

## A. Disassembled Memory Controller (DMC)

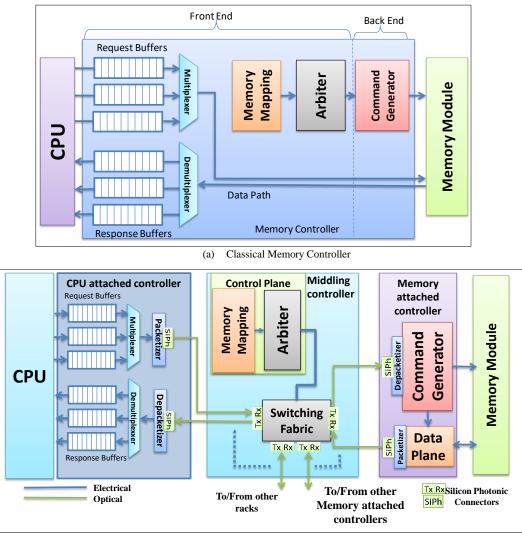

The main driving factor we consider in the DS design is that resources are to be disaggregated while maintaining the same original interfaces they connected to before disaggregation. Based on this vision and design approach, the memory controller is disassembled into functional blocks to enable its disaggregation motivated by the fact that it has been moved over time from the motherboard's north bridge to other locations such as the CPU die. In this design, we split the memory controller into three functional blocks. The first block is attached to the CPU itself, named the CPU attached memory controller (CPUMC), and the second block is general to the whole memory rack, named the middling memory controller (MMC), while the last block is attached to the memory module directly and is the memory attached memory controller (MEMC). Before we present our new Disassembled Memory Controller (DMC), we need to examine the current classical memory controller. Fig. 2.a displays the complete architecture of the current memory controller [36]. It is mainly composed of two segments, the front end and the back end. While the front end is independent of the memory module type and provides an interface to the back-end segment of the memory controller, the back end is memory type dependent. It translates requests from the front end to the target memory.

Functions such as buffering and instruction mapping and sequencing are performed in the front-end segment, which consists of buffers to store memory requests and responses. The buffers are attached to multiplexers/demultiplexers in order to send/receive one data word at a time [37]. The memory mapping decodes the memory address from the CPU address view to the memory address view (virtual memory to physical memory), and the arbiter decides the sequence in which requests from the CPU can access the memory modules. Thus, memory access requests are queued in the arbiter. The back-end command generator generates the commands for the target memory. It is memory-type dependent; thus, we will keep it attached to the memory, and it is customized to handle different timings so that different components having different clock rates can access the same memory module.

When disassembling the memory controller, we construct the three functional blocks shown in Fig. 2.b. The first block of Fig. 2.b, starting from the left, is the CPU directly attached to the CPUMC, as the CPU needs to see the same old interface. Buffers from the memory controller are attached to the CPU directly, and data is selected from these buffers in order to be sent to its destination memory rack.

Fig. 2. Memory controller.

(b) Disassembled Memory Controller

In this block, we have added a packetizer [38], after multiplexing the incoming memory access requests from the CPU. The packetizer's role is to packetize the memory controller data to be switched between the CPU rack and the memory rack. On the other hand, the depacketizer puts the responses from the memory in normal data form to be read by the CPU. The block in the middle is the MMC, where the memory mapping and the arbiter functional blocks are integrated with the top of the memory rack switch. The memory mapping and the switch arbiter form the control plane of the switch. When receiving memory access requests, in packets form, the control plane of the memory controller reads the header of the packets and, according to the ID of the destination memory module, a path is established to the intended memory module. Finally, the command generator is attached directly to the memory modules to form the MEMC, as shown in Fig 2.b. It generates commands to read from/write to the memory through the control path for control signaling and through the data path for receive and send data.

## B. Design Description

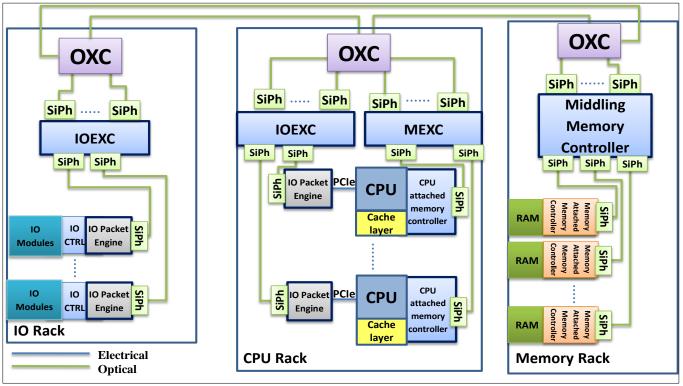

The architecture is wavelength division multiplexing (WDM) over hybrid optical and electrical switching, utilizing

components such as the optical cross connect (OXC) switch and the electronic core packet (EXC) switch, in addition to Intel Silicon Photonic (SiPh) interconnect and optical fiber links, as shown in Fig. 3. In this architecture, Intel's new SiPh interconnect, which uses light as a speedy way to shuffle data between components, is used to perform the electrical to optical transformation function and to feed each fiber link. This new SiPh interconnect is designed especially for data center applications, using new materials and manufacturing techniques to be smaller, more resilient to dust and other pollutants, more reliable, and cheaper [<u>38</u>]. Our optically enabled modular architecture is a composition of different components, and the key ones are presented in Table I.

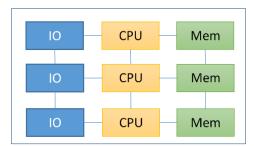

## C. Racks Interconnect Topology

We have designed a modular software-defined architecture that can replace the traditional single rack of servers with three racks: the CPU rack, memory rack, and IO rack. These racks are connected and communicate using the new communication fabric described. In this architecture, our DS design is built up by disaggregating the server into its main components, where the switching between the racks is accomplished in a distributed manner through the use of the previously

Fig. 3. DS architecture

mentioned components in Table I. Despite the fact that the single CS rack is replaced by three DS racks, power saving is still possible as the same number of resources (CPU, memory, IO, hard disks etc) are distributed (no increase in number of resources) and are utilized in an energy efficient manner in the DS racks as in [33]. In this work, DS racks consume extra power in the communication fabric, however, power saving is still possible as long as the increase in power in the communication fabric (DS communication fabric power minus CS communication power) is outweighed by the power saving due to efficient resource utilization as a result of the DS concept.

The DS design concept requires attention to the non-IT components that consume power. These non-IT components include networking, cooling and power supplies for example. The design of a custom networking architecture and subsystems for the DS has been considered in this work. The number of components to be cooled, i.e. CPUs, IO cards, and memory remain the same in the DS and CS cases (despite the fact that a single CS rack may be replaced by three DS racks). Therefore, the amount of cooling required in the data center remains the same provided custom cooling systems are introduced at the rack level instead of replicating the full server cooling system next to the CPU and replicating the full server cooling system next to (each of) memory and IO. The power supply unit has to be redesigned at the rack level instead of individual power supplies for each component (CPU, IO and memory). Such custom cooling and power supply designs for rack scale data centers are starting to appear in the industry [16]. Developments in this direction are already starting to appear in blade servers. Each server blade slides into a blade bay in a system chassis and plugs into a backplane to share common support components, such as

5

power supplies, fans, CD-ROM, Ethernet and fibre channel and system ports [<u>39</u>].

Starting with the CPU rack, in this implementation, the new photonic interconnects and fiber cables are used to connect the CPUs throughout the rack via a point-to-point to a Top of Rack electronic memory switch (MEXC). These intrarack connections are all optical, i.e. different wavelengths are used for the set of computing trays in each rack. In this design, the computing systems have been configured in trays, and each tray contains a single CPU die and its associated cache memory and control. Having large L1, L2, or even L3 caches reduces the impact of the main memory latency since the CPU can retrieve

cached data faster from its caches. The control consists of a CPUMC and PCIe interface connecting the CPU with the IO packet engine. Thus, both PCI and Ethernet networking protocols can be implemented in the same rack system, all enabled by the functionality of the MEXC and IOEXC switches, using light as the transmission medium over fiber channels.

| TABLE I                          |

|----------------------------------|

| MAIN COMPONENTS IN OUR DS DESIGN |

| MAIN COMI ONEMIS IN OUR DS DESIGN |                                           |  |

|-----------------------------------|-------------------------------------------|--|

| Optical Connectors (SiPh)         | Intel Silicon Photonic interconnects [16] |  |

| MEXC                              | Electronic switch that grooms CPU traffic |  |

| MEAC                              | to access RAM racks                       |  |

| IOXC                              | Electronic switch that grooms CPU traffic |  |

| IOAC                              | to access IO racks                        |  |

| IO Packet Engine                  | IO adapter [40]                           |  |

| IO CTRL                           | IO controller                             |  |

| OXC Switch                        | Top of Rack (ToR) optical switching units |  |

|                                   | [22]                                      |  |

| DMC Blocks                        | Disassembled memory controller blocks     |  |

Two IO packet engines are used in this design: one for each side of the CPU-IO link. This serial interface is configured to

transfer the data and address and control information required to communicate with external IO modules, such as hard disks and Ethernet ports, using a serial packetized protocol. The CPU side IO packet engine provides an interface to the CPU and supports the IO switch IOEXC on top of the CPU rack by packetizing/depacketizing the IO control/data signals to be sent to their intended destination. The IO side IO packet engine provides an interface to peripheral devices, such as IO cards, to support the support the communication between the disaggregated resources. This relies on the design idea given in [<u>18</u>], where the IO modules are disaggregated from the rest of the server box.

Due to differences between the memory and IO packet formats, two separate switches have to be implemented: one for the CPU-MEM, and the other for the CPU-IO communications. Another reason for separating the electronic switches is that the CPU-MEM communication is latency intolerant. Here, application specific switches have to be used, which are normally expensive but are high performance, in contrast to the CPU-IO traffic, which is latency tolerant, and commodity switches can be used to transfer such traffic. Furthermore, the separation of the two types of traffic reduces the load on the bottleneck MEXC and results in fast communication. These switches are very important for traffic grooming in collecting traffic from different CPU cards to optimize the number of wavelengths used in the optical layer. These switches can be programmed to assign all traffic associated with a particular CPU to a specified port. The switch is programmable in order to allow software-based implementation of the protocols used for communications at any particular port. The output from these switches is fed into an OXC switch, which is the gateway for the rack to connect it with its neighboring racks. The connecting inter-rack links, linking the OXCs, are all optical in order to achieve a high bandwidth, low latency data transmission and simplicity of wiring through the use of fewer cables/fibers, which is an essential issue for certain dense applications.

The number of output ports of each WDM OXC switch depends on the number of neighbors of the rack where the switch resides, where these outputs are connected to their neighboring OXCs. In the memory rack, starting from the top, the OXC is connected to the middling memory controller via the fibers and silicon photonic interconnects. The middling memory controller, in turn, provides a path to the selected memory module. The middling memory controller combines both the switching and the MMC functionalities.

After switching, the data is sent to the MEMC, attached to the required memory module, optically. Additionally, our design supports direct memory access (DMA), such that the memory rack can communicate with the IO rack directly without interrupting the busy CPU. This is because the memory and IO racks are interconnected through their top of rack WDM OXC switches, either by passing the OXC on top of the intermediate CPU rack in the bypass scenario or through the intermediate top of CPU rack OXC, in a nonbypass scenario.

The IO rack structure is relatively similar to the memory rack, and it is disaggregated in a similar way to what is done in [18], with the use of the IOEXC to support the OXC. All the communication links here are optical to achieve fast and

high bandwidth transmission. In this rack, the WDM OXC on the very top of the IO rack is connected to the electronic switch on top of the IO modules, IOEXC, and the IOEXC is connected optically to the different IO modules, which reside in the IO rack, through their packet engines and passing their IO controllers.

Communication integrity, control, and management are provided by a global data center operating system (GOS). This operating system is a general control layer that has an inclusive view for the whole disaggregated racks with their connectivity in order to be able to provide fluency in communication and manage the connectivity.

A hypervisor, which is a software layer that runs on top of the hardware resources and provides virtual partitioning capabilities to higher-level virtualization services, can be coupled with the GOS. The hypervisor enables the GOS to supervise and multiplex multiple operating systems in order to maintain and control every resource at all times and enable different operating systems to operate cooperatively.

CPU-to-CPU communication is managed by the top of memory rack electronic switch, MMC, and the MEXC, as communicating CPUs will interconnect through the remote memory modules, shared memory, they are using [41, 42]. CPU-MEM rack communication is performed by mutual functionality between the OXCs, DMC blocks, and the MEXC. The CPU-IO communication is facilitated by the functionality of IO packet engines on both racks to support the switching fabric implemented by the IOEXCs and the OXCs.

In brief, in the CPU rack, there are CPU trays whose traffic is aggregated using an electronic switch and is forwarded to the destined rack through optical layer switching using the OXC switch.

## IV. ENERGY EFFICIENT RESOURCE PROVISIONING IN DS Server with Communication Fabric

In the literature, a number of energy efficient inter-data center communication networks and architectures have been proposed and previously studied in [43-45]; however, data center energy management is still a hot topic for both industry and academia. We believe that implementing the DS-based data centers architecture can bring a variety of benefits, considering different prospects which include improved energy efficiency. In this section, we focus on the energy efficiency gains of resource provisioning and VM allocation in a DS-based data center. Data centers are large computing facilities which are built for applications that have very diverse resource requirements and are supposed to last for 15 to 20 years. Some applications are network intensive, such as video streaming applications, while others are latency sensitive and/or CPU intensive, such as web searching. The loads on a data center vary throughout the day and are related to our daily life events. This, in turn, creates challenges in attempting to reduce power consumption while maintaining the data center's performance. Precise resource provisioning and management directly influence overall data center energy efficiency and are of extreme importance in data center design. Under-provisioning of data center resources means that resources will be bottlenecked, while over-provisioning data center resources means a loss of power and capital. Thus,

accurate provisioning is of vital importance and motivates the efficient design of data centers. Our vision is that implementing DS to provide a solution for the problem of good resource provisioning can result in notable outcomes.

Most of the previous work in the area of resource provisioning in data centers has focused on dealing with the VM itself, such as slicing [46], queuing, and migration [47], and multiple VM multiplexing [48]. In this paper, and due to the limitations of current server design, we study the DS approach as a means of improving data center resource provisioning and resource utilization. In this sense, the main aim is an efficient data center in terms of power consumption.

In the following paragraphs, we describe the type of data center we considered and how we can account for the power consumption associated with a requested VM running in the data center. We present details of the assumptions and system configuration for the resource provisioning and VM placement using disaggregated resources. Each VM request is identified

to destination based on our novel design for the DS architecture. We present our MILP model, followed by a heuristic that mimics the MILP model behavior and expands the scope of the MILP model by providing lower complexity algorithms that enable real-time operation of the DS data center and enable the evaluation of relatively large size DS data center clusters.

A. Resource Provisioning MILP model with Communication Fabric

As explained in Fig. 1 and in Section III, each processing resource rack is served by two electrical switches, one for CPU-MEM communication and the other for CPU-IO communication; in addition, there is an optical switch on the top of the rack. The memory rack and IO rack are each served by a single electrical switch and a top of rack optical switch. All optical switches on top of the racks are connected in a semi- mesh connection. Inside each rack, the transceivers [49] shown in Fig. 3 (SiPh) support each port in each electronic switch. Each link is supported by transceivers and packetizers (packet engines for communications with IO modules) [50] at each end, one next to the source resource and one next to the destination resource. In addition, an optical Mux/Demux [51] is added after the transceivers at the link ends near the resources. As each transceiver is a 100 Gb/s in our design, and single resource traffic could exceed this 100 Gb/s, more transceivers can be used by a single resource, imposing the need to add multiplexing units. For the added functionalities of the memory mapping and arbiter to the MMC, we consider an additional 5 W to each working MMC to account for the power consumption of these units.

VMs demand resources in both the IP layer and the optical layer, in addition to the underlying DS resources. For evaluation, we define the following sets:

Sets:

NP Set of CPUs in each CPU rack

by a unique id, denoted by index i; in addition, each CPU, memory, and IO module in the data center is similarly identified by a unique id, denoted by index j. Throughout the rest of the paper, we use VM and VM requests interchangeably to refer to requested resources by a VM.

In order to optimize the VM placement in DS-based data centers, consideration has to also be given to the inter-rack communication power consumption, which is very important due to the new DS design structure. In the CS data center, resource utilization may not be as efficient as in the DS data center; however, the traffic which used to be contained within the same server or the same rack in the CS data center, now typically navigates through several racks spanning part of the data center fabric.

In this section, we highlight the main components required to establish an end-to-end connection and guarantee a fast and durable communication path from source

- NM Set of memories in each memory rack

- *NIO* Set of IOs in each IO rack

1

p

The power consumption of a data center based on the DS architecture is composed of two parts, the first is the power consumed by active resources:

The power consumption of active processors

$$\sum_{p \in PR} \sum_{j \in NP} ((XP_j^p \cdot Pmin) + (\Delta P \cdot \delta P_j^p))$$

2) The power consumption of active memories

$$\sum_{m \in MR} \sum_{j \in NM} \left( (XM_j^m \cdot Mmin) + (\Delta M \cdot \delta M_j^m) \right)$$

3) The power consumption of active IO modules

$$\sum_{io \in IOR} \sum_{j \in NIO} \left( (XIO_j^{io} \cdot IOmin) + \left( \Delta IO \cdot \delta IO_j^{io} \right) \right)$$

The second part is the power consumed by networking elements:

- 1) Power consumption due to CPU-MEM traffic, which in turn is composed of:

- a) The power consumed by the electrical switches

$$\sum_{e \in PR} PRS \cdot QPM_p + \sum_{a \in NR} \sum_{b \in N_a} PRI \cdot WPM_{a,b}$$

b) The power consumed by the optical switch

$$\sum_{a \in OPR} PO$$

2) Power consumption due to CPU-IO traffic, which is composed of:

$$\sum_{p \in PR} PRS \cdot QPIO_p + \sum_{a \in NR} \sum_{b \in N_a} PRI \cdot WPIO_{a,b}$$

b) The power consumed by the optical switch

$$\sum_{a \in MR} PO$$

3) Power consumption due to Memory-IO traffic, which consists of:

$$\sum_{m \in MR} PRS \cdot QMIO_m + \sum_{a \in NR} \sum_{b \in N_a} PRI \cdot WMIO_{a,b}$$

b) The power consumed by the optical switch

$$\sum_{a \in IOR} PO$$

The MILP model is defined as follows:

Objective: minimize:

m

io

$$\sum_{p \in PR} \sum_{j \in NP} ((XP_j^p \cdot Pmin) + (\Delta P \cdot \delta P_j^p)) + \sum_{\sum_{e \in NR}} \sum_{j \in NM} ((XM_j^m \cdot Mmin) + \Delta M \cdot \delta M_j^m)) + \sum_{\sum_{e \in IOR}} \sum_{j \in NM} ((XIO_j^{io} \cdot IOmin) + (\Delta IO \cdot \delta IO_j^{io})) + \sum_{e \in IOR} \sum_{j \in NIO} ((XIO_j^{io} \cdot IOmin) + (\Delta IO \cdot \delta IO_j^{io})) + \sum_{p \in PR} PRS \cdot QPM_p + \sum_{a \in NR} \sum_{b \in Na} PRI \cdot WPM_{a,b} + \sum_{p \in PR} PRS \cdot QPIO_p + \sum_{a \in NR} \sum_{b \in Na} PRI \cdot WPIO_{a,b} + \sum_{m \in MR} PRS \cdot QMIO_m + \sum_{a \in NR} \sum_{b \in Na} PRI \cdot WMIO_{a,b} + \sum_{a \in NR} \sum_{b \in Na} PRI \cdot WMIO_{a,b} + \sum_{a \in NR} \sum_{b \in Na} PRI \cdot WMIO_{a,b} + \sum_{a \in NR} \sum_{b \in Na} PRI \cdot WMIO_{a,b} + \sum_{a \in NR} \sum_{b \in Na} PRI \cdot WMIO_{a,b} + \sum_{a \in NR} \sum_{b \in Na} PRI \cdot WMIO_{a,b} + \sum_{a \in NR} \sum_{b \in Na} PRI \cdot WMIO_{a,b} + \sum_{a \in NR} \sum_{b \in Na} PRI \cdot WMIO_{a,b} + \sum_{a \in NR} \sum_{b \in Na} PRI \cdot WMIO_{a,b} + \sum_{a \in NR} \sum_{b \in Na} PRI \cdot WMIO_{a,b} + \sum_{a \in NR} \sum_{b \in Na} PRI \cdot WMIO_{a,b} + \sum_{a \in NR} \sum_{b \in Na} PRI \cdot WMIO_{a,b} + \sum_{a \in NR} \sum_{b \in Na} PRI \cdot WMIO_{a,b} + \sum_{a \in NR} \sum_{b \in Na} PRI \cdot WMIO_{a,b} + \sum_{a \in NR} \sum_{b \in Na} PRI \cdot WMIO_{a,b} + \sum_{a \in NR} \sum_{b \in Na} PRI \cdot WMIO_{a,b} + \sum_{a \in NR} \sum_{b \in Na} PRI \cdot WMIO_{a,b} + \sum_{a \in NR} \sum_{b \in Na} PRI \cdot WMIO_{a,b} + \sum_{a \in NR} \sum_{b \in Na} PRI \cdot WMIO_{a,b} + \sum_{a \in NR} \sum_{b \in Na} PRI \cdot WMIO_{a,b} + \sum_{a \in NR} \sum_{b \in Na} PRI \cdot WMIO_{a,b} + \sum_{a \in NR} \sum_{b \in Na} PRI \cdot WMIO_{a,b} + \sum_{a \in NR} \sum_{b \in Na} PRI \cdot WMIO_{a,b} + \sum_{a \in NR} \sum_{b \in Na} PRI \cdot WMIO_{a,b} + \sum_{a \in NR} PRI \cdot WIO_{a,b} + \sum_{a \in NR} PRI \cdot WMIO_{a,b} + \sum_{a \in NR} PRI \cdot WIO_{a,b} + \sum_{a \in NR} PR$$

Equation (1) gives the MILP model objective, which is to minimize the resource provisioning power consumption and the communication fabric power consumption, where  $XP_j^p$  is a binary indicator and  $XP_j^p = 1$  indicates that processor j in CPU rack p is active; otherwise,  $XP_j^p = 0$ .  $XM_j^m$ , and  $XIO_j^{io}$  are defined in a similar manner for the memory and IO respectively.

(1)

$\Delta P$ =Pmax-Pmin, where  $\Delta P$  is referred to as the CPU power factor (Watt), Pmax and Pmin are the CPU maximum and idle (i.e. minimum) powers respectively (Watt).  $\Delta M$  and  $\Delta IO$  are the memory and IO power factors respectively.  $\delta P_j^p$  is the total utilization of processor j in CPU rack p (unitless).  $\delta M_j^m$  and  $\delta IO_j^{io}$  are the memory and IO total utilization respectively. *PRS* and *PRI* are the electrical switch port power for the source and intermediate nodes respectively (Watt). *PRS* and *PRI* will be explained later in detail in order to show the difference between their values.  $QPM_p$  and  $QPIO_p$  are the number of aggregation ports of the MEXC and IOEXC electrical switches in CPU rack p respectively, and  $QMIO_m$  is the number of aggregation ports of the electrical switch at memory rack m.

$WPM_{a,b}$ ,  $WPIO_{a,b}$  and  $WMIO_{a,b}$  are the number of wavelengths that carry the CPU-MEM, CPU-IO and MEM-IO traffic in the physical link (a, b) respectively.

For simplicity and due to their small power consumption, we assume that the optical switches are always on. Note that NR unites all of PR, MR, and IOR, and therefore the optical switch power PO (Watts) is summed once over NR.

The minimization is subject to:

1) Resource Allocation Constraints. Capacity Constraints:

$$\delta P_j^p = \sum_{i \in VM} \theta P_{i,j}^p \leq Utl \qquad \forall j \in NP, \\ p \in PR \qquad (2)$$

$$\sum_{p \in PR} \sum_{j \in NP} \theta P_{i,j}^p = \frac{VP_i}{PRO} \qquad \forall i \in VM$$

(3)

$$\theta P_{i,j}^p \le W \cdot Y P_{i,j}^p \qquad \qquad \forall i \in VM, j \\ \in NP, p \in PR \qquad \qquad (4)$$

$$\theta P_{i,j}^{p} \ge e + Y P_{i,j}^{p} - 1 \qquad \qquad \forall i \in VM, j \\ \in NP, p \in PR \qquad (5)$$

--- -

$$\sum_{m \in MR} \sum_{j \in NM} \theta M_{i,j}^m = \frac{VM_i}{MEM} \qquad \forall i \in VM$$

(7)

$$\theta M_{i,j}^{m} \ge e + Y M_{i,j}^{m} - 1 \qquad \qquad \begin{array}{c} \forall i \in VM, j \\ \in NM, m \in MR \end{array} \tag{9}$$

$$\delta IO_{j}^{io} = \sum_{i \in VM} \theta IO_{i,j}^{io} \le Utl \qquad \forall j \in NIO, io \\ \in IOR \qquad (10)$$

$$\sum_{io \in IOR} \sum_{j \in NIO} \theta IO_{i,j}^{io} = \frac{VIO_i}{IO} \qquad \forall i \in VM \qquad (11)$$

$$\theta IO_{i,j}^{io} \le W \cdot YIO_{i,j}^{io} \qquad \forall i \in VM, j \\ \in NIO, io \in IOR \end{cases}$$

(12)

Constraint (2) calculates the total processing utilization of each processor  $\delta P_j^p$  and ensures that it is less than the maximum allowed utilization (*Utl*). Constraint (3) calculates the utilization of each processor per allocated VM,  $\theta P_{i,j}^p$ , where  $VP_i$  is the processing demand of VM *i* and *PRO* is the CPU processing capacity (GHz). Constraints (4) and (5) allocate each VM to a certain processor in a certain CPU rack by evaluating  $YP_{i,j}^p$ , which is 1 if processor j in CPU rack p hosts request *i*; otherwise,  $YP_{i,j}^p=0$ , using a very big number, *W*, and a very small number *e*, both numbers are used to help in the conversion to binary variables. Constraints (6)-(9) and (10)-(13) repeat the same steps of constraints (2)-(5), where the variables are defined in a similar manner but for the memory and IO modules respectively.

2) SLA Constraints:

$$\sum_{i \in VM} K_i \ge NVM \cdot SLA \tag{14}$$

$$K_{ip} \leq \sum_{p \in PR} \sum_{j \in NP} Y P_{i,j}^{p} \qquad \forall i \in VM \qquad (15)$$

$$W \cdot K_{ip} \geq \sum_{p \in PR} \sum_{j \in NP} Y P_{i,j}^p \quad \forall i \in VM \quad (16)$$

$$K_{im} \leq \sum_{m \in MR} \sum_{j \in NM} YM_{i,j}^m \qquad \forall i \in VM \qquad (17)$$

$$W \cdot K_{im} \geq \sum_{m \in MR} \sum_{j \in NM} Y M_{i,j}^m \quad \forall i \in VM \quad (18)$$

$$K_{iio} \leq \sum_{io \in IOR} \sum_{j \in NIO} YIO_{i,j}^{io} \qquad \forall i \in VM \qquad (19)$$

$$W \cdot K_{iio} \geq \sum_{io \in IOR} \sum_{j \in NIO} YIO_{i,j}^{io} \qquad \forall i \in VM \qquad (20)$$

$$K_i = K_{ip} = K_{im} = K_{iio} \qquad \forall i \in VM \qquad (21)$$

Constraint (14) ensures that the total number of served VMs is within an acceptable predefined percentage of the incoming VMs requests according to the service level agreement (*SLA*) value. The total number of served VMs,  $K_i$  depends on the outcomes of constraints (15)-(21) collectively; if all these constraints yield a value of 1, then  $K_i$  is 1, otherwise  $K_i$  is 0, where  $K_{ip}$ ,  $K_{im}$  and  $K_{iio}$  are binary variables indicating if the processing, memory and IO requirements of request *i* are, respectively, served or blocked.

3) Slicing Constraints:

$$\sum_{p \in PR} \sum_{j \in NP} YP_{i,j}^{p} \leq 1 \qquad \forall i \in VM \qquad (22)$$

$$\sum_{m \in MR} \sum_{j \in NM} YM_{i,j}^{m} \leq 1 \qquad \forall i \in VM \qquad (23)$$

$$\sum_{io \in IOR} \sum_{j \in NIO} YIO_{i,j}^{io} \leq 1 \qquad \forall i \in VM \qquad (24)$$

Constraint (22) ensures that a VM i processing requirement is served by only one CPU, i.e. this constraint prevents VM slicing. Constraints (23) and (24) repeat constraint (22) for the memory and IO requirements. If multiple VM copies or VM slicing is required, equations (22)-(24) should be upper bounded by an appropriate number greater than 1, however, for consistency with the CS design, we considered a scenario where each of the VM resource requirements in the DS design is also served by a single physical resource.

4) Active resources constraints:

Active processors

$$XP_j^p \le W \cdot \delta P_j^p \qquad \forall p \in PR, j \in NP$$

(25)

$$W \cdot XP_j^p \ge \delta P_j^p \qquad \forall p \in PR, j \in NP$$

(26)

Active memory modules

$$XM_j^m \le W \cdot \delta M_j^m \qquad \forall m \in MR, j \in NM$$

(27)

$$W \cdot XM_j^m \ge \delta M_j^m \qquad \forall m \in MR, j \in NM$$

(28)

Active IO modules

$$XIO_j^{io} \le W \cdot \delta IO_j^{io} \qquad \forall io \in IOR, j \in NIO$$

(29)

$$W \cdot XIO_j^{io} \ge \delta IO_j^{io} \qquad \forall io \in IOR, j \in NIO$$

(30)

Constraints (25) and (26) jointly find the active processors by checking the utilization  $\delta P_j^p$ . Constraints (27) and (28) together check the active memory modules and constraints (29), and (30) repeat the same steps but for the IO modules. 5) Communication constraints

Generating the index matrix for the CPU-MEM traffic

$$PM_{i}^{p,m} \cdot 2 = \sum_{j \in NP} YP_{i,j}^{p} + \sum_{j \in NM} YM_{i,j}^{m}$$

$$\forall i \in VM, p \in PR, m \in MR$$

$$(31)$$

$$ZPM_{i}^{p,m} \leq PM_{i}^{p,m} \qquad \begin{array}{c} \forall i \in VM, \ p \in PR, \\ m \in MR \end{array}$$

(32)

$$ZPM_i^{p,m} \ge PM_i^{p,m} - 0.5 \qquad \begin{array}{c} \forall i \in VM, \ p \in PR, \\ m \in MR \end{array}$$

(33)

Generating the index matrix for the CPU-IO traffic

$$PIO_{i}^{p,io} \cdot 2 = \sum_{j \in NP} YP_{i,j}^{p} + \sum_{j \in Nio} YIO_{i,j}^{io}$$

$$\forall i \in VM, p \in PR, io \in IOR$$

$$(34)$$

$$\forall i \in VM, p \in IK, to \in IOK$$

$\forall i \in VM.$

$$ZPIO_{i}^{p,io} \leq PIO_{i}^{p,io} \qquad p \in PR, \qquad (35)$$

$$io \in IOR$$

$$\forall i \in VM,$$

$\forall i \in VM$

$$ZPIO_i^{p,io} \ge PIO_i^{p,io} - 0.5 \qquad \begin{array}{c} p \in PR, \\ io \in IOR \end{array}$$

(36)

Generating the index matrix for the Memory-IO traffic

$$MIO_i^{m,io} \cdot 2 = \sum_{j \in NP} YM_{i,j}^m + \sum_{j \in NIO} YIO_{i,j}^{io}$$

(37)

$\forall i \in VM, m \in MR, io \in IOR$

$$ZMIO_{i}^{m,io} \leq MIO_{i}^{m,io} \qquad m \in MR, \qquad (38)$$

$$io \in IOR$$

Constraint (31) connects each source CPU rack to its destination memory rack.  $PM_i^{p,m}$  is an integer indicator that connects the *i*<sup>th</sup> VM CPU-MEM traffic to the relevant CPU and MEM racks. Constraints (32) and (33) collectively generate source-destination index matrix,  $ZPM_i^{p,m}$  for all CPU-MEM traffic, depending on constraint (31).  $ZPM_i^{p,m} = 1$  if the VM *i* generates traffic between CPU rack *p* and MEM rack *m*; otherwise,  $ZPM_i^{p,m} = 0$ . Constraints (34)-(36) and constraints (37)-(39) repeat the same steps of (31)-(33), where the variables are defined in a similar manner but for the CPU-IO traffic and Memory–IO traffic, respectively.

Generating the traffic demand matrix:

$$TPM_{p,m} = \sum_{i \in VM} VPM_i \cdot ZPM_i^{p,m} \qquad \forall p \in PR, \\ m \in MR \qquad (40)$$

$$TPIO_{p,io} = \sum_{i \in VM} VPIO_i \cdot ZPIO_i^{p,io} \qquad \forall p \in PR, \\ io \in IOR \qquad (41)$$

$$TMIO_{m,io} = \sum_{i \in VM} VMIO_i \qquad \forall m \in MR, \\ io \in IOR \qquad (42)$$

Constraint (40) generates the CPU-MEM traffic matrix  $TPM_{p,m}$  based on the index matrix  $ZPM_i^{p,m}$  calculated previously in constraints (32) and (33), and  $VPM_i$ , which is the  $i^{th}$  VM CPU-MEM traffic demands. Constraints (41) and (42) generate the CPU-IO and Memory-IO traffic matrices respectively, using the relevant variables.

Traffic flow conservation:

$$\sum_{b \in N_{a}} WPM_{a,b}^{p,m} - \sum_{b \in N_{a}} WPM_{b,a}^{p,m}$$

$$= \begin{cases} (TPM_{p,m} / B) & a = p \\ -(TPM_{p,m} / B) & a = m \\ 0 & otherwise \end{cases}$$

$$\forall p \in PR, m \in MR, s \in NR$$

$$\sum_{b \in N_{a}} WPIO_{a,b}^{p,io} - \sum_{b \in N_{a}} WPIO_{b,a}^{p,io}$$

$$= \begin{cases} (TPIO_{p,io} / B) & a = p \\ -(TPIO_{p,io} / B) & a = io \\ 0 & otherwise \end{cases}$$

$$\forall p \in PR, io \in IOR, s \in NR$$

$$\sum_{b \in N_{a}} WMIO_{a,b}^{m,io} - \sum_{b \in N_{a}} WMIO_{b,a}^{m,io}$$

$$= \begin{cases} (TMIO_{m,io} / B) & a = m \\ -(TMIO_{m,io} / B) & a = io \\ 0 & otherwise \end{cases}$$

$$\forall m \in MR, io \in IOR, s \in NR$$

$$(45)$$

Constraints (43)-(45) are the flow conservation constraints for the CPU-MEM, CPU-IO, and Memory-IO traffic respectively in the networking elements switches, ensuring that the total incoming traffic is equal to the total outgoing traffic for all nodes except for the source and destination racks, where  $WPM_{a,b}^{p,m}$ ,  $WPM_{a,b}^{p,io}$  and  $WPM_{a,b}^{m,io}$  are the number of wavelengths of lightpath (p,m), (p,io), and (m,io) respectively passing through a physical link (a,b).

Wavelengths capacity constraints:

$$\sum_{p \in PR} \sum_{io \in IOR} WPIO_{a,b}^{p,io} \le WPIO_{ab} \qquad \stackrel{\forall a}{\in} PR, b \\ \in Na \qquad (47)$$

$$\sum_{m \in MR} \sum_{io \in IOR} WMIO_{a,b}^{m,io} \le WMIO_{ab} \qquad \stackrel{\forall a}{\underset{\in Na}{\leftarrow} MR,b}$$

(48)

Constraints (46)-(48) ensure that the summation of the number of wavelengths traversing a physical link in the optical layer does not exceed the total number of wavelengths in that link for the CPU-MEM, CPU-IO, and Memory-IO traffics respectively.

$$QPM_{p} = \frac{1}{B} \cdot \sum_{m \in MR} TPM_{p,m} \qquad \forall p \in PR \qquad (49)$$

$$QPIO_{p} = \frac{1}{R} \cdot \sum_{m \in MR} TPIO_{p,io} \qquad \forall p \in PR \qquad (50)$$

$$QMIO_{m} = \frac{1}{B} \cdot \sum_{io \in IOR} TMIO_{m,io} \qquad \forall m \in MR$$

(51)

Constraints (49)-(51) determine the total number of aggregation ports utilized by the CPU-MEM, CPU-IO, and Memory-IO traffics respectively in each rack by dividing the total traffic matrix by the wavelength rate B (Gbps).

#### B. Resource Provisioning in CS with Communication Power MILP Model

Here, we assume that both the CS and DS use the same data center networking topology, such as fat tree or spine and leaf. Therefore, the power consumption of this fabric is not included in both CS and DS designs, but we include the communication fabric needed to realize the DS functionality as shown in Fig. 3. Note that such topologies might not be an optimal choice for the DS data center, and a specially designed communication fabric on top of the communication layer shown in Fig. 3 may be needed to form an optimal higher networking architecture layer for the DS data center interconnect topology; this is an issue for future research.

In the CS MILP model we consider a pool of servers, rather than a pool of resources. Each CS is equipped with the same type of resources (CPU, memory, I/O) that are used in the DS. Furthermore, we assume that each CS has a single CPU associated with a single Memory and a single IO module. Therefore, the utilization of a certain resource in the CS will affect the utilization of the other two resources. For example CPU#1 is associated with memory#1 and IO module#1 in CS#1. If CPU#1 is fully utilized by VM#1 then memory#1 and IO module#1 cannot be used by another VM even if they have enough capacity for the second VM. This is to be compared to the DS design. Thus, the number of servers in CS design is the same as the number of one type of resources, such as the number of CPU resources, and here we have 24 servers.

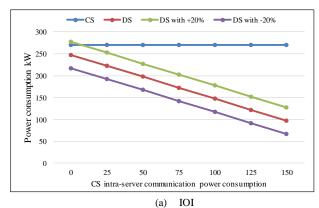

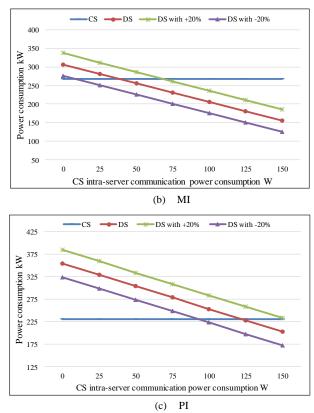

To account for the server power, we consider a fully loaded server power of 300 Watts [52]. The power consumption of each resource (e.g. CPU, memory, IO card) in this server was comparable to the values used in the DS. Given that all the traffic is contained within the same server, and we assume that VMs are not sliced among different servers and VMs do not interact with each other, we are not using switches for interserver traffic with the CS design. Viewed differently, we essentially do not include the data centre communication fabric (eg. fat tree or spine and leaf) when comparing the CS and DS as the same fabric is considered in both cases and carries the same inter-server traffic, (although the DS can potentially benefit from an alternate custom higher layers architecture fabric as mentioned). Instead we account for the intra-server communication in the CS as follows: the power consumption of each resource was set exactly equal to the values used in DS to facilitate comparison, and the CS idle power consumption is considered to be 150W which is about 50% of its maximum power consumption [53][72], to account for the intra-server communication power. Later in the paper we revisit this idle power and consider the situation where only a fraction of it contributes to the intra-server communication power while the remaining noncommunication power is distributed among other parts of the CS, e.g. non-IT components, hard disks, etc. Such noncommunication power consumption has to be added to the DS design to accurately assess its power savings compared to the CS design.

For the CS approach, each VM is allocated to the server that has enough CPU, memory, and IO modules to accommodate the VM; otherwise, a new server is powered on to host the requesting VM.

In addition to the parameters and variables defined in Section

IV-A, we define the following:

Sets:

١

| 50.65.           |                                                                                  |

|------------------|----------------------------------------------------------------------------------|

| NS               | Set of all servers                                                               |

| VM               | Set of VMs to be served                                                          |

| Variables:       |                                                                                  |

| $\delta P_j$     | Total processor utilization of server <i>j</i>                                   |

| $\delta M_j$     | Total memory utilization of server <i>j</i>                                      |

| $\delta IO_i$    | Total IO utilization of server <i>j</i>                                          |

| $X_j$            | Indicates if server <i>j</i> is active, $X_j = 1$ ; otherwise, $X_j = 0$         |

| $\theta P_{ij}$  | Portion of the processing capacity of server $j$ allocated to request $i$        |

| $\theta M_{ij}$  | Portion of the memory capacity of server $j$ allocated to request $i$            |

| $\theta IO_{ij}$ | Portion of the IO capacity of server $j$ allocated to request $i$                |

| $Y_{ij}$         | $Y_{ij} = 1$ if server <i>j</i> hosts request <i>i</i> , otherwise, $Y_{ij} = 0$ |

|                  |                                                                                  |

*NOS* Number of working servers

The resource provisioning in the CS-based data center MILP model is:

Objective: minimize:

$$\sum_{j \in NS} ((X_j \cdot Pmin) + (\Delta P \cdot \delta P_j)) + \sum_{j \in NS} ((X_j \cdot Mmin) + (\Delta M \cdot \delta M_j)) + \sum_{j \in NS} ((X_j \cdot IOmin) + (\Delta IO \cdot \delta IO_j)) + NOS \cdot 150$$

(52)

The objective (52) aims to minimize the total power by consolidating VMs in the minimum number of working servers.

Capacity Constraints:

$$\begin{split} \delta P_{j} &= \sum_{i \in VM} \theta P_{ij} \leq Utl & \forall j \in NS \quad (53) \\ P_{j} \cdot \theta P_{ij} &= VP_{i} \cdot Y_{ij} & \forall i \in VM, j \\ \theta P_{ij} \leq W \cdot Y_{ij} & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ \in NS & \forall i \in VM, j \\ i \in VM, j \\ \in NS & \forall i \in VK & \forall i \in VK \\ \in NS & \forall i \in VK & \forall i \in VK \\ \in NS & \forall i \in VK & \forall i \in VK \\ \in NS & \forall i \in VK \\ i \in VK & \forall i \in VK \\ i \in VK \\ i \in VK & \forall i \in VK \\ i \in$$

$$M_{j} \cdot \theta M_{ij} = V M_{i} \cdot Y_{ij} \qquad \forall i \in V M, j \quad (58)$$

$$\theta M_{ij} \le W \cdot Y_{ij} \qquad \qquad \begin{array}{c} \forall i \in VM, j \\ \in NS \\ \forall i \in VM, j \\ \in NS \end{array} \tag{59}$$

$$\delta IO_j = \sum_{i \in VM} \theta IO_{ij} \le Utl \qquad \forall j \in NS$$

(61)

$$IO_{j} \cdot \theta IO_{ij} = VIO_{i} \cdot Y_{ij} \qquad \begin{array}{c} \forall i \in VM, j \\ \in NS \end{array}$$

(62)

$$\theta IO_{ij} \ge e + Y_{ij} - 1 \qquad \qquad \begin{array}{c} \forall i \in VM, j \\ \in NS \end{array} \tag{64}$$

Constraint (53) calculates the total processing utilization of each processor in each server and ensures that it is less than the maximum allowed utilization. Constraint (54) calculates the utilization of each processor per allocated VM, and constraints (55) and (56) allocate each VM to a certain processor in a certain server. Constraints (57)-(60) and (61)-(64) repeat the same steps of constraints (53)-(56) but for the memory and IO modules respectively.

Slicing Constraint:

$$\sum_{j \in NS} Y_{ij} = 1 \qquad \qquad \forall i \in VM \qquad (65)$$

Constraint (65) ensures that each VM will be served by one server. This constraint will force service quality equal to 100% SLA.

Active Resources Constraint:

$$X_j \le W \cdot \delta P_j \qquad \forall j \in NS \qquad (66)$$

$$W \cdot X_j \ge \delta P_j \qquad \forall j \in NS \qquad (67)$$

$$NOS = \sum_{j \in NS} X_j \tag{68}$$

Constraints (66) and (67) find the working servers and constraint (68) uses their results to calculate the total number of working servers.

C. Energy Efficient Resource Provisioning in Disaggregated Servers with Communication Fabric (EERP-DSCF) Heuristic

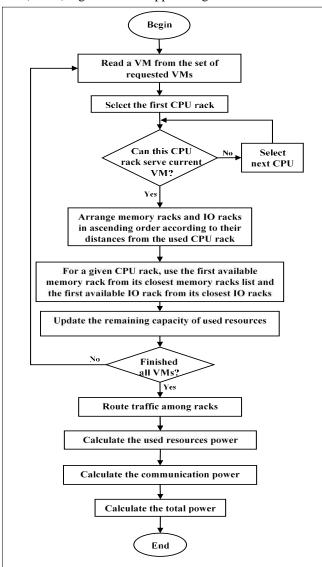

The EERP-DSCF heuristic provides real-time implementation of the MILP model in Section IV-A. The flow chart of the heuristic is shown in Fig. 4. In this study, we use homogenous resources, and thus sorting resources according to their PF is not necessary. Therefore, the heuristic picks the first CPU from the first CPU rack in the cluster and uses it for serving the first VM request. Then, the heuristic decides the VM's memory and IO racks allocation based on joint criteria involving the resource availability and rack distance from the chosen CPU rack. Thus, both packing and open shortest path first (OSPF) algorithms are applied together.

Fig. 4. EERP-DSCF heuristic flow chart.

As shown in the flow chart, Fig. 4, the heuristic follows a greedy approach to pack as many VMs as possible in the minimum number of resources and such resources may be physically far apart. Therefore, SLA violations might occur in the form of increased delay. However, delay constraints can be included by forming clusters of DS racks within a maximum distance limit between the selected racks in each cluster which should be set in consistency with the OSA metrics for server disaggregation.

The EERP-DSCF picks the first VM and allocates the first CPU in the first CPU rack in the cluster. The heuristic then organizes the memory and IO racks in a list according to their distances from the chosen CPU rack in ascending order. Subsequently, the heuristic checks the resources availability in the newly organized lists. If the first memory rack has enough capacity to accommodate the VM under consideration, the heuristic uses it; otherwise, the next rack is tested. In the same fashion, the heuristic checks the first IO rack in the list and allocates the chosen resources for the VM under consideration; otherwise, the next nearest IO rack is tested, and so on, until an available IO module is found. The heuristic tries to fill partially used resources and racks as much as possible before moving onto next racks. After allocating resources to the first VM request, the heuristic loops for the rest of the VM requests until all VMs allocations are done. Finally, EERP-DSCF grooms the traffic from each rack according to the traffic destination, routes them among racks, and calculates the total consumed power.

#### D. Evaluation Scenarios for the MILP Model and Heuristic

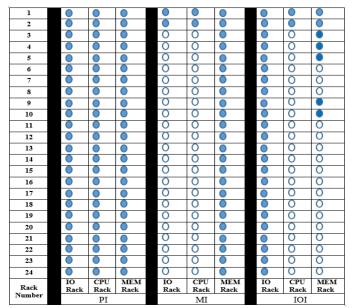

To evaluate the performance of the proposed MILP model and heuristic, we consider the example data center shown in Fig. 5. It consists of 72 racks (24 racks of each resource type), organized in an  $8\times9$  matrix and 127 links, as shown in Fig. 5, which represents the top view of the DS data center considered.

Fig. 5. DS based data center structure under consideration.

For the MILP model, a smaller version of the data center cluster, shown in Fig. 5, is used due to MILP computational complexity. It comprises 9 racks (3 racks of each resource type) organized in a  $3\times3$  matrix and 12 links, as shown in Fig. 6. It follows the same structure and racks sequencing of the data center cluster in Fig. 5. The first column consists of three

IO racks, the second consists of three CPU racks, and the last column consists of three memory racks. We consider a scenario in which each rack contains 8 resources of its own type, each CPU rack contains 8 processors, each IO rack contains 8 IO modules, and each memory rack contains 8 memory modules. Thus every three racks, (one of each type, i.e. one processing, one memory and one IO racks) will contribute to make 8 servers. Therefore, in 3×3 racks there are 24 servers in total (8  $\times$  3). Thus with a load of 25 VMs, assuming 1 VM per server, the maximum load of the DC is 100%.

For the heuristic, and due to its lower computational complexity, we evaluated the full 8×9 data center shown in Fig. 5. Each column is one type of resource racks, and each rack of each type contains 42 resources of its type. Starting from the far left, the first column contains the IO racks, followed by the CPU racks, then the Memory racks, and this sequence is repeated for the next 6 columns. Note that each rack is only connected to the nearest neighboring racks using optical fibers. As for the heuristic, the distance between adjacent racks is set to 1m [54].

For both the MILP model and the heuristic, each rack has its own intra-rack communication fabric and electrical and optical switches to facilitate the communication among racks and inter-rack communication, as shown in Fig. 1 and in Fig. 3. Table II shows the parameters used for both the MILP model and heuristic. The power consumption of the resources we used is consistent with our previous work in [33, 34], and, for the network devices, we use the values in Table II.

Regarding some of the power values given in Table II, it is worth noting that for the electrical switch port power and the packetizer power, we have linearly scaled up the values given in [55] for the switch port and [50] for the channel adapter to account for 100 Gbps port power. For the switch port power, and according to [55], a 10 Gbps port consumes 4 W; therefore, the switch port power consumption is calculated as 4×10W (equivalent to 100 Gbps port). For the 100 Gbps packetizer, in [50], the 40 Gbps packetizer power consumption is 7 W, and thus to scale up for 100 Gbps, the total power consumption is calculated as 7×2.5=17.5 W, and, to be more conservative, an extra 2.5 W was added, i.e. 20 Watts in total in order to account for other possible functionalities, such as buffering and arbitration.

| TABLE II                                             |                       |

|------------------------------------------------------|-----------------------|

| INPUT PARAMETERS FOR THE MILP MODEL AND SIMULA       | TION HEURISTIC        |

| Power consumption of electrical switch port for      | 70.5 W                |

| source nodes PRS                                     |                       |

| Power consumption of electrical switch port for      | 43.5 W                |

| intermediate nodes PRI                               |                       |

| Power consumption of electrical 100 Gbps switch      | 40 W [55]             |

| port (Pr)                                            |                       |

| Power consumption of an optical switch               | 85 W [56]             |

| Bit rate of each wavelength                          | 100 Gbps              |

| CPU capacity                                         | 3.6 GHz [ <u>57</u> ] |

| CPU maximum power consumption                        | 130 W [ <u>57</u> ]   |

| RAM capacity                                         | 8 GB [ <u>57</u> ]    |

| Memory maximum power draw                            | 10.24 W [ <u>58</u> ] |

| IO module rate                                       | 10 Gbps [ <u>57</u> ] |

| IO module maximum power draw                         | 21.4 W [ <u>59</u> ]  |

| 100 Gbps Optical transceiver power                   | 3.5 W [ <u>49</u> ]   |

| 100 Gbps Multiplexer power (W)                       | 4 W [ <u>51</u> ]     |

| 100 Gbps Packet engine (packetizer or packet engine) | 20 W [ <u>50</u> ]    |

| power                                                |                       |

$$PRS = 40 W (electrical switch port) + 3 \times 3.5 W (transceivers power) + 20 W (packetizer power)$$

Here, we consider 3 transceivers: the first is attached to the source resource, the second is for the destination resource, and the third is for the source electrical switch port.

For each intermediate node, we consider a switch port power plus a transceiver power, which yields:

> PRI = 40 W(electrical switch port) + 3.5 W (transceiver power)

Fig. 6. Substrate data center for the MILP model.

#### E. VM Modeling

For the VM resources requirements and traffic demands, we use the requirements in Table III, which are assumed with respect to the three different VM types: processing intensive (PI), memory intensive (MI), and IO intensive (IOI). These three VM types are different in terms of their resources requirements, as shown in Table III. VMs are assumed to arrive at the same time, but we have not considered blocking because blocking can reduce power consumption, and we consider a situation where both CS and DS can accommodate all VM requests without blocking or migration to establish a comparison that is based solely on the difference in architecture and resource management between the two approaches. However, we note that VM blocking and different VM arrival patterns are interesting topics, and we leave their investigation for future research. Comparing the IO resources requirements to the actual traffic reveals that delay or maybe blocking situations can occur on the egress ports. However, we have not considered their effects in the analysis presented in this work.

A VM requires three resources: processing, memory and networking resources, and there is traffic between these resources. As mentioned above, we assume that all the VM requests arrive at once and they all have infinite service durations. Thus, it is a one shot (non-sequential) evaluation, such that a VM will use the same allocated resources at all times and will not be migrated to different resources. We assume all VMs are served as we set the SLA to 100% and as such no VM blocking is considered. We did not consider blocking VM requests since such blocking can lead to lower power consumption in one of the designs. Therefore we require both the CS and DS to serve all the requests.

Using a computer with a 3.3 GHz CPU and 8 GB memory, our heuristic produced the results in less than one minute, considering 1000 IOI VMs. This is a remarkable improvement over the MILP model, which requires about 2 days to produce the results for only 20 IOI VMs using the same computer. While our heuristic results show the power consumption of a range of data center loads ranging from 100 to 1000 VMs, the MILP model shows results for data center loads ranging from 5 to 20 VMs, limited by the computational complexity of the MILP and the processing platform available.

| IN UTTAKAMETEKS.       |         |         |         |

|------------------------|---------|---------|---------|

| VM Type<br>Demands     | PI      | MI      | ΙΟΙ     |

| CPU (GHz)              | 2-3.6   | 0.1-0.3 | 0.1-0.3 |

| Mem (GB)               | 0.1-0.3 | 6-8     | 1-4     |

| IO (Gbps)              | 0.5-1   | 0.5-1   | 6-10    |

| CPU-MEM Traffic (Gbps) | 10-100  | 10-50   | 5-20    |

| CPU-IO Traffic (Gbps)  | 1-3     | 1-3     | 1-3     |

| MEM-IO Traffic (Gbps)  | 1-3     | 1-5     | 6-10    |

TABLE III INPUT PARAMETERS FOR THE VMS REOUIREMENTS

F. MILP Model and Heuristic Results

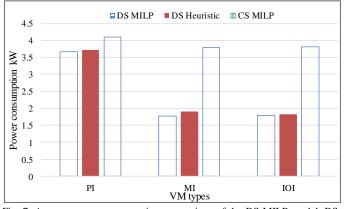

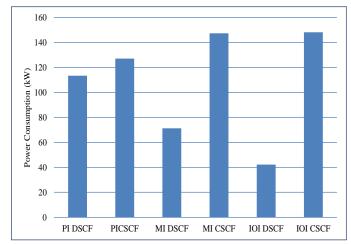

Fig.7 compares the average power consumption results of the MILP model for the DS and CS designs and the DS heuristic considering the three VM types PI, MI and IOI. The results were obtained by running the MILP models and the heuristic for the cases of 5, 10, 15, 20 and 25 VM requests, then the average power consumption is calculated. The results show clearly that the DS heuristic and the DS MILP are comparable and the heuristic follows the MILP closely

Fig. 7. Average power consumption comparison of the DS MILP model, DS heuristic, and CS MILP model with communication fabric.

Examining the results in Fig. 7 and comparing the DS MILP to the CS MILP shows that the PI VMs are the highest power consuming demands which leads to minimum average power saving, of about 3% while MI and IOI have comparable power consumptions and they have comparable average power savings, of about 42%.

Fig. 7 shows that the heuristic and MILP are close and the heuristic execution time is short. Therefore, we have obtained new results where for each VM the CPU load was random and uniform between 0.1 and 3.6 GHz, the other VM attributes were also random and uniform and were: Mem (1-8) GB, IO (0.5-10) Gbps, CPU-Mem traffic (10-100) Gbps, CPU-IO traffic (1-3) Gbps, Mem-IO traffic (1-10) Gbps.

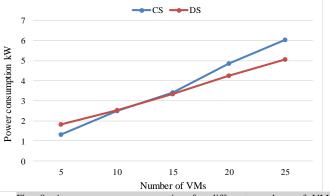

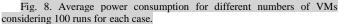

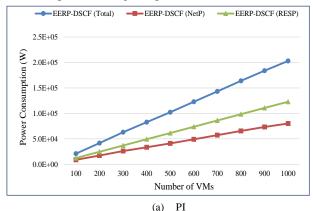

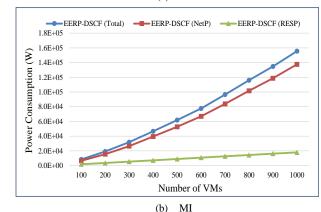

The power savings are averaged over 100 experiments (each experiment obtained power saving using 100 runs of the CS and DS heuristics for 5, 10, 15, 20, and 25 VMs) and the power profiles are shown in Fig. 8. With the considered high demand values, the DS power consumption is more than the CS for very small numbers of VMs, but moving to large numbers of VMs, the DS shows better performance compared to CS due to good resource packing.

The placement of VMs is optimized by the CS and the DS heuristics so as to minimize the power consumption through packing and proximity placement as shown in Fig. 4.

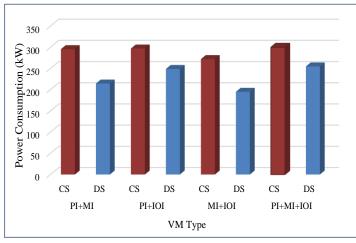

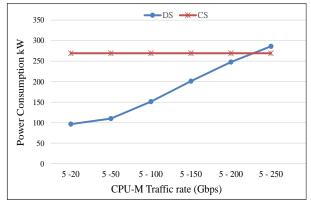

Fig. 9 shows the DS heuristic results for the power consumption of the networking resources (NetP), the resource power consumption (RESP), and the total power consumption (Total). The results can be explained by considering the cluster topology and size under consideration plus the number of served VMs, as well as the inputs, in particular, the resource specifications, and VM requirements.

Fig. 9.a shows the PI VM requests results. Note that the resource power is higher than the networking power, and it has higher impact on the total power consumption. Given the parameters in Tables II and III for the resources, power consumption, and VM demand values, the average CPU demand per VM is 3 GHz for the PI VMs type, and thus a huge number of CPUs will be used for VM allocation. A lot of VMs will occupy a whole CPU on their own and not share the CPU with other VMs. Given that the CPU has high power consumption values, the resource power consumption is the highest and exceeds the network power consumption.

In relation to the networking power, Fig. 10 shows the active racks of each type when serving 1000 VM requests for the three VM types, PI, MI, and IOI. Examining Fig. 10 reveals that considering 1000 PI VM requests results in a case where all the racks in the cluster are activated, regardless of their utilization, where an active rack means there is an outgoing/incoming traffic. Each CPU rack has an active memory and IO racks among its neighbors, enforced by the heuristic, and thus all traffic, in this case, will be a single hop traffic resulting in about 80 kW networking power consumption, which is less than the power consumed by the resources.

Fig. 9.b shows the evaluation for the MI VM requests and compares the two power components: the network and resource powers. As in PI, both the network power and resource power consumption increase with increasing number